周立功教授新书《面向AMetal框架与接口的编程(上)》,对AMetal框架进行了详细介绍,通过阅读这本书,你可以学到高度复用的软件设计原则和面向接口编程的开发思想,聚焦自己的“核心域”,改变自己的编程思维,实现企业和个人的共同进步。经周立功教授授权,即日起,致远电子公众号将对该书内容进行连载,愿共勉之。

第二章为ADC 信号调理电路设计,本文为 2.3 必要措施、2.4 实测验证和2.5 应用说明。

2.3 必要措施

一个完整的采集电路框图详见图2.19,从传感器或信号源到最终的ADC 数据输出,中间需要经过输入范围调整、多通道复用等信号调理环节。除ADC 自身之外,需要考虑整个采集通道链路的设计,才能获得的良好采集精度。

图2.19 典型的采集电路框图

在设计采集通道时,需要考虑的问题有:

-

信号的大小和ADC 满量程输入的范围。

-

信号的极性和ADC 输入的极性。

-

信号的通道数,是否需要多通道同步采样,还是采用复用输入?

-

信号是单端输入,还是差分输入?

>>> 2.3.1 输入范围匹配

传感器信号往往都很微弱,幅度可能只占ADC 量程的一小部分。使得最大输入信号的幅度与ADC 量程相匹配,对于得到最大的ADC 转换精度是重要的。假定要转换的信号在0V 至2V 之间变化,而VREF 等于3V,则最大信号的ADC 转换数值是2729(2.0V),详见图2.20。这样,就有1366 个未使用的转换数值,即丢失了转换信号的精度。

图2.20 输入信号幅度与ADC 测量范围

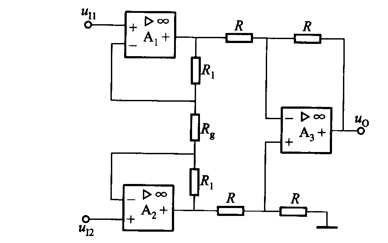

最好使用一个外部的前级放大器,这个放大器可以把输入信号的范围转换至ADC 模块的范围。例如使用LMV358A 搭建10 倍同相放大器,使得0~300mV输入信号,转换到0~3V。

同样可以使用外部的放大器搭建叠加电路,完成双极性正负输入,转换成单极性输入;搭建仪表放大器,完成差分输入转换成单端输入。

>>> 2.3.2 多通道采样设置

考虑硬件成本时,多个采集通道复用一个ADC 是常用的做法。LPC82x 具有12 路模拟输入管脚,芯片内部已经是多路复用结构,详见图2.21。

图2.21 LPC82x 模拟输入通道的多路复用等效电路

使用这种时分复用结构时,非常容易由以下两个问题导致精度下降:

-

通道的信号源阻抗过大导致建立时间不足,采集到的电压值减小。

-

通道切换时间过快,多路开关公共端的寄生电容,导致相邻通道上的信号出现串扰。

虽然信号源阻抗的影响已经设计了缓冲运放彻底解决,但是考虑到成本因素,每个通道都加入一个运放有时无法接受,更合理的配置是幅值精度要求高的信号通道上使用运放,要求不高的通道上信号源直接输入ADC 通道。

这种混合配置需考虑两种情况:直接输入通道为高速信号并且要求高带宽,或者为低速信号并且要求限制带宽。当直接输入通道为高速信号的参考电路详见图2.22,为了避免通道串扰导致的电压残留,通道上不能并接电容,设计关键在于信号源阻抗与采样速率相匹配。

图2.22 直接输入通道为高速信号时的多通道采样电路

要根据采样速率,对直接输入通道信号源阻抗的极限值进行量化。为了方便计算,取多路复用结构中的单个LPC82x 模拟输入通道,等效电路详见图2.23。

图2.23 LPC82x 单个模拟输入通道的等效电路

从左至右来看,RS 为外部信号源阻抗,CPIN 是输入引脚电容(基本可忽略),RSWITCH为多路复用开关电阻+采样开关导通电阻,CSAMPLE 为采样电容。采样期间开关闭合,RS、RSWITCH、CSAMPLE 构成单极点RC 网络,它的时间常数可以表示为:

假设在采样刚开始时,采样电容上电压为0,电容上电压与上升时间的关系可以表示为:

由此可见,可以根据变化时间确定采样电容上的电压达到输入信号电压值的百分比。假设RS 为0,当采样电容上的电压为输入电压值的99.32%时,将有0.68%(剩余百分比)的电压无法准确获得,也就是说最小分辨率为0.68%,这和7.2 位的ADC 的分辨率一致。剩余百分比和ADC 位数的换算公式为log2(1/剩余百分比)log2(1/剩余百分比),其典型换算结果详见表2.4。

表2.4 建立时间与ADC 精度

根据这个表的计算,如果不能给ADC 足够的采样时间会导致ADC 的精度降低。假设一个采样速率为1Msps 的12 位ADC,有效的采样时间为750ns。当RS为0 时,750ns>200ns,采样电容上能获得远高于12 位的精度,采样时间是足够的。如果现在对信号源增加5KΩ内阻,然后可以得到:如果要达到13bits 精度,ADC 至少需要1350ns 的采样时间:

750ns 的采样时间就已经不够了。这时,可以通过改变软件来降低ADC 的采样率来获得更长的采样时间。而判断是否应该降低采样速率,以LPC82x 最高采样速率1Msps 情况下,所允许的最高源阻抗为参考值。考虑信号建立至1/2LSB,计算过程如下:

该极限值表示,使用图2.22 的直接输入通道为高速信号的多通道采样电路,最高信号源阻抗不能超过2kΩ,否则需要降低采样速率。

当直接输入通道为低速信号的参考电路详见图2.24,对源阻抗无要求,但通道两侧的相邻输入通道需要接地。总结多通道采样设置方法详见表2.5,高速信号是指需要进行波形采样的信号,比如采集电网波形。低速信号是指只关注直流分量的信号,比如电源电压、温传感器的输出电压。

图2.24 直接输入通道为低速信号时的多通道采样电路

表2.5 多通道采样电路的选择方法

>>> 2.3.3 电源分配策略

电源噪声是电路板上重要的噪声源头。为了减少干扰,建议模拟和数字部分独立使用稳压器供电,详见图2.25。

图2.25 模拟部分与数字部分独立供电

>>> 2.3.4 PCB 布局布线处理

数字信号的开关噪声是电路板上另外一大干扰源。避免干扰电路板上的数字电路干扰模拟电路,应该遵循下面的规则:

-

模拟部分器件与数字部分器件,分区域放置,避免交叉放置,详见图2.26。

图2.26 模拟器件与数字器件分区域放置

-

分割地平面,然后使模拟地平面与数字地平面在单点连接,避免通过公共的地回路引入干扰,详见图2.27。

图2.27 分割地平面在单点连接

-

模拟走线与数字走线,避免靠近平行走线,如果不能避免,加地线屏蔽模拟走线,详见图2.28。

图2.28 避免数字走线干扰模拟走线

2.4 实测验证

为验证改善方法的有效性,特制作了实际的电路板。测试LPC824 内部ADC 的关键精度指标,并且与成品开发板AM824 的测试数据进行对比。主要测试数据为无噪声分辨率、INL、失调误差、增益误差。

>>> 2.4.1 无噪声分辨率

无噪声分辨率定义为ADC 电路测量一个无噪声的稳定直流电压源,统计多次连续采样数据,输出数字代码能够保持不跳动的位数。无噪声电压源使用干电池,理想情况下,输出代码不跳动,只有一个输出代码。

在原AM824 开发板上,重复测试一块干电池200 次,获得的数据直方图详见图2.29。

图2.29 AM824 开发板测试直流信号的代码分布

在使用了本文改善措施的电路板上,重复测试同一块干电池200 次,获得的数据直方图详见图2.30。

图2.30 标准化电路板测试直流信号的代码分布

经过对比,发现原数据跳动在6 位数码,转换成分辨率为3 位,就是说如果使用原开发板,最多可以发挥9 位分辨率的精度。但是在新的电路板上,我们看到数据相对集中而且跳动仅仅在3 位,测量的精度更高,可以使用10 位的分辨率精度。

>>> 2.4.2 积分非线性(INL)

INL 是表征ADC 精度的一个重要参数。在ADC 的全量程范围内,设置输入电压值从小至到大,依次等间距采集一系列数据点,可以线性拟合出一条最贴近这些数据点的直线。理想情况下,ADC 是线性的,采集数据点应该全部落在该直线上。实际的采样数据点与拟合直线的偏离程度,则表征了ADC 的非线性。在原AM824 开发板上测试的数据详见 表 2.6(Vref=2.5V)。

表2.6 AM824 开发板的INL 测试数据

AM824 开发板INL 数据的拟合曲线详见图2.31。

图2.31 AM824 开发板INL 数据的拟合曲线

在使用了本文改善措施的电路板上,重复测试获得的测试数据详见表2.7(Vref=3V)。

表2.7 标准化电路板的INL 测试数据

标准化电路板INL 数据的拟合曲线详见图2.32。

图2.32 标准化电路板INL 数据的拟合曲线

通过对比 表2.6 与表2.7 发现,在电路板上加入这些措施后,INL 得到了改善,从原来的5.3 个 LSB 改善为后来的3.6 个LSB。

>>> 2.4.3 失调与增益误差

1. 失调误差

失调误差定义为第一次实际的转换至第一次理想的转换之间的偏差。理想情况下,第一次转换应该发生在输入信号为0.5 LSB 时。失调误差以EO 标注,测试过程如下:

调节可调电阻,产生连续可变的mV 级电压值输入到标准化电路板,观察ADC 输出代码变为1 的电压值为:2.44mV。实测电路板上基准电压为:3047.56mV,算得1LSB =3047.56/(4096*2)=0.74mV。

2. 增益误差

增益误差定义为最后一次实际转换与最后一次理想转换之间的偏差。理想情况下,当模拟输入电压等于VREF-0.5LSB 时产生从0xFFE 至0xFFF 的变换。增益误差以EG 标注,测试过程为:调节可调电阻,产生Vref 附近连续可变的电压值输入到标准化电路板,观察ADC输出代码变为0xFFF 的电压值为:3046.35mV。

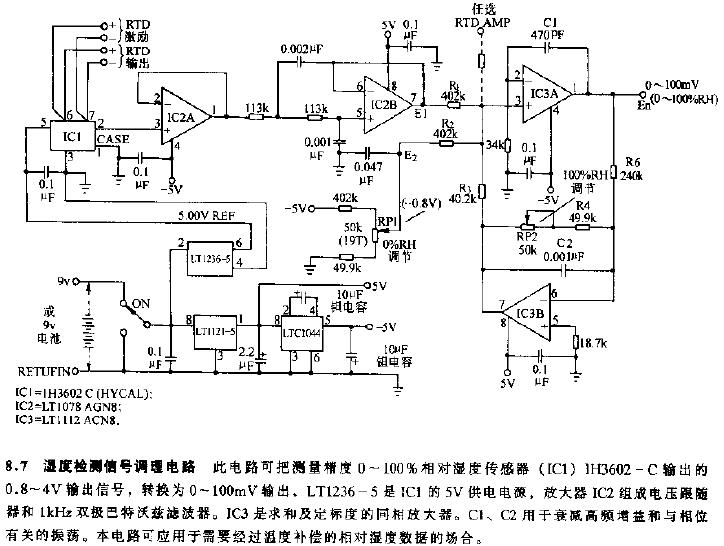

2.5 应用说明

总结改善后的标准化电路板和AM824 开发板的精度指标测试值详见表2.8。

表2.8 标准化电路板与AM824 开发板的ADC 测试精度

表中数据表明,经过上面提及到的方法改进后,除增加ADC 驱动运放导致失调电压有略微增加之外,所有参数指标都可以有进一步的改善。在AM824 开发板中无噪声分辨率比较低,根据公式log2(1/跳动LSB)log2(1/跳动LSB),在9 位左右。INL 根据公式log2(1/误差LSB)log2(1/误差LSB)也是9 位。

在改进设计后的标准化电路板,片上ADC 可以发挥更好的性能指标,其无噪声分辨率与INL 性能都提升到了10 位,适合于精度等级为0.5%的应用。

在实际应用中,如果用户需要进行修改滤波器带宽或输入范围等参数,可以在以下几方面进行,只需要做一些参数上或通道电路上的调整,详见表2.9。

表2.9 用户参数选择

-

adc

+关注

关注

99文章

6526浏览量

545273

原文标题:周立功:ADC 信号调理电路设计必要措施、实测验证和应用说明

文章出处:【微信号:ZLG_zhiyuan,微信公众号:ZLG致远电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

OPA564在搭建电路实测验证时候,实际输出有效值功率3W左右,波形畸变严重怎么解决?

振动信号调理硬件电路设计

手持示波表的前端模拟信号调理电路

心电信号调理电路设计

ADC 信号调理电路设计——必要措施、实测验证和应用说明

ADC 信号调理电路设计——必要措施、实测验证和应用说明

评论