在接下来的几年中,服务提供商将通过部署小型蜂窝网络、超小型蜂窝网络、DAS、μ-BTS和回传设备来构建5G网络。通过增加室外网络覆盖和容量,改善室内信号接收和现有的4G/LTE网络相辅相成……

迎向未来的移动通信网络技术大跃进,Silicon Labs(Silicon Labs)日前针对4.5G和基于以太网的通用公共无线电接口(eCPRI)无线应用,以及10/25/100G应用,分别推出两款高性能时钟产品:Si5381/82/86系列与Si5332系列。Silicon Labs时钟产品高级营销总监James Wilson先生在接受行业媒体专访时援引Cisco的数据称:“带宽需求正在驱动时钟产品的成长。”到2021年,全球互联网用户将达到46亿,约有271台设备实现互联,82%的总IP流量将会是视频。欲了解更多关于时钟应用与设计的趋势,欢迎点击“阅读原文”至Silicon Labs中文论坛阅读完整采访文章!

Silicon Labs时钟产品高级营销总监James Wilson先生

4.5G无线接入网时钟方案

James Wilson认为,在接下来的几年中,服务提供商将通过部署小型蜂窝网络、超小型蜂窝网络、DAS、μ-BTS和回传设备来构建5G网络。通过增加室外网络覆盖和容量,改善室内信号接收和现有的4G/LTE网络相辅相成。随着运营商逐渐转移到使用基于以太网的eCPRI前传网络来增加基带单元与远程无线电头之间的前传连接的容量,他们开始在网络边缘部署异构网络(HetNet)设备。而成本、功耗和尺寸限制则成为HetNet设备硬件设计人员要面临的特殊挑战。

Si538x时钟专门针对为HetNet设备提供参考时钟进行了优化。作为业界首款将低相噪4G/LTE时钟和低抖动以太网时钟结合在一起的时钟IC,Si538x系列大幅简化了HetNet设备中的时钟生成,据称可比竞争方案降低55%的功耗,占板面积减小70%,从而替代小型蜂窝网络、分布式天线系统(DAS)、μ-BTS,基带单元(BBU)和前传/回传设备等应用中所需的多个时钟器件和压控振荡器(VCXO)。

小型蜂窝网络和DAS设备是“一体化”基站,需要为4G/LTE收发器、基带处理和以太网/Wi-Fi连接提供参考时钟。Si5386时钟的低相噪DSPLL以紧凑的单芯片设计取代了分立时钟IC、VCXO和环路滤波器件。此外,Si5386时钟集成了五个MultiSynth小数时钟合成器,可以非常方便的提供以太网和基带参考时钟。这种现代化的单PLL+MultiSynth架构设计,相对于依赖多个PLL和分立振荡器的解决方案,提供了更高的可靠性。

基带单元具有复杂的时钟要求,需要多个独立时钟域,包括用于CPRI到远程无线电头连接的时钟域,用于基于以太网的eCPRI前传网络(包括eCPRI)的时钟域和用于本地基带处理的通用时钟的时钟域。Si5381/82时钟集成了一个高速、低相噪DSPLL用于支持高达3GHz的无线频率,并采用多个灵活的任意频率DSPLL来提供以太网和通用时钟。和Si5386一样,Si5381/82器件不需要外部VCXO或振荡器。所有PLL器件都集成在片内,并采用了节省空间的9x9mm64-LGA封装。

此外,Si538x时钟支持无缝切换功能,这使得系统设计人员能够轻松地在不同的时钟输入间切换并最大限度的减少输出相位瞬变,确保下游PLL保持锁定状态。和Silicon Labs的其他时钟产品一样,Si538x器件可以使用ClockBuilder Pro软件进行配置和定制。

Si5381/82/86无线时钟现已提供样片,并同步推出新型Si5381E-E-EVB、Si5382E-E-EVB和Si5386E-E-EVB开发套件。

10/25/100G以太网数据中心时钟方案

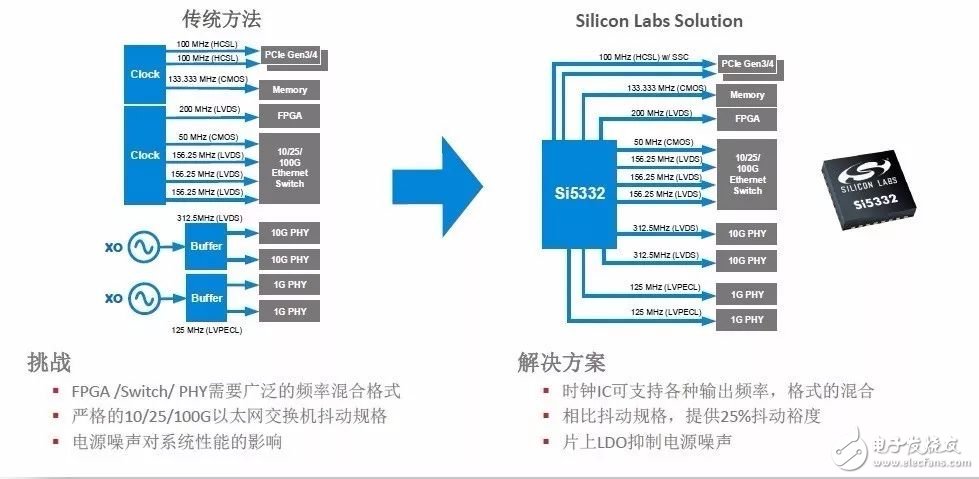

超高速数据中心正在迅速从10G迁移到25G、50G和100G以太网,以便加速数据传输和提高网络效率。这波新投资周期促使设备制造商将交换机和接入端口升级到更高速率,并采用更高性能的时钟解决方案。然而这些复杂的设备,例如以太网交换机、高速交换结构、网络处理器、服务器SoC和FPGA等,在单个IC中集成了数据路径处理、CPU功能和多个串行/解串器(SerDes)。因此,它们迫切需要多样化的参考时钟组合。

与使用石英振荡器、缓冲器和固定频率时钟发生器的传统时钟解决方案不同,Si5332时钟在单芯片器件中产生所有SerDes、处理器和系统时钟,同时提供显著的抖动余量,使系统开发人员能够有把握地简化时钟树。此外,Si5332系列还支持PCI Express,这是连接微处理器、网络、存储和内存的长期主流标准。PCI-SIG组织最近推出了PCI Express 4.0(0.9版本),支持16GT/s数据速率。Si5332系列产品完全符合PCI Express 4.0标准,同时为PCIe Gen 4规格提供60%的抖动余量。

其他行业联盟,包括CCIX、Gen-Z、NVLink和OpenCAPI,正在开发支持高达25GT/s速率的串行互连替代技术。除了要求低抖动时钟之外,还需要展频参考时钟。Si5332系列产品提供支持双独立展频通路的多功能解决方案。在每个输出基础上启用展频时钟生成,这使得单个时钟器件能够同时支持展频和非展频时钟的混合模式。

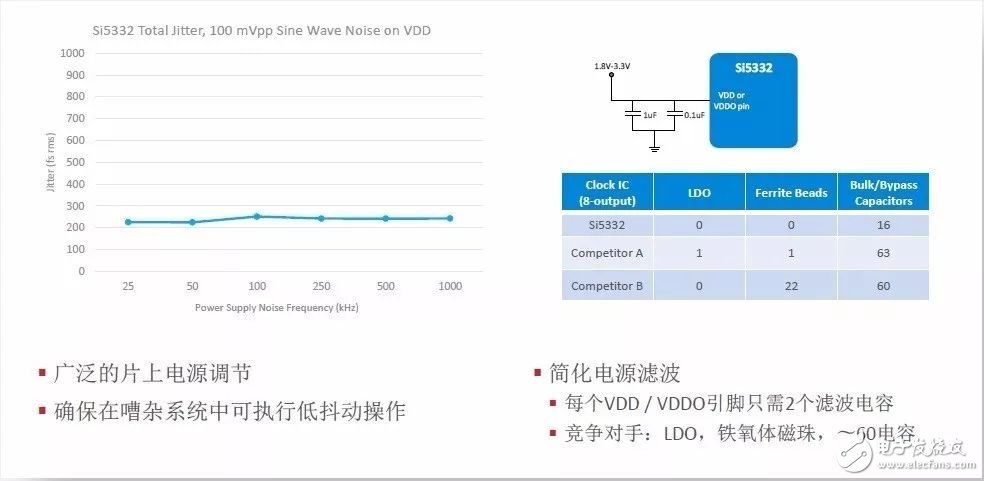

两个MultiSynth小数时钟合成器和五个独立的整数分频器是Si5332时钟发生器能够实现简化时钟树设计的关键,这使得数据中心无需再使用固定频率时钟和振荡器来产生时钟。SiliconLabs提供的数据显示,Si5332时钟具有230fs rms抖动性能,优于竞争解决方案2-5倍,同时提供10/25/100G SerDes时钟要求。Si5332时钟集成了大量片上电源调节器,无需竞争解决方案通常所需的片外昂贵的分立低压差(LDO)稳压器。基于MultiSynth架构的Si5332系列产品同样针对电源效率进行了优化,功耗比竞争对手低50-60%。

每个Si5332时钟输出可配置为LVPECL、LVDS、HCSL或LVCMOS时钟格式,并支持1.8V-3.3V电平,这无需分立的格式或电压转换器,简化了与FPGA、ASIC和SoC的接口设计。除了I2C控制之外,这些时钟产品还支持用户自定义的控制引脚,无需串行接口,可用于快速配置每个器件。和其他Silicon Labs时钟产品一样,Si5332时钟可以使用灵活的ClockBuilder Pro软件进行配置和定制。

Si5332任意频率时钟产品现已量产,可提供样片。此外,Silicon Labs也推出了新型的Si5332-6EX-EVB、Si5332-8EX-EVB和Si5332-12EX-EVB开发套件。

原文标题:【行家观点】高集成、低功耗时钟方案颠覆4.5G/以太网设计

文章出处:【微信号:SiliconLabs,微信公众号:Silicon Labs】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

是德科技与Capgemini合作验证5G NR NTN

是德科技与东北大学合作展示AI-RAN协调测试方案

LitePoint促进RAN生态系统内的创新

物联网接入网关数据安全与高效传输能力

物联网接入网关数据处理与优化能力详解

工控接入网关:实现工业物联网的关键技术

AI在无线接入网中的价值

3GPP R18标准正式冻结,5G-Advanced开启新篇章

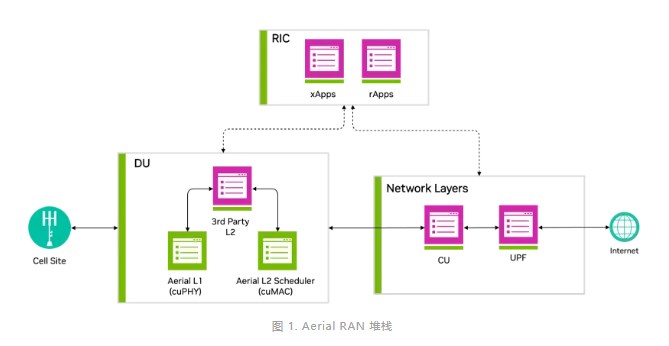

借助NVIDIA Aerial CUDA增强5G/6G的DU性能和工作负载整合

物联网接入网关是什么?

爱立信成功中标罗马尼亚STS无线电项目

是德科技与NVIDIA携手推进6G研究云平台发展

英伟达推出6G研究平台,加速智能应用发展

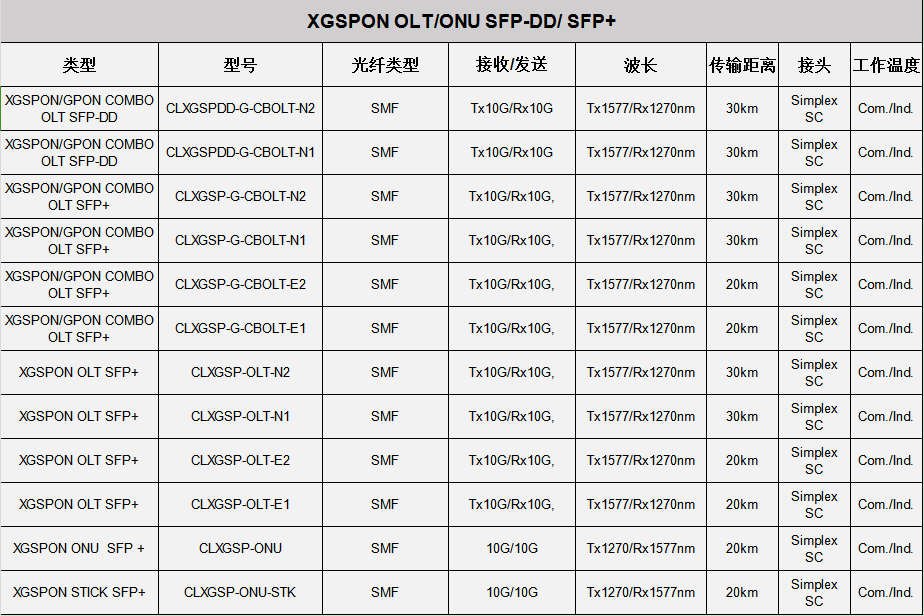

10G PON部署在企业接入中的应用

4.5G无线接入网时钟方案

4.5G无线接入网时钟方案

评论