大多数设计者都熟悉基于Pierce(皮尔斯)栅拓扑结构的振荡器,但很少有人真正了解它是如何工作的,更遑论如何正确的设计。我们经常看到,在振荡器工作不正常之前,多数人是不愿付出太多精力来关注振荡器的设计的,而此时产品通常已经量产;许多系统或项目因为它们的晶振无法正常工作而被推迟部署或运行。情况不应该是如此。在设计阶段,以及产品量产前的阶段,振荡器应该得到适当的关注。设计者应当避免一场恶梦般的情景:发往外地的产品被大批量地送回来。

本文介绍了Pierce振荡器的基本知识,并提供一些指导作法来帮助大家如何规划一个好的振荡器设计,如何确定不同的外部器件的具体参数以及如何为振荡器设计一个良好的印刷电路板。

在本文结尾处,有一个简易的晶振及外围器件选型指南,其中为MCU推荐了一些晶振型号(针对HSE及LSE),可以帮助大家快速上手。

1、石英晶振的特性及模型 石英晶振的特性及模型

石英晶体是一种可将电能和机械能相互转化的压电器件,能量转变发生在共振频率点上。它可用如下模型表示:

图1 石英晶体模型

C 0 :等效电路中与串联臂并接的电容(译注:也叫并电容,静电电容,其值一般仅与晶振的尺寸有关)。

L m :(动态等效电感)代表晶振机械振动的惯性。

C m :(动态等效电容)代表晶振的弹性。

R m :(动态等效电阻)代表电路的损耗。

晶振的阻抗可表示为以下方程(假设R m 可以忽略不计):

其中F s 的是当电抗Z=0时的串联谐频率(译注:它是L m 、C m 和R m 支路的谐振频率),其表达式如下:

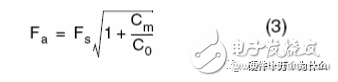

F a 是当电抗Z趋于无穷大时的并联谐振频率(译注:它是整个等效电路的谐振频率),使用等式

(1),其表达式如下:

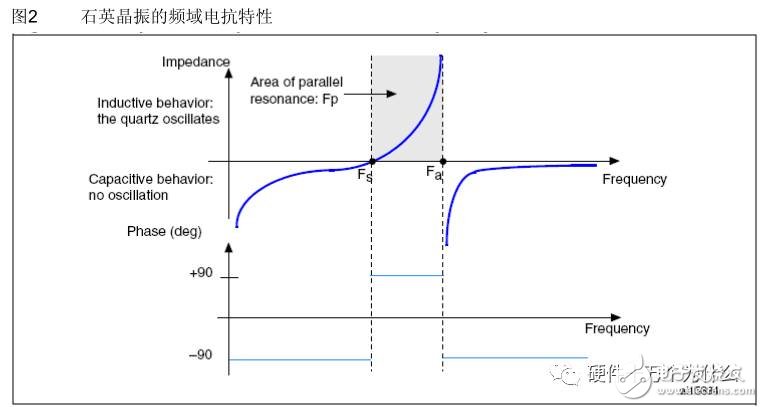

在F s 到F a 的区域即通常所谓的:“并联谐振区”(图2中的阴影部分),在这一区域晶振工作在并联谐振状态(译注:该区域就是晶振的正常工作区域,F a -F s 就是晶振的带宽。带宽越窄,晶振品质因素越高,振荡频率越稳定)。在此区域晶振呈电感特性,从而带来了相当于180 °的相移。

其频率F P (或者叫F L :负载频率)表达式如下:

从表达式(4),我们知道可以通过调节负载电容C L 来微调振荡器的频率,这就是为什么晶振制造商在其产品说明书中会指定外部负载电容C L 值的原因。通过指定外部负载电容C L 值,可以使晶振晶体振荡时达到其标称频率。

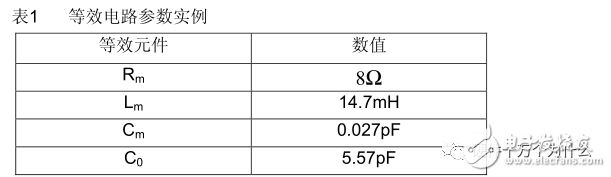

下表给出了一个例子来说明如何调整外部参数来达到晶振电路的8MHz标称频率:

使用表达式(2)、(3)和(4),我们可以计算出该晶振的F s 、F a 及F P :

F s = 7988768Hz,F a = 8008102Hz

如果该晶振的C L 为10pF,则其振荡频率为:F P = 7995695Hz。

要使其达到准确的标称振荡频率8MHz,C L 应该为4.02pF。

2、振荡器原理

振荡器由一个放大器和反馈网络组成,反馈网络起到频率选择的作用。图3通过一个框图来说明振荡器的基本原理

为了起振,Barkhausen条件必须得到满足。即闭环增益应大于1,并且总相移为360°。

为了让振荡器工作,要保证|A(f)|.|B(f)| >> 1。这意味着开环增益应远大于1,到达稳定振荡所需的时间取决于这个开环增益。然而,仅满足以上条件是不够解释为什么晶体振荡器可以开始振荡。为了起振,还需要向其提供启动所需的电能。一般来说,上电的能量瞬变以及噪声可以提供所需的能量。应当注意到,这个启动能量应该足够多,从而能够保证通过触发使振荡器在所需的频率工作。

实际上,在这种条件下的放大器是非常不稳定的,任何干扰进入这种正反馈闭环系统都会使其不稳定并引发振荡启动。干扰可能源于上电,器件禁用/使能的操作以及晶振热噪声等...。同时必须注意到,只有在晶振工作频率范围内的噪声才能被放大,这部分相对于噪声的全部能量来说只是一小部分,这也就是为什么晶体振荡器需要相当长的时间才能启动的原因。

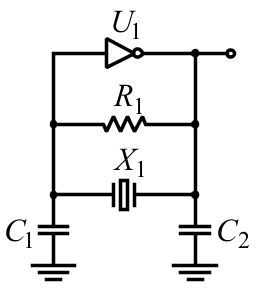

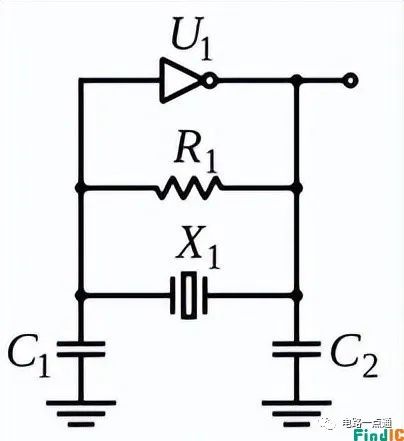

3 Pierce 振荡器

皮尔斯振荡器有低功耗、低成本及良好的稳定性等特点,因此常见于通常的应用中。

4 Pierce 振荡器设计

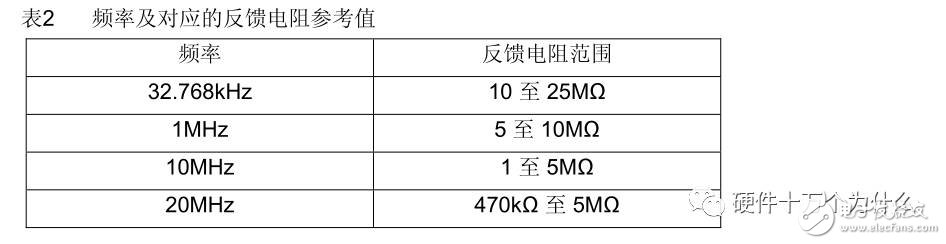

反馈电阻 反馈电阻R F

在大多数情况下,反馈电阻R F 是内嵌在振荡器电路内的(至少在ST的MCU中是如此)。它的作用是通过引入反馈使反向器的功能等同于放大器。Vin和Vout之间增加的反馈电阻使放大器在Vout= Vin时产生偏置,迫使反向器工作在线性区域(图5中阴影区)。该放大器放大了晶振的正常工作区域内的在并联谐振区内的噪声(例如晶振的热噪声)(译注:工作在线性区的反向器等同于一个反向放大器),从而引发晶振起振。在某些情况下,如果在起振后去掉反馈电阻R F ,振荡器仍可以继续正常运转。

负载电容 负载电容C L

负载电容C L 是指连接到晶振上的终端电容。C L 值取决于外部电容器C L1 和C L2 ,刷电路板上的杂

散电容(C s )。C L 值由由晶振制造商给出。保证振荡频率精度,主要取决于振荡电路的负载电容与

给定的电容值相同,保证振荡频率稳定度主要取决于负载电容保持不变。外部电容器C L1 和C L2

可用来调整CL,使之达到晶振制造商的标定值。

即:C L1 = C L2 = 20pF

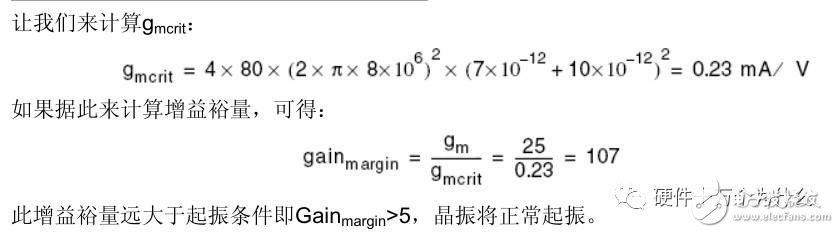

振荡器的增益裕量

增益裕量是最重要的参数,它决定振荡器是否能够正常起振,其表达式如下:

根据Eric Vittoz的理论(译注:具体可参考Eric A. Vittoz et al., "High-Performance Crystal Oscillator Circuits: Theory and Application", IEEE Journal of Solid-State Circuits, vol. 23, No. 3,pp. 774-782, Jun. 1988),放大器和两个外部电容的阻抗对晶振的RLC动态等效电路的电抗有补偿作用。

基于这一理论,反向器跨导(gm)必须满足:gm > gmcrit 。在这种情况下才满足起振的振荡条件。为保证可靠的起振,增益裕量的最小值一般设为5。

例如,如果设计一个微控制器的振荡器部分,其gm等于25mA/V。如果所选择的石英晶振(来自FOX公司)的参数如下:

频率 = 8MHz,C 0 = 7pF,C L = 10pF,ESR = 80 Ω

那么该晶体能否与微控制器配合可靠起振?

如果不能满足增益裕量起振条件(即增益裕量Gain margin 小于5,晶振无法正常起振),应尝试选择一种ESR较低或/和C L 较低的晶振。

5关于PCB的建议

1. 外部杂散电容和电感要控制在一个尽可能小的范围内,从而避免晶振进入非正常工作模式或引起起振不正常等问题。另外,振荡器电路旁边要避免有高频信号经过。

2. 走线长度越短越好。

3. 接地平面用于信号隔离和减少噪声。例如:在晶振的保护环(译注:(Guard ring),指器件或走线外围成一圈用于屏蔽干扰的导线环,一般要求理论上没有电流从该导线环上经过)下直接敷地有助于将晶振和来自其他PCB层的噪声隔离开来。要注意接地平面要紧临晶振但只限于晶振下面,而不要将此接地平面敷满整个PCB板(见图7)。

4. 像图7所示来布地线是一个好的作法。这种布线方法将振荡器的输入与输出隔离开来,同时也将振荡器和临近的电路隔离开来。所有的V SS 过孔不是直接连到地平面上(除晶振焊盘之外),就是连接到终端在C L1 和C L2 下方的地线上。

5. 在每一对V DD 与V SS 端口上连接去藕电容来平滑噪声。

硬十iBox晶振设计实例:

-

振荡器

+关注

关注

28文章

3832浏览量

139076 -

Pierce振荡器

+关注

关注

0文章

1浏览量

1035 -

振荡器设计

+关注

关注

0文章

1浏览量

1035

原文标题:微控制器振荡器电路

文章出处:【微信号:Hardware_10W,微信公众号:硬件十万个为什么】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

压控振荡器vco工作原理是什么

压控振荡器的指标有哪些

压控振荡器的工作原理是什么

数字振荡器的相位噪声是多少

反馈式振荡器的振荡平衡条件是什么

高频振荡器和低频振荡器的区别

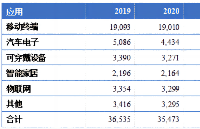

6.晶体和振荡器 行业研究及十五五规划分析报告(不同应用晶体和振荡器分析)

如何巧妙运用Pierce振荡器知识规划一个好的振荡器设计?

如何巧妙运用Pierce振荡器知识规划一个好的振荡器设计?

评论