关键词: GPS中频信号;USB;信号采集;数据分析

中图分类号: TN967.1

文献标识码: A

DOI:10.16157/j.issn.0258-7998.170792

中文引用格式: 陶梦,李金城. GPS中频信号采集及分析系统设计[J].电子技术应用,2017,43(9):34-38.

英文引用格式: Tao Meng,Li Jincheng. Design of a system for sampling and analysis of GPS IF signal[J].Application of Electronic Technique,2017,43(9):34-38.

0 引言

随着GPS全球卫星定位系统在提供定位信息和高精度时间信息上的广泛应用,国内外越来越多的企业和研究机构深入研究导航、授时芯片,而要实现这些功能,都离不开对GPS卫星信号的分析。因此,自主研发小型化、便携式GPS中频信号数据采集设备对导航算法研究及芯片设计非常重要[1]。

USB接口数据传输速率高、传输模式灵活,支持低速(1.5 Mb/s)、全速(12 Mb/s)和高速(480 Mb/s)3种传输速度以及中断传输、控制传输、同步传输和块传输4种传输模式,目前在PC领域中USB接口已广泛应用[2]。高集成度的GPS接收机射频前端芯片NJ1006可采集2 bit格式的GPS卫星信号,通过位拼接可将实时采样率下降至4 MHz左右。USB2.0的传输速度完全可以满足,而从成本和普及率方面综合考虑,使用USB2.0是一个较好的选择。

基于上述分析,本论文设计了一种GPS中频信号采集及分析系统。系统使用FPGA对NJ1006的数字中频信号进行字节拼接及缓存,通过USB接口芯片(FX2 68013)上传到PC。在PC端设计了专用的VC++程序,用于PC端的数据接收、格式转换及分析。

1 系统软硬件总体架构

本论文的GPS中频信号采集及分析系统的软硬件总体架构如图1所示,由硬件和软件两部分组成。其中硬件部分包括GPS射频接收芯片NJ1006、FPGA(cyclone EP1C12Q240C8N,具有20 060个逻辑单元和52个M4K存储器)和 USB2.0接口芯片(FX2-68013);软件部分包括数据接收程序、格式转换程序、数据分析程序和主控程序组成。

NJ1006是一个高集成度的GPS接收机射频前端IC,其集成了LNA和本机振荡器的谐振回路,减少了外部元器件数量和PCB的面积。NJ1006下变频1 575.42 MHz GPS L1信号,通过2 bit A/D转换器采样后,输出采样率为16.368 MHz,中频频率为4.092 MHz的2 bits数字信号(符号位SGN和大小位MAG)到FPGA。

FX2-68013是由Cypress半导体公司所推出的USB2.0芯片,芯片将USB外围接口所需要的各种功能包装成一精简的集成电路,其内部的8051微处理器方便对芯片的控制与配置[3]。通过对芯片内部8051编程,使USB2.0芯片配置在Slave FIFO模式下工作,异步方式传输数据,以支持图1中的高速数据通道;由于该USB2.0芯片具有I2C接口,支持对外部I2C存储器的读写,为了不影响高速数据传输,本论文用FPGA模拟了一个I2C存储器,上位机通过对I2C存储器的读写实现了对FPGA工作状态的控制[4]。

FPGA接收NJ1006的数字中频信号,进行位拼接和缓存,向USB2.0芯片发送数据,并通过USB2.0接口将采集的数据上传到PC。在PC端接收数据,并进行格式转换和数据分析。分析的主要任务是对GPS中频信号进行C/A码相位和多普勒频率的二维相关值计算,并由Matlab进行三维立体显示。

2 FPGA逻辑设计

2.1 数据拼接

GPS卫星信号是在16.368 MHz时钟下利用射频前端NJ1006接收得到的,由于该信号的位宽为2 bits,而FPGA与USB之间的数据总线位宽为8 bits,因此需通过“串并转换”,将串行数据转换为并行数据。此时,写入数据速度降低到原来的四分之一(4.092 MHz),将大大降低数据上传所需的时序要求。

2.2 数据缓存

USB2.0协议拥有较快的数据传输速率,但本设计使用Windows系统PC作为上位机,属于多任务系统,运行时会分出多个时间片给各应用程序,即使只运行本设计中的软件程序,也无法保证稳定的传输速度,将影响数据的实时传输性。为解决该问题,可通过增加存储器以缓存数据。但由于外部增加RAM的成本较大,且前文中提到的数据流采集速率约为稳定不变的4 MHz,而Windows平均的传输数据速率高于此采集速率,为了保证数据流的连续性,可利用FPGA 内部52个M4K存储器资源生成26 KB RAM作为缓冲器,把从位拼接得到的数据暂存在此RAM中,再通过USB2.0传输到上位机PC中进行存储和分析。

本系统中把这26 KB缓存空间分成13个2 KB RAM,将从位拼接得到的数据依次写进RAM中,同时将写满2 KB RAM的缓存数据依次读出传送至FX2,之后FX2一次性将2 KB数据通过USB2.0传输至上位机,由此对RAM0至RAM12这13个存储器进行循环操作,完成数据的读写操作。该方法能够最大限度地利用资源,保证了数据流的实时不间断。

缓存数据写入RAM的过程如图2(a)所示。系统在接收到RAM的写指令后,首先向RAM0写入采集到的数据。当RAM0写满后,若RAM1处于忙状态(即Rd_en[1]=1,系统从RAM1中读出数据),则终止写入,系统回归初始状态,等待写指令,否则无间断地向RAM1中写入数据。由此依次对RAM0至RAM12这13个存储器进行循环操作,完成数据的写入。该RAM写操作机制能够保证数据流的实时、不间断,符合数据采集要求。而缓存数据的读出过程如图2(b)所示。系统在接收到RAM的读指令后,首先从RAM0中读出数据,将其传送至FX2的Slave FIFO。完成RAM0的读操作后,若RAM1处于空闲状态(即Wr_en [1]=0,系统未向RAM1写入数据),则无间断地读取RAM1中的缓存数据,否则等待RAM1完成写操作之后再继续进行读操作。对RAM0至RAM12这13个存储器进行循环读操作,直到采集结束。

2.3 数据传送

数据传送即通过FX2 的Slave FIFO模式,将从RAM中读出的数据上传至上位机PC并保存,其高速数据传送通道接口图如图3所示[5]。在开始传送数据前,需通过Slave FIFO的切换地址fifoaddr配置Slave FIFO为2′b10,使其能够向FX2的Slave FIFO写入数据。接收到数据传送指令后,主程序实时监控Slave FIFO的空满标志empty、full。当发现Slave FIFO未满时,通过控制Slave FIFO的写时钟slwr,将从RAM读出的数据传送至Slave FIFO的双向数据端口fd,构成了高速数据通道,完成数据上传。

2.4 FPGA状态转换

FPGA主状态机的状态转换图如图4所示,整个状态机工作在72 MHz时钟下,INIT状态对FX2各接口数据进行初始化,之后进入WAIT_CMD状态,等待上位机发指令。当上位机发出采集指令后,由USB向FX2内部8051芯片下传48 B数据发送指令,再由8051将此48 B数据写入I2C的存储器,并分析第一字节数据[6]。当第一字节为8′h0a时,状态机进入CMD_PRO状态,进行指令处理,向RAM发出写指令开始数据缓存,然后进入READ_RAM状态,在识别FX2中Slave FIFO的空满标志等信号后,读出RAM缓存数据。关于RAM读写调用在上文中有详细介绍,这里不再赘述。当采集结束后,状态机重新回到WAIT_CMD状态,等待下一次采集。

本设计中的采集结束机制分为两种情况,一种是当要向单个RAM写入数据时系统正在读出该RAM中的数据,无法继续进行写操作,导致实时传输数据中断。此时上位机长时间接收不到数据,将自动终止接收数据,这是由数据实时传输数据速率大于上位机接收数据速率导致的,此时软件将通知用户此次数据不可靠;另一种是上位机接收到的数据已经满足采集数据的大小要求,此时上位机主动停止接收数据,FX2 slave FIFO一直处于满状态,FPGA超过规定时间的等待还不能继续上传数据,状态机回到WAIT_CMD状态,此次采集结束,等待下一次采集。

3 软件操作

上位机程序使用C语言的MFC编写,操作界面如图5所示。USB Connection键可对FX2中的8051芯片进行配置,实现USB和FPGA数据通道连接。点击图中的Sample键,发出采集指令后,上位机开始调用FX2专用的批量端点上传函数,反复循环128次来接收256 KB数据,等待接收数据,再通过USB传输指令,使FPGA与上位机协同工作,采集数据[7]。

数据采集结束后,可通过软件操作界面的TXT Conversion窗口将数据格式转换为ASCII码或对应的0-1二进制序列,方便用户使用。

通过图5中的SV-Searching Paramenters窗口可设置参数,进行数据分析。源文件为当前数据采集转换后的0-1二进制序列文件,通过设置卫星号SV num(1至32号卫星)、毫秒积分ms num(1 ms至10 ms)、量化位LO bits(1 bits至10 bits)和多普勒频率范围LO Frequency、CA码相位C/A Phase以及相对应的频率步长LO Step、C/A步长C/A Step等参数,点击Analysis键,对其进行CA码和多普勒频率的二维搜索。通过时域串行捕获算法计算得到三维数据,并利用Matlab的surf函数仿真出三维立体图,从而分析信号的可靠性[8]。

时域串行捕获算法如图6所示,即本地载波生成器在预先设定的多普勒频率范围内选择一个载波频率,产生两路相位差 90°的本地载波cos和sin。将输入信号与这两路本地载波混频,得到同相分量I和正交分量Q。然后将I和Q两路分量分别与本地产生的C/A码序列进行相关运算,并通过绝对值求和Absolute或平方求和square运算得到相关值[9-10]。

4 GPS中频信号采集及分析结果

本文通过图形操作界面对卫星信号进行采集、转换和分析,实现了自主研发小型化、便携式GPS中频信号数据采集设备。GPS卫星信号数据于2017年1月13日下午1点20分在北京交通大学第九教学楼采集,此时的18号星1 ms平方和运算对应相关值如图7所示。从图中可明显观察到,该卫星的频率在4.094 5 MHz附近,码相位在16 000点附近出现明显的相关峰。图8则是18号星进行绝对值求和对应的相关图,对比图7和图8可以看出,在信号明显的情况下两种运算都能找到相关峰,但绝对值求和得到的相关值基数更小,所需的硬件资源更少,相比之下,平方求和其相关峰则更加明显。

在全搜索的基础上,找到相关峰后还可对其进行更精确的搜索。在图7 18号星全搜索的基础上,将频率搜索范围缩小到4.092~4.097 MHz,并缩小频率步长为250、CA码步长为2,对其相关峰进行放大分析,其结果如图9所示,该方法便于分析算法的可靠性以及信号正确性。

软件还支持多毫秒叠加,设置多普勒搜索步长、频率和CA码采样点数等。由于当前某颗卫星的信号比较弱,1 ms相关值累加有可能不能准确地找出相关峰,此时可通过多毫秒累积的方法得到相关峰。图10为27号星1 ms的相关值,从图中不能明显地观察到相关峰,但通过图11中的2 ms运算可以看到,在频率为4.092 MHz、码相位为8 000处有明显的相关峰。

5 结论

本文针对GPS中频信号的采样、转换、分析提出了相应的解决方案。实验证明,基于USB2.0的数据传输方案达到了对GPS中频信号高速准确的采集目标。基于GPS的捕获算法,通过C语言实现时域串行捕获算法检测,验证了数据的可靠性,为之后的GPS算法研究奠定了坚实的基础。

-

GPS中频信号采集

+关注

关注

0文章

1浏览量

2009 -

GPS系统设计

+关注

关注

0文章

1浏览量

2043

原文标题:【论文精选】GPS中频信号采集及分析系统设计

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一种GPS信号干扰源的设计与实现

数字方法中频信号相干检波实现

中频信号与伴音信号处理电路

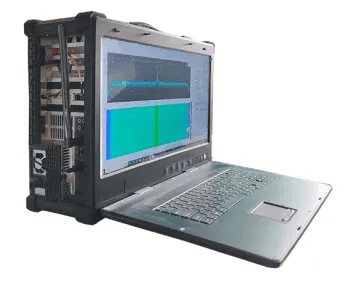

NewStar210A数字回放式GPS中频信号采样器

基于GPS中频信号源的FPGA设计实现方案

坤驰科技丨L波段射频信号采集记录与回放系统 QTS12331-L

GPS中频信号采集及分析系统设计知识分享

GPS中频信号采集及分析系统设计知识分享

评论