在高性能应用中,例如通信、无线基础设施、服务器、广播视频以及测试和测量装置,当系统集成更多功能并需要提高性能水平时,硬件设计就变得日益复杂,为系统提供参考时序的板级时钟树也走向这种趋势。在进行时钟树设计时, “ 一成不变 ” 的策略并不适用,优化时钟树以满足性能和成本的要求取决于多种因素,包括系统架构、集成电路( IC )时序需求(频率、信号格式等)和终端应用的抖动需求。

参考时序 - 何时使用晶体或时钟

第一个设计原则是理清硬件设计的参考时钟需求,并选择用于系统中处理器、 FPGA、 ASIC、 PHY 、 DSP 和其他组件的参考时钟类型。如果 IC 已集成振荡器和片上锁相环( PLL )用于片内时序,那么通常可以使用石英晶体。石英晶体具有成本效益,因其优异的相位噪声特性而被广泛使用,他们放在靠近IC的地方,以简化电路板布局。然而,晶体的缺点之一是在整个温度范围内频率有显著变化,超出许多串化器/并化器( SerDes )应用中高精度ppm等级的稳定性需求。在许多要求高稳定性的高速SerDes 应用中,推荐使用晶体振荡器( XO ),因其可以确保比无源晶体更可靠的稳定性。

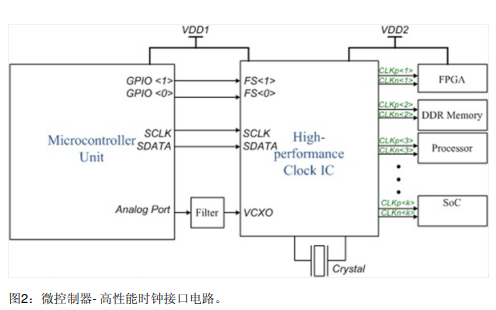

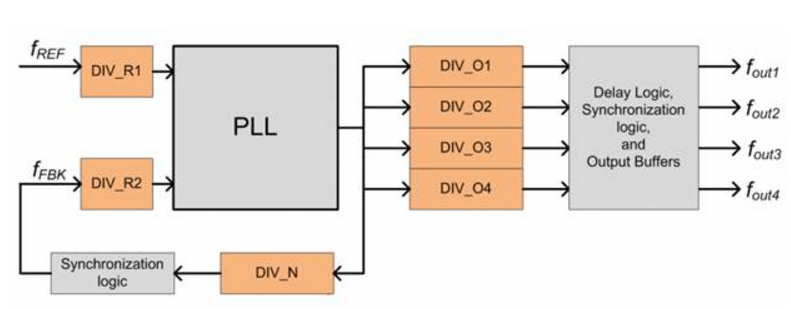

当需要多个参考频率时,通常使用时钟发生器和时钟缓冲器。在某些应用中,FPGA/ASIC有多个时钟域用于数据通路、控制平面和存储控制器接口,需要多个特定参考频率。如果 IC 不提供晶体输入接口,或者当 IC 需要与外部参考(同步源应用)同步时,又或者当所需高频参考值很难由晶体生成时,时钟发生器和缓冲器也是优先选择。

自由运行对比同步时钟树

一旦硬件设计确定下来,并且为部分器件选择了晶体,接下来的步骤就是为剩下的时钟选择时序架构:自由运行或同步。对于需要一个或多个独立参考时钟,且没有任何特殊锁相环或同步需求的应用来说,XO、时钟发生器和时钟缓冲器是理想选择。处理器、存储控制器、 SoC和外围组件(例如, USB 和 PCI Express 转换器)通常使用 XO、时钟发生器和时钟缓冲器组合,为自由运行和异步的应用提供参考时序。

如果应用需要一到两个定时源,XO 是最好的选择;而时钟发生器和缓冲器更适合同时需要多个独立时钟的应用。时钟发生器能够合成多个不同频率的时钟,但与由时钟缓冲器加上XO组成的时钟树相比,牺牲部分抖动性能。时钟缓冲器可以与XO 参考联合分配多个相同频率的时钟,并且为多输出时钟树实现最低抖动。

-

时钟设计

+关注

关注

0文章

27浏览量

10908 -

高性能时钟

+关注

关注

0文章

1浏览量

1265 -

时钟设计技巧

+关注

关注

0文章

1浏览量

1196

原文标题:高性能时钟设计与应用

文章出处:【微信号:SiliconLabs,微信公众号:Silicon Labs】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时钟设备如何满足复杂系统的高性能时序需求?

时钟IC怎么满足高性能时序需求?

时钟的重要性,如何正确设计高性能转换器

系统时钟源的比较选择及高性能PLL的发展趋势

MAX3679A高性能四路输出时钟发生器(Maxim)

ADI公司宣布收购高性能时钟技术MULTIGIG公司

采用MPC92433高性能时钟合成源完成时钟信号电路的设计

时钟设备如何才能实现复杂系统的高性能时序需求

高性能时钟芯片

设计高性能时钟的几点技巧

设计高性能时钟的几点技巧

评论