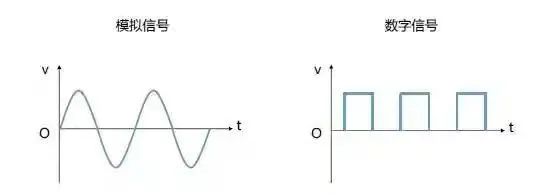

关于电平标准的由来:

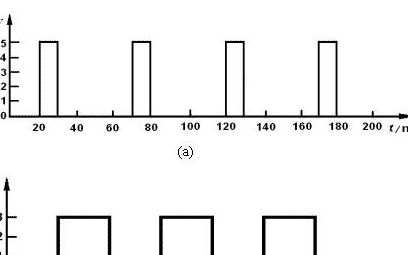

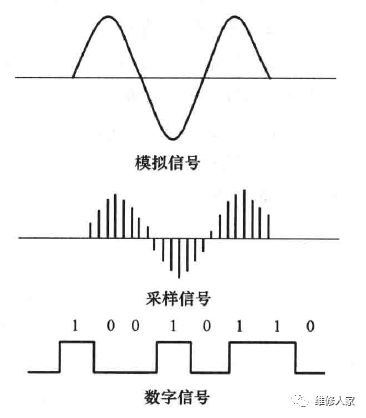

在以高(1)和低(0)为格式的数字通信过程中必然要涉及到高和低对应的模拟电压值,而这个值的确定是有原因和历史的。具体而言就是和半导体器件的发展有关,例如TTL即Transistor-Transistor Logic (晶体管-晶体管逻辑集成电路),这是因为半导体器件中最先发明的是双极型晶体管。而后由于MOS,CMOS工艺的发展给电路的供电需求带来新的改变而导致输出数字电平标准的变化。

一、TTL和CMOS电平介绍

TTL电路只能在5V或以下工作,VCC=5V时。

TTL输出:VOH>2.4V,VOL<0.4V。

输入:VIH>2.0V,VIL<0.8V。

CMOS电路的工作电压范围更宽,可达到12V,VCC=5V时。

CMOS输出:VOH>4.99V,VOL<0.01V。

输入:VIH>3.5V,VIL<1.5V。

可以看出TTL电平的噪声容限为0.4V,CMOS的噪声容限为1.5V。

TTL和CMOS门电路结构:

如图TTL门结构,输出级采用推挽式输出结构,T4为射极跟随的形式,输出电阻小,带负载能力强。

如图CMOS门结构。

TTL和CMOS驱动的几个特点:

1、TTL输出电阻小,因此带载能力一般更强。

2、TTL的响应速度更快一般在ns级,CMOS稍大,但是先进的高速MOS设计速度已经不输于TTL。

3、TTL为电流驱动,功耗更大,无法进行更大规模集成。

4、CMOS的栅极输入更容易受到干扰,因为输入阻抗远大于TTL输入,因此不能悬空。

5、现代集成电路工艺综合TTL和CMOS的特点发展出Bicmos工艺。

6、TTL和CMOS电平有差异,需要进行转换才能有效识别。

TTL和CMOS电平的发展

因为TTL的高电平2.4V与5V之间存在空闲区间,后来又发展出低压的LVTTL,具体电平标准根据手册。

3.3V LVTTL:VCC:3.3V VOH>2.4V,VOL<0.4V;VIH>2V;VIL<0.8V;

V2.5V LVTTL: VCC:2.5V。VOH>2.0V,VOL<0.2V,VIH>1.7V,VIL<0.7V.

同样也发展出LVCMOS电平。

3.3V LVCMOS: Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。 2.5V LVCMOS: Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。

二、高速电平标准

在高速电路中如何实现高速驱动输出呢?要么增大驱动电流,要么降低电平标准,或者提高晶体管工作速度。显然前者会带来非常大的功耗,因此改变电平标准和改进晶体管设计成为选择,虽然低电平更容易受到干扰,所以需要更严格的硬件设计。

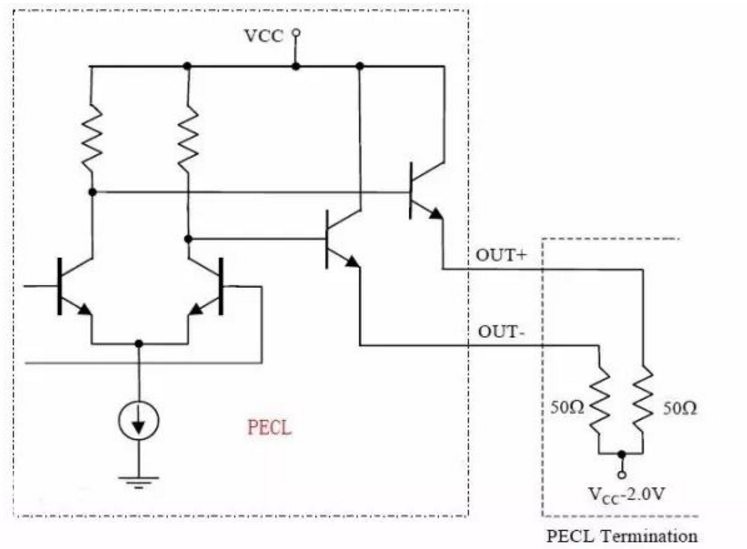

1、ECL和PECL电平接口

ECL即射极耦合逻辑(Emitter Coupled Logic)采用的是差分结构输出,并需要负电源供电。后来发展处PECL,即正电源射极耦合逻辑。基本原理就是利用晶体管工作在非饱和区来减小转换时间,大大提高转换速度。

ECL的输出管始终有电流通过,非常有利于高速转换。输出阻抗几欧姆,输出电流10mA左右,驱动能力强。

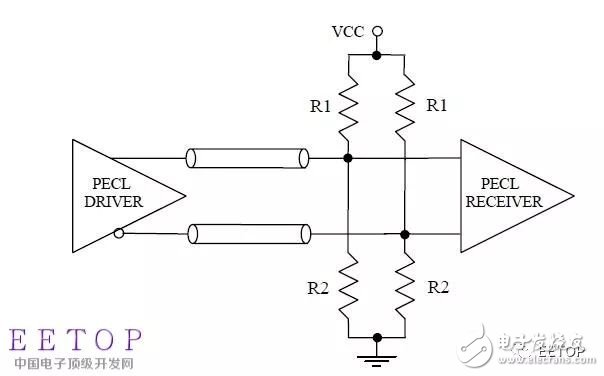

接口连接:直流耦合,适用于短距离

这个匹配方式由等效而来,具体阻值计算:

接口连接:交流耦合,适用于较远距离

2、LVDS电平接口

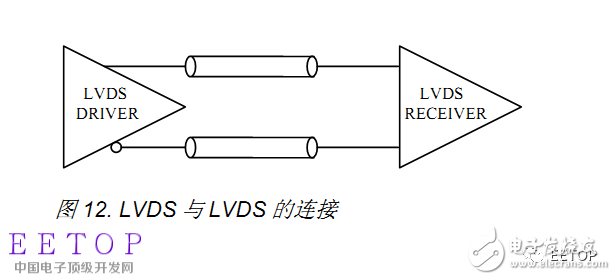

LVDS即Low-Voltage Differential Signaling,是一种利用低压差分信号传输高速信号的电平标准。特点是:低压,低功耗,噪声抑制能力强。

如图LVDS的输入和输出规格:

LVDS的连接方式:直接连接,因为片内具有端接电阻。

、

、

三、CML电平接口

CML即电流模式逻辑电平,采用恒流驱动,内置匹配电阻,使用简单,短距离高速应用中最多。

下图是几种高速接口的性能简单比较:

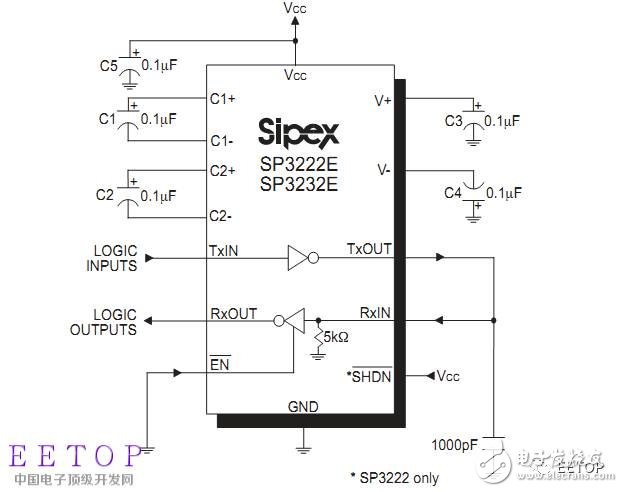

三、常用普通电平标准

在工业领域应用最多的应该是485 232的电平标准,两者各有优缺点,成本低,使用也比较简单,但是依然有很多技术要点可以讨论,譬如传输速度,距离,防护设计等等。

因为485输出的是A/B差分信号,因此485属于半双工通讯,而232属于全双工通讯。

485和232的几个特点及原因说明:

1、传输距离。受驱动电容的影响,232允许的电容负载为2500pF,因此传输距离在15~30m。而485采用的是差分传输,距离可达上千米。

2、传输可靠性。232因为收发端共地的原因更容易受到干扰,485实际上两根线就可以应用,可靠性要好。

3、电平标准。232:高电平为-3V~-15V。低电平为+3V~+15V。485发送时:高电平A-B为+2V~+6V,低电平为-2V~-6V,接收时|A-B|差值在200mV以上。

4、关于共模电平,显然232的共模电平更高,容易损坏芯片,可靠性稍低。

5、RS485可以进行组网通讯,总线最多可带32台。

接口的防护设计问题一直是重中之重,基本电路结构原理实际上并不难,主要在于对问题的综合分析和处理。按照干扰源-传播路径-屏蔽措施的套路来逐步实验处理。如图以485为例的接口防护电路设计

RS232和RS485的连接问题:

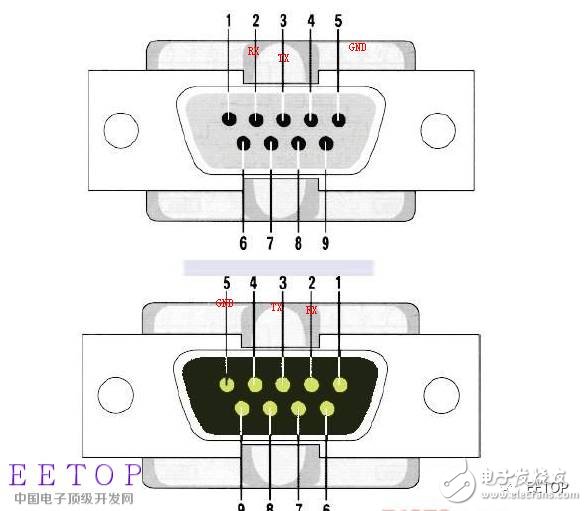

工作中了解到不少同学对于232或者485的连接一直有些迷糊,关于信号的收发端定义及公母头连接,一开始我也是经常摸不着头脑。以收发地三线为主。

标准的232是DB9接头:

简记为:235-收发地。

485如何利用DB9连接:

485的两根线对应DB9头的1,2脚。

232和485与MCU的连接:

四、小结

关于数字电平的标准主要就这么几种,这些都是在硬件层面的定义,在软件上对应的就有各种协议通讯方式的规定。关于接口设计确实是电路设计中的重点,尤其是在目前的高速数字通讯应用当中,我觉得主要有几个要掌握的方面:

1、信号电平的应用电路,也就是基本结构要清晰。

2、防护设计问题要考虑周全,不同接口对于负载对于匹配度的要求都不一样。

3、PCB设计的重要性,在高速设计中很多都采用EDA软件仿真的方式来协助查找关于干扰的问题,但是首要的还是要严格遵循相关规则和规范来设计。

4、实验的必要性。尤其是接口的干扰问题,尽可能全面的实验方案设计是尽快解决问题的最佳路径之一。

总之,理论基础要有,设计考虑要到,测试实验要全,如此,结果可能才好!

原文标题:硬件开发者之路之——数字电路电平标准全解析

文章出处:【微信号:eetop-1,微信公众号:EETOP】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字电路是什么

数字电路及其应用

数字电路及其应用

数字电路及其应用

数字电路的应用介绍

电平特性数字电路中有哪几种电平

数字电路电子教材 PPT

怎样看数字电路图

如何才能快速掌握数字电路的电平标准

如何快速掌握数字电路的电平标准

如何快速掌握数字电路的电平标准

评论