2.电源和地忘记接了。。。。还有接反的。。。

3、连接器的线序搞反了

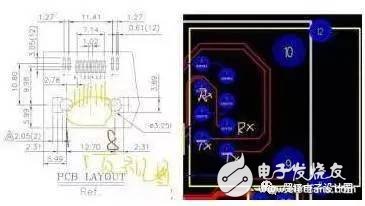

4、RX、TX接反了。。。

串口RX,TX画的时候心里默念不要接反,不要接反,板子贴片回来测试,果然串口不通。

5、想当然的写一个封装,结果没有这个规格的器件。百度文库下载datasheet,结果根本买不到这个器件。

6、直接抄电路,结果器件根本买不着。

曾经一个做智能锁的团队,电路直接抄三星的智能锁,结果里面一个电容式触摸按键的控制器,是韩国产的很难买到,而且没有什么代理和支持。纯靠自己试验和摸索。

7、选择电容的时候,只考虑容量,没有考虑耐压,结果这么大的封装放不下满足规格电容。

8、选择电阻的时候,只看阻值,不看功耗。

9、画完PCB,不看DRC报告,靠眼睛看飞线,回板后就真的飞线了。

脑残的一次把短路DRC关了,结果回来板子电源正负果然连一起了。

10、封装做反了。。。

当时赶进度,没拿到芯片只看了Datasheet就画了图投了板,板子回来后看着镜像的封装一脸懵x。但这事不能怪我,因为那个傻x datasheet上的封装图居然是bottom view而且没有注明!

11、散热焊盘的阻焊层没有处理

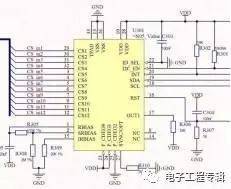

12、lm1117整个画反了,ina826同向端反向端看错了原理图就画错了。。烧程序时候忘了选外部晶振然后测了好久好久 发现我擦,烧程序的问题。

13、431真是奇葩设计,每次用都检查几遍管脚顺序

关于431稳压器SOT23封装的引脚排列,原来以为各个厂家排序都一样。结果发现:从左到右数,TI-TL431A是CAR排列,UTC-TL431A和CJ431A是RAC排列。还有继电器引脚排列,文档一般给个底视图,结果画板时没有镜像,只好把继电器焊接到背面.

14、对着datasheet把封装画反了,信誓旦旦的说这是我布局布得最漂亮的一块

15、板子只要有子卡,那就等着手心莫名其妙出汗,睡觉被吓醒了。

16、电池接口极性画反。。损失惨重

附电路设计常见的八个误区

现象一:这板子的PCB设计要求不高,就用细一点的线,自动布吧

点评:自动布线必然要占用更大的PCB面积,同时产生比手动布线多好多倍的过孔,在批量很大的产品中,PCB厂家降价所考虑的因素除了商务因素外,就是线宽和过孔数量,它们分别影响到PCB的成品率和钻头的消耗数量,节约了供应商的成本,也就给降价找到了理由。

现象二:这些总线信号都用电阻拉一下,感觉放心些。

点评:信号需要上下拉的原因很多,但也不是个个都要拉。上下拉电阻拉一个单纯的输入信号,电流也就几十微安以下,但拉一个被驱动了的信号,其电流将达毫安级,现在的系统常常是地址数据各32位,可能还有244/245隔离后的总线及其它信号,都上拉的话,几瓦的功耗就耗在这些电阻上了。

现象三:CPU和FPGA的这些不用的I/O口怎么处理呢?先让它空着吧,以后再说。

点评:不用的I/O口如果悬空的话,受外界的一点点干扰就可能成为反复振荡的输入信号了,而MOS器件的功耗基本取决于门电路的翻转次数。如果把它上拉的话,每个引脚也会有微安级的电流,所以最好的办法是设成输出(当然外面不能接其它有驱动的信号)

现象四:这款FPGA还剩这么多门用不完,可尽情发挥吧

点评:FGPA的功耗与被使用的触发器数量及其翻转次数成正比,所以同一型号的FPGA在不同电路不同时刻的功耗可能相差100倍。尽量减少高速翻转的触发器数量是降低FPGA功耗的根本方法。

现象五:这些小芯片的功耗都很低,不用考虑

点评:对于内部不太复杂的芯片功耗是很难确定的,它主要由引脚上的电流确定,一个ABT16244,没有负载的话耗电大概不到1毫安,但它的指标是每个脚可驱动60毫安的负载(如匹配几十欧姆的电阻),即满负荷的功耗最大可达60*16=960mA,当然只是电源电流这么大,热量都落到负载身上了。

现象六:存储器有这么多控制信号,我这块板子只需要用OE和WE信号就可以了,片选就接地吧,这样读操作时数据出来得快多了。

点评:大部分存储器的功耗在片选有效时(不论OE和WE如何)将比片选无效时大100倍以上,所以应尽可能使用CS来控制芯片,并且在满足其它要求的情况下尽可能缩短片选脉冲的宽度。

现象七:这些信号怎么都有过冲啊?只要匹配得好,就可消除了

点评:除了少数特定信号外(如100BASE-T、CML),都是有过冲的,只要不是很大,并不一定都需要匹配,即使匹配也并非要匹配得最好。象TTL的输出阻抗不到50欧姆,有的甚至20欧姆,如果也用这么大的匹配电阻的话,那电流就非常大了,功耗是无法接受的,另外信号幅度也将小得不能用,再说一般信号在输出高电平和输出低电平时的输出阻抗并不相同,也没办法做到完全匹配。所以对TTL、LVDS、422等信号的匹配只要做到过冲可以接受即可。

现象八:降低功耗都是硬件人员的事,与软件没关系。

点评:硬件只是搭个舞台,唱戏的却是软件,总线上几乎每一个芯片的访问、每一个信号的翻转差不多都由软件控制的,如果软件能减少外存的访问次数(多使用寄存器变量、多使用内部CACHE等)、及时响应中断(中断往往是低电平有效并带有上拉电阻)及其它争对具体单板的特定措施都将对降低功耗作出很大的贡献。

-

电容器

+关注

关注

64文章

6240浏览量

99886 -

连接器

+关注

关注

98文章

14586浏览量

136795 -

智能锁

+关注

关注

18文章

1067浏览量

39163

原文标题:搞反了,忘接了,画个电路被自己蠢哭了

文章出处:【微信号:Mouser-Community,微信公众号:贸泽电子设计圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

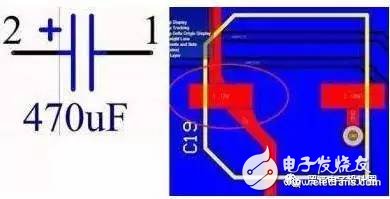

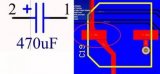

有极性电容,原理图和PCB把管脚搞反了?

有极性电容,原理图和PCB把管脚搞反了?

评论