在这篇文章中,我将会介绍一个有趣的时钟芯片反馈装置。它可能意外发生,或作为尝试恢复或测试模式,但通常应该如所解释的那样避免。此外,了解Ouroboros时钟可能有助于在复杂的定时应用中解释一些奇怪的行为。在深入了解“Ouroboros”时钟之前,我们来看一下基本的时钟切换术语和标准输入时钟切换配置。欢迎点击“阅读原文”观看全文!

一些基本时钟切换术语

时钟芯片通常支持基于某些限定条件(例如LOS(Loss of Signal))或OOF(Out of Frequency)的条件,从一个输入时钟切换到另一个输入时钟。以下是最常用的术语:

自由模式

基于附加晶体或其他谐振器的输出时钟,或替代外部参考时钟。输出时钟的频率稳定性,漂移和抖动特性由芯片的晶振决定,与输入时钟无关。

保持模式

输出时钟基于所选输入时钟的历史频率数据,并且在输入时钟丢失并且没有有效的备用可用时使用。通常历史数据必须在一些最短时间内被收集,以被认为是有效的。频率精度与收集的数据一样好。

锁定模式

输出时钟频率和相位锁定到所选择的输入时钟,即正常操作。

标准输入时钟切换配置

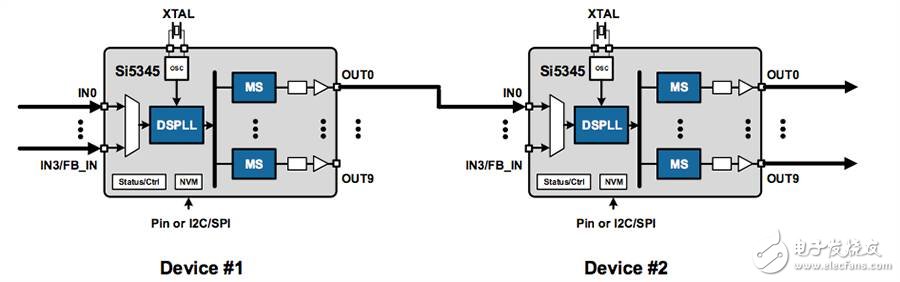

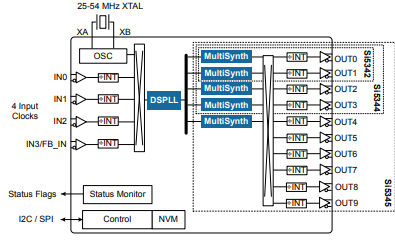

考虑下图中的两个抖动衰减器时钟IC级联的图示。这可能用于额外的抖动衰减或优化频率的计划和分配。为了说明,这些设备被描绘为非常简化的Si5345框图。在该图中,IN0和IN3提供给设备#1两个输入时钟。

在典型的应用中,一个时钟可以被认为是“主”时钟,另一个被认为是“辅助”时钟。主时钟可能会从网络数据恢复,而辅助时钟则依赖本地振荡器。如果主时钟故障或被LOS或OOF取消资格,则时钟芯片切换到辅助时钟。这通常旨在使“下游”设备保持运行。如果主时钟返回并且有效,那么根据所选择的选项,时钟IC可能会还原到它。

这里的推测是,只要这两个时钟中的任何一个存在,则在OUT0处产生有效的锁定模式时钟,从而向下游设备#2提供输入时钟。实际上,如果设备#1的两个输入时钟都丢失,则设备可以进入保持模式,如上所述,甚至是自由模式,并且仍然产生临时合理的输出时钟。

时钟配置

在标准应用中,下行时钟不反馈到上行时钟输入。相反,它们通常是上游独立稳定或数据导出时钟的缩放或抖动衰减版本。

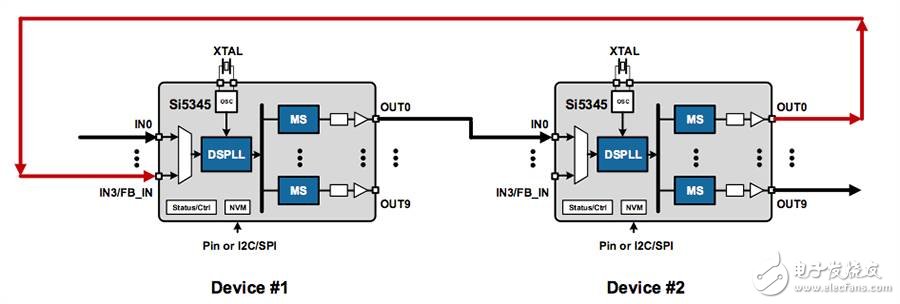

但是如果我们尝试了如下图2所示的配置怎么办?在这种情况下,下游设备#2的输出之一被反馈到上游设备#1。这可能是作为临时的备份时钟。

现在如下图3所示,当我们失去主时钟IN0时会发生什么?辅助或备用时钟IN3至设备#1依赖于设备#2的输出。请注意,这只是Device#1输出的锁定版本。我们通常不会看到这种与一个设备的连接,但偶尔提出涉及2个设备的应用程序。

这是Ouroboros时钟配置。(是的,它听起来就像生活大爆炸的台词。)Ouroborus时钟配置的命名,是应为它的反馈类似于蛇追逐(或咬)它的尾巴的神话符号。根据维基百科,这个词来自希腊语“ourá”和“bóros”,用于描述“吞噬或吞咽”。见图4中的图示。它是古代的循环无穷符号,适用于此应用。

Gedanken

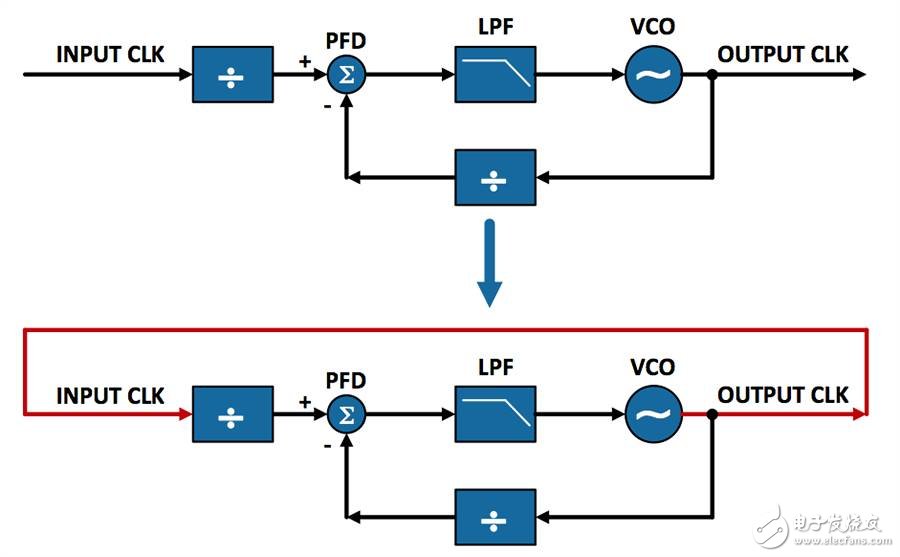

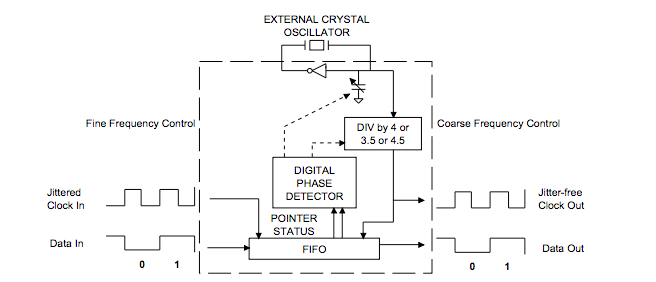

我们考虑一个简单的gedanken实验,由一个基本的PLL组成。然后假设它已经成功地被放置在Ouroboros配置中,如下面的图5所示。

现在我们可以考虑可能的后果。如果一切都是理想的,并且没有PFD(相位检波器)错误输出,则情况至少是稍微稳定的。然而,即使忽略环路噪声,很可能在实际的PLL中,在PFD(+)和PFD( - )之间呈现的时钟之间存在固定的相位偏移。在正常的PLL操作中,可以调节VCO,以便将输出时钟频率和相位锁定到独立的输入时钟。在Ouroboros配置中,VCO无法减少相位误差。

假设输出时钟以相位快速测量,在PFD(+)对PFD( - )下。然后,环路将通过将VCO调谐到更高的频率来尝试跟踪。但相对相位差仍然存在。因此,循环将继续尝试校正所测量的相位误差,直到VCO以其最高频率“固定”为止。注意,为了推广,可以根据相位差的极性将VCO调谐到更高或更低的频率。最重要的是,PFD可以看到导致失控状态的相位差。

实验

那么真实情况下发生了什么呢?考虑具有以下属性的项目计划:

-

标称带宽:100.000 Hz

-

快速锁定启用关闭

-

从Holdover退出

-

OOF IN0和IN1:

-

声明阈值100 ppm

-

断言阈值98 ppm

现在采取这样一个计划,并将其应用到2个Si5345评估板,如上图第二部分所示,除了使用IN1而不是IN3作为辅助或备用输入时钟。

将信号发生器应用到设备#1 IN0,并让两个电路板运行,直到HOLD_HIST_VALID为真。在IN0中删除100 MHz输入时钟时会发生什么?

最初只有LOS [0]由设备#1报告。否则一切都很好。但是,来自Device#2的输出时钟频率开始频率上升(通常可能会上升或下降,但是在我的实验中却正在上升)。

最后,设备#2的输出时钟作为备用输入时钟,远远超出了设备#1的OOF标准。结算条件如下:

-

设备#1进入保持模式

-

设备#2在锁定模式下运行。

请注意,一般来说,设备每个都在相反状态的时候可能无理由的不稳定。我们的经验是,大多数时候都有一些优先选择的状态,但是你会不时看到替代品,几乎就好像结果中都有一个混乱的元素。

在这种情况下,Ouroboros配置没有真正实现我们的任何东西,除了可能一点点。但是,请注意,输出频率在设备#1的OOF [1]断言并且设备#2仍然依赖于设备1 HO时钟的整个时间内上升。这对于这种不切实际的配置只是一个潜在的问题。但还有另一个可能更糟的效果。

Ouroboros振荡

这种配置还可以产生正反馈系统,可以使振荡,导致奇怪的行为。特别是,如果可以使其中一个设备进入退出HO,则可能会发生这种情况。例如,如果项目计划OOF规格如下收紧,则可以观察到这种现象。

-

OOF IN0和IN1:

-

声明阈值000 ppm

-

断言阈值9,375 ppm

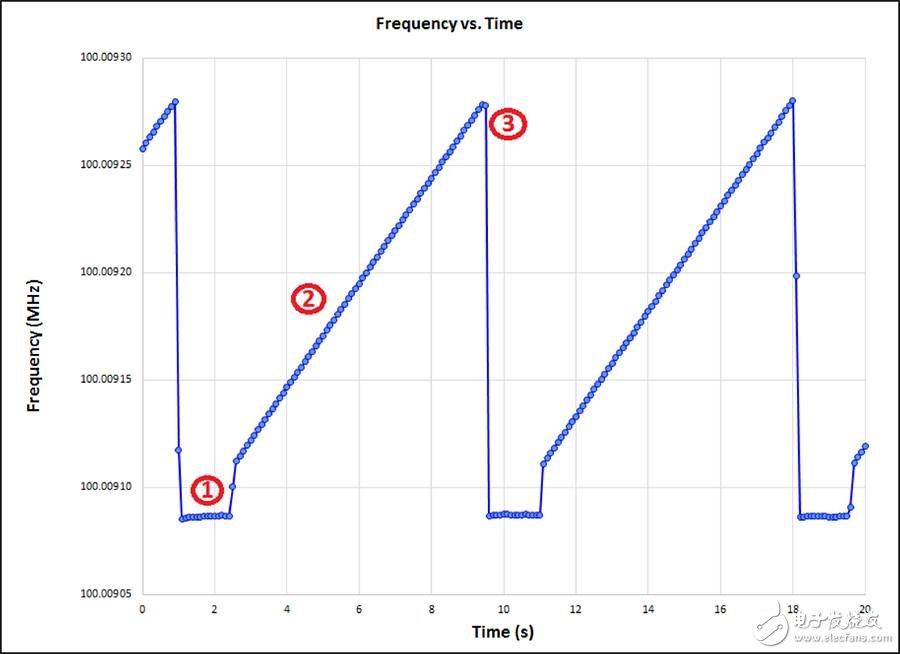

现在这两个设备将相互交互,可能永远不会解决。下面是Device#2输出时钟数据的频率图。您可以看到Device#2的输出频率在8或9秒的频率范围内慢慢振荡。

上面有关于设备#1的状态的三个功能,因为设备#2的输出频率有所不同:

1.器件#1处于保持或HO模式

2.装置#1从HO斜坡退出

3.设备#1正在进入HO

在此期间,设备#2不会发出报警。这个状态可以无限期地持续下去。我星期五下午开始试用这个实验,星期一早上还在运行。设备甚至可以根据哪个在HO状态交换角色!设备不断进入和离开HO甚至比直接进入HO更糟糕。

结论

底线是,Ouroboros时钟配置要么除了延迟进入HO没有任何用处,或者可以触发在输出时钟中产生重复漫游的振荡。下游时钟一般应保持下游。

-

抖动衰减时钟应用

+关注

关注

0文章

1浏览量

783

原文标题:秒懂时钟-抖动衰减时钟设计与应用技巧 – Part 2

文章出处:【微信号:SiliconLabs,微信公众号:Silicon Labs】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速ADC在低抖动采样时钟电路设计中的应用

Si5345和SI5344及SI5342系列抖动衰减时钟倍增器的数据手册免费下载

抖动衰减时钟设计与应用技巧资料下载

时钟电路设计之抖动衰减时钟设计与应用技巧

时钟电路设计之抖动衰减时钟设计与应用技巧

评论