从复杂的算法交易和交易前风险评估到实时市场数据传输,当今领先的交易公司、做市商、对冲基金、经纪商和交易所都在不断追求最低时延的交易执行,以获得竞争优势。

最快电子交易执行速度世界记录

AMD 与全球领先的高级交易和执行系统提供商 Exegy 合作,取得了创世界纪录的 STAC-T0 基准测试结果,实现了最低 13.9 纳秒 ( ns ) 的交易执行操作时延。相比此前的记录,这一结果可令 tick-to-trade 时延至多降低 49%,是迄今为止发布的最快 STAC-T0 基准测试结果1。此前的最高速度记录为 24.2 纳秒,同样来自采用 AMD 加速卡的参考设计1。

STAC 基准测试是业界用于测试高速时间序列报价数据分析解决方案的标准。STAC-T0 基准测试评估 tick-to-trade 网络 I/O 时延,即接收和执行交易订单所需的时间。

这项新的 AMD 和 Exegy STAC-T0 高精度时间戳基准记录采用 AMD Alveo UL3524 加速卡实现,AMD Alveo UL3524 加速卡是一款专为快速交易执行而设计的金融科技卡,由 AMD Virtex UltraScale+ FPGA 提供支持,在配备 AMD EPYC 7313 处理器的戴尔 PowerEdge R7525 服务器中的 Exegy nxFramework 和 Exegy nxTCP-UDP-10g-ULL IP 核上运行,并配备 Arista 7130 平台和 Arista MetaWatch 7130 设备。

AMD Alveo UL3524 加速卡具备突破性的收发器架构、78 万个 LUT 的 FPGA 架构以及 1,680 个 DSP 计算片。该产品旨在加速硬件中的自定义交易算法,交易者可以根据自定义算法和 AI 交易策略定制其设计。

“在超低时延交易中,1 纳秒即可决定交易的盈亏。这项基准测试展示了经过独立量化和验证的真实结果,展现了 AMD 如何从整体上推动高速交易和金融技术突破边界与可能性。”

—— Girish Malipeddi

产品营销总监

Exegy 提供了由必要的 FPGA IP 和相关软件组成的应用,以实现 Alveo UL3524 卡上的 STAC-T0 基准测试要求。

“通过完成此次最新 STAC-T0 基准测试,Exegy 和 AMD 很高兴能够创下 tick-to-trade 时延记录。今年的 STAC-T0 采用 Exegy 的 FPGA 开发框架和新的超低时延 TCP-UDP IP 协议栈,取得了迄今为止最出色的公开结果。”

—— Olivier Cousin

Exegy FPGA 解决方案总监

1.基于 AMD 和 Exegy 委托 Strategic Technology Analysis Center, LLC (STAC) 进行的第三方测试,2024 年 4 月。“Exegy nxFramework 和 Exegy IP Core nxTCP-UDP-10g-ULL 在搭载 AMD EPYC 7313 处理器的戴尔 PowerEdge R7525 服务器中的 AMD Alveo UL3524 FPGA 加速卡上运行。”测试系统配置:AMD Alveo UL3524 加速卡(由 AMD Virtex Ultrascale+ FPGA 驱动),运行 Exegy nxFramework 和 Exegy nxTCP-UDP-10g-ULL IP 核,安装在搭载 AMD EPYC 7313 处理器的戴尔 PowerEdge R7525 服务器上,搭配 Arista 7130 平台和 MetaWatch 7130 网关设备,运行 STAC-T0 基准测试。配置可能有所不同,进而产生不同的结果。

-

FPGA

+关注

关注

1630文章

21759浏览量

604361 -

amd

+关注

关注

25文章

5479浏览量

134310 -

加速卡

+关注

关注

1文章

60浏览量

10980

原文标题:AMD 创下 STAC 基准测试最快电子交易执行速度世界纪录

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

天合光能创造高效n型HJT电池组件效率世界纪录

MLCommons推出AI基准测试0.5版

隆基绿能HPBC 2.0组件效率破世界纪录

隆基绿能刷新光伏晶硅组件效率世界纪录

AMD 以全球极快的纤薄尺寸电子交易加速卡扩展 Alveo 产品组合,助力广泛且具性价比的服务器部署

AMD 以全球极快的纤薄尺寸电子交易加速卡扩展 Alveo 产品组合,助力广泛且具性价比的服务器部署

AMD推出新款纤薄尺寸电子交易加速卡

华为云图引擎服务GES震撼业界,刷新基准测试世界纪录

是德科技与AMD携手革新云与边缘基础设施性能基准测试

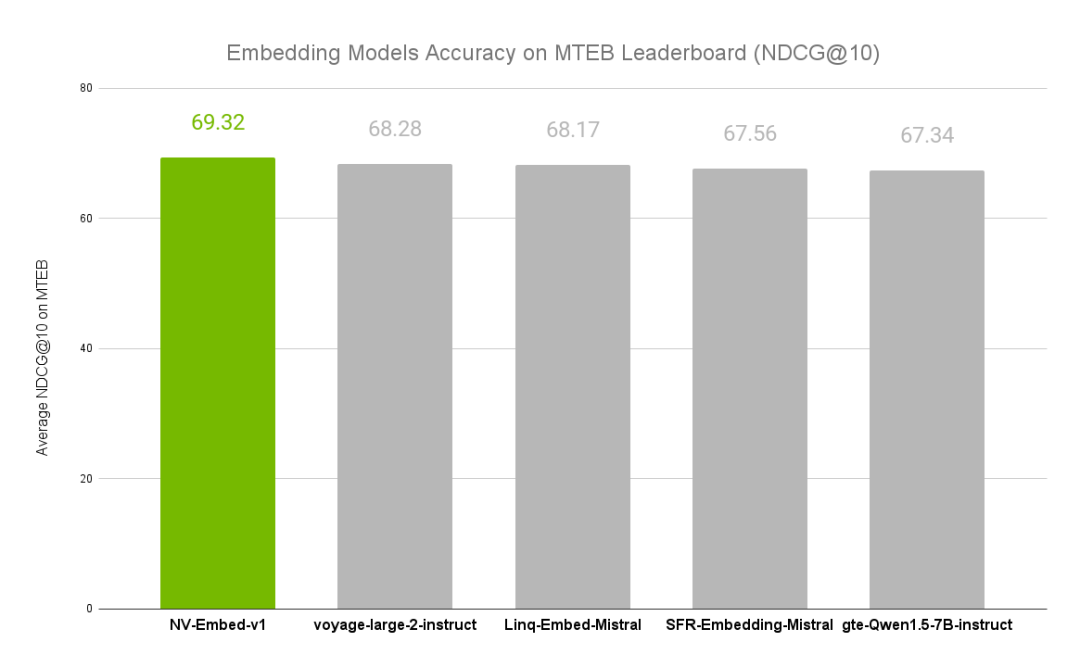

NVIDIA文本嵌入模型NV-Embed的精度基准

AMD创下STAC基准测试最快电子交易执行速度世界纪录

AMD创下STAC基准测试最快电子交易执行速度世界纪录

评论