从综合角度看,Vivado 2024.1对SystemVerilog和VHDL-2019的一些特性开始支持。先看SystemVerilog。

支持SystemVerilog AOI (Array of Instances)

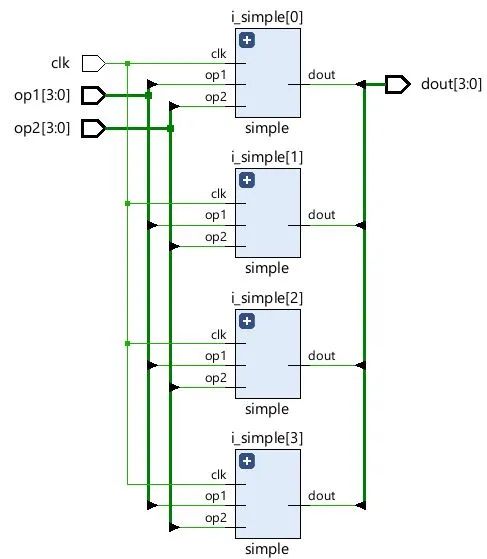

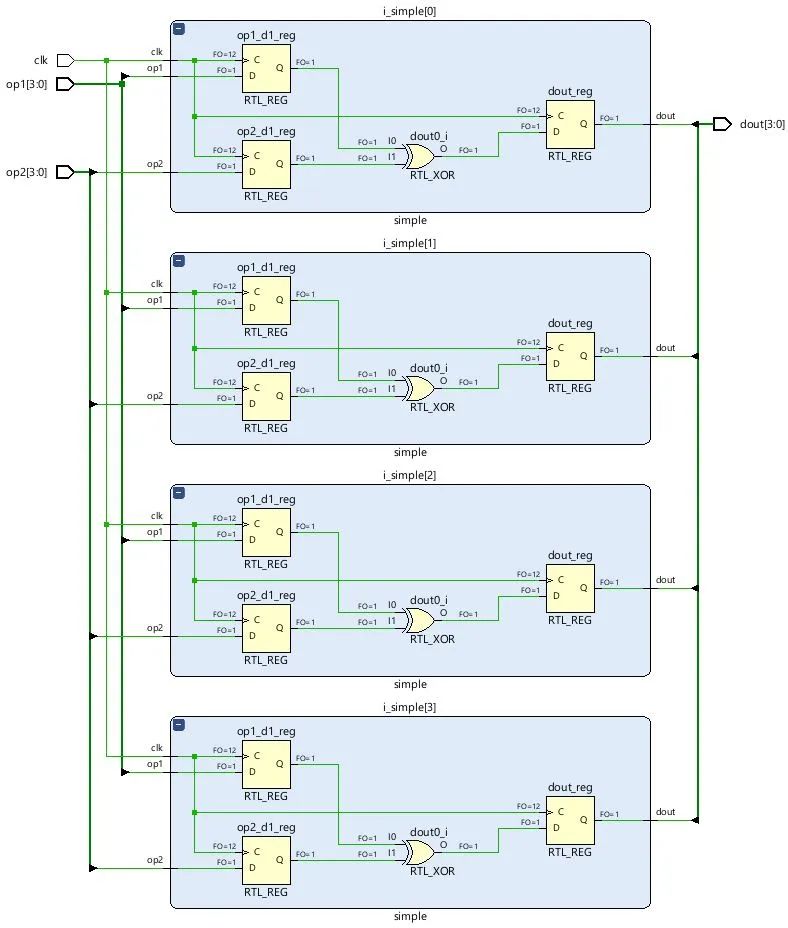

AOI指的是在实例化某个module时,可以将其声明为数组,这样就等效于同时声明了多个module,如下图所示。代码第8行对模块simple进行实例化,实例化名为i_simple[M-1:0],这里M等于4。实际上就等于实例化了4个simple,每个的实例化名分别为i_simple[0]~i_simple[3]。这样可以不用for generate语句。打开Elaborated Design视图可以看到其中的连接关系。

支持VHDL-2019引用端口属性的功能

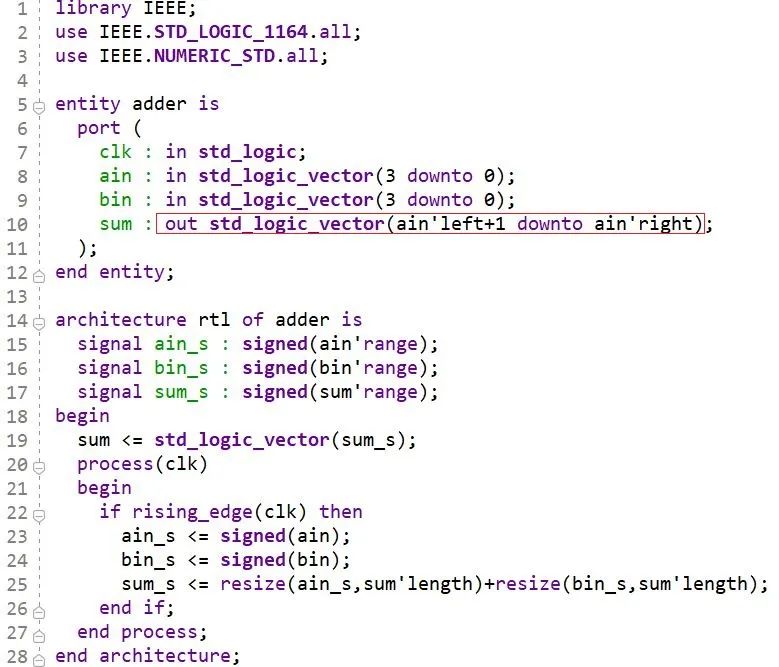

VHDL-2019支持在端口列表中引用端口属性。如下图所示代码片段,代码第10行声明端口sum时,对sum位宽的定义就引用了输入端口ain的属性left和right。其中ain’left返回值为3,ain’right返回值为0。同时还可以注意到第10行的末尾增添了分号。这也是VHDL-2019的新特性。之前的VHDL版本,由于端口列表中的最后一个端口声明不能加分号,导致端口列表声明不一致,VHDL-2019则解决了这一问题。但这个分号不是强制的,是可选的,即没有分号也同样是正确的。

支持VHDL-2019的多位宽端口部分互连功能

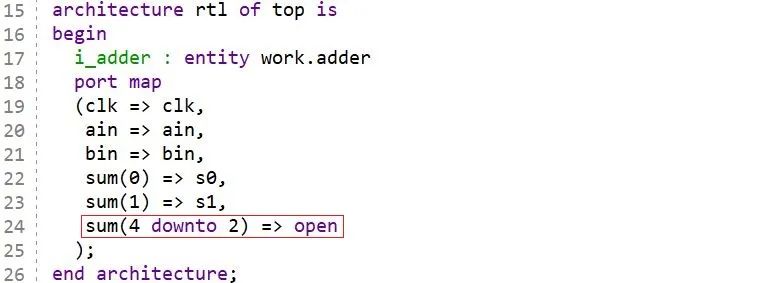

使用VHDL当对某个模块进行实例化时,若该模块某个输出端口未使用,需要声明为open状态。如果该端口是个多位宽的信号,某些位的数据需要连接到其他模块,某些位的数据不需要,那么VHDL-2019可以支持部分位的数据标记为open状态。如下图所示代码,代码第22行和第23行分别标记了sum(0)和sum(1)的连接关系,第24行则将sum(4 downto 2)标记为open状态。从代码风格角度看,该代码片段还体现了如何更好的实例化指定模块,如代码第17行所示,采用entity work的方式,这样的好处是不用在architecture中声明component,从而使代码更简洁。

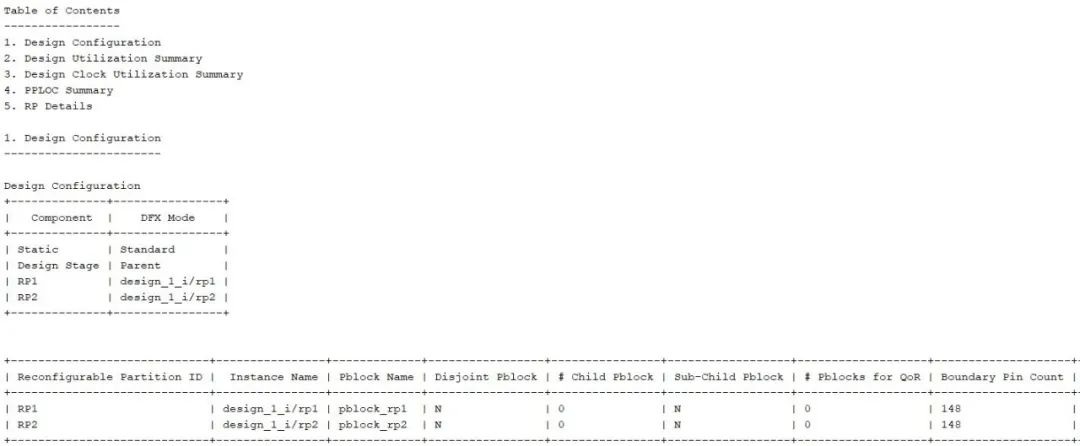

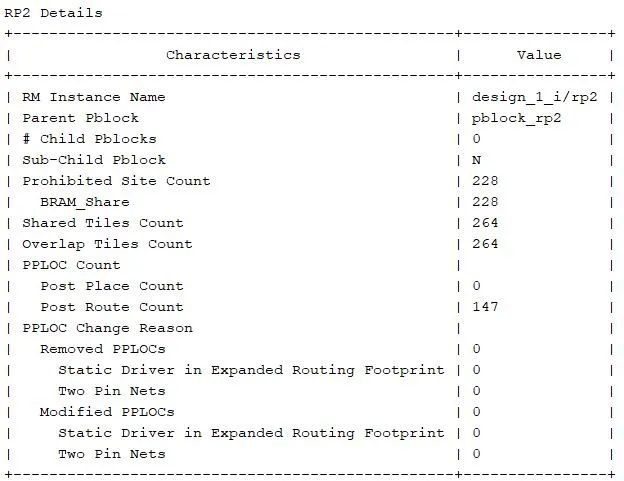

新增支持DFX的命令report_dfx_summary

新增命令report_dfx_summary,针对基于Versal器件的DFX设计。该命令会生成5个部分的内容,如下图所示。这对于DFX的分析会很有帮助。从该报告中可以看每个动态区的大小以及资源利用率、静态区的可用资源及资源利用率、时钟资源利用率以及PPLOC。除此之外,对于每个RP,还会显示RP的Pblock名称、共享的Tile等更具体的信息。

-

代码

+关注

关注

30文章

4857浏览量

69524 -

design

+关注

关注

0文章

159浏览量

45943 -

Vivado

+关注

关注

19文章

819浏览量

67256

原文标题:Vivado 2024.1有哪些新特性?(2)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

请问我可以免费更新Vivado版本到2016.1吗?

怎么将vivado12.3更新到最新的15.4版本?

Vivado Design Suite HLx 版本 2016.4 现已发布

Vivado Design Suite 2014.4.1 现已推出!

赛灵思Vivado设计套件推出2013.1版本,提供IP 集成器和高层次综合功能

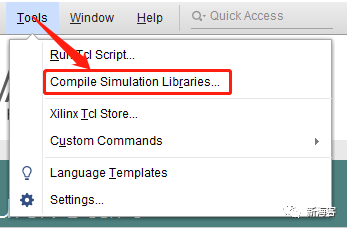

使用Vivado 2017调用Modelsim的详细步骤

如何使用Vivado 2022.1版本工具链实现ZCU102 USB启动(上)

Vivado Design Suite用户指南:版本说明、安装和许可

Vivado2018版本中Modelsim的配置

Vivado 2024.1版本的新特性(2)

Vivado 2024.1版本的新特性(2)

评论