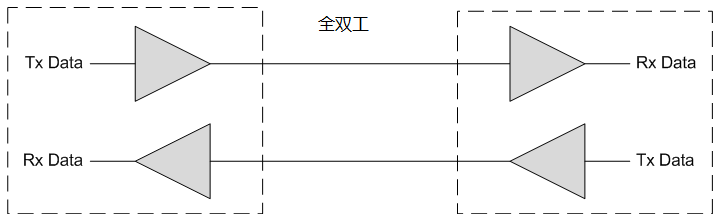

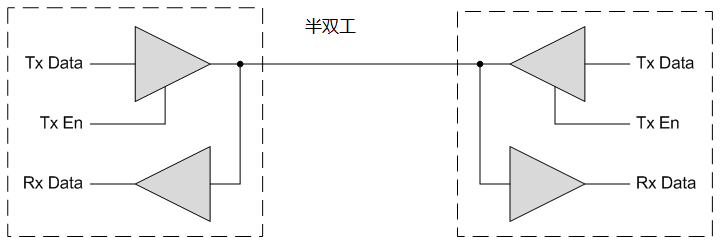

典型的全双工(Full Duplex)系统如下图所示,芯片1和芯片2之间有彼此独立的数据传输线,这意味着芯片1和芯片2可以同时给对方发送数据而不会发生冲突。SPI/UART采用的就是全双工通信方式。半双工系统则不同,芯片1和芯片2之间只有一条专用的且被彼此共享的数据传输线。这就要求芯片1和芯片2必须协商好,当前谁发送数据,谁接收数据。如果两者同时发送数据就会导致发送冲突,从而造成数据丢失。I2C采用的就是半双工通信方式。

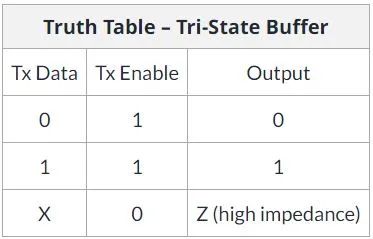

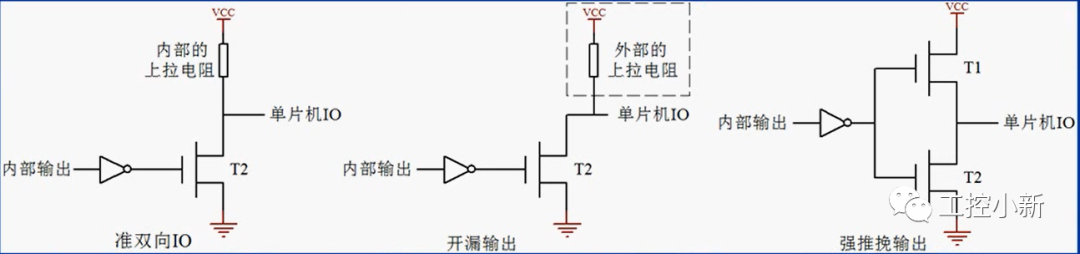

在上面两张图片中,其中的三角形代表输入/输出缓冲器(IBUF/OBUF),在半双工系统中,多了一个控制信号TxEn,该信号控制的是三态缓冲器。这里我们先看一下三态缓冲器的真值表,如下图所示。可以看到TxEn为1时三态缓冲器输出等于输入,为0时,输出为高阻。当芯片1和芯片2的TxEn均为高时,两者均会驱动数据传输线发送数据,造成冲突。这在半双工系统中是一定要避免的。

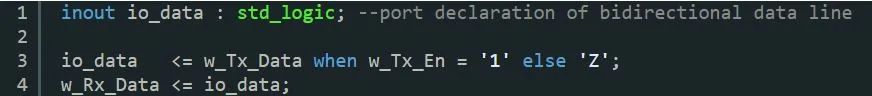

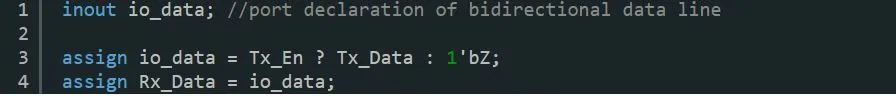

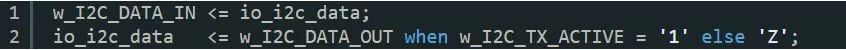

无论是VHDL还是Verilog/SystemVerilog,都提供了相应的语句描述三态缓冲器,而综合工具也可将其正确地推断出来。下面给出了三态缓冲器对应的VHDL代码和Verilog代码。其中io_data被声明为双向信号。需要注意的是尽管VHDL不区分大小写,但高阻态则必须用大写Z来表示,Verilog中大小写均可。

VHDL代码

Verilog/SystemVerilog代码

当前主流的FPGA结构中,三态缓冲器只存在于IOB(Input/Output Block)中。因此,对应的双向IO一定要放在设计的顶层、。如果在子模块中使用了三态缓冲器,如下图的I2C子模块,因为综合工具判断其出现在子模块中,所以会将三态缓冲器移除使其成为普通输出,从而造成功能错误。

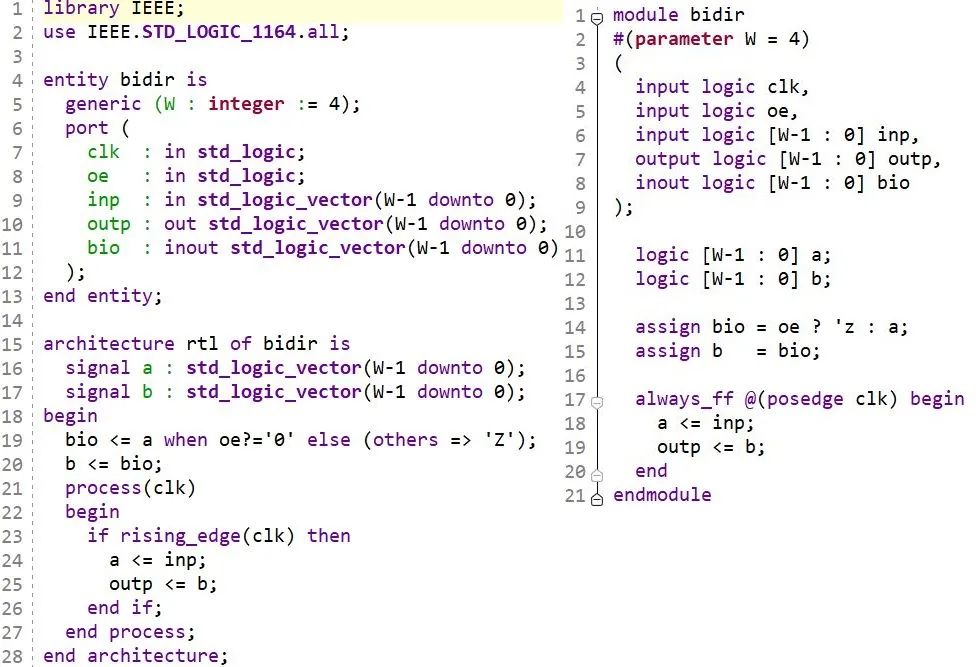

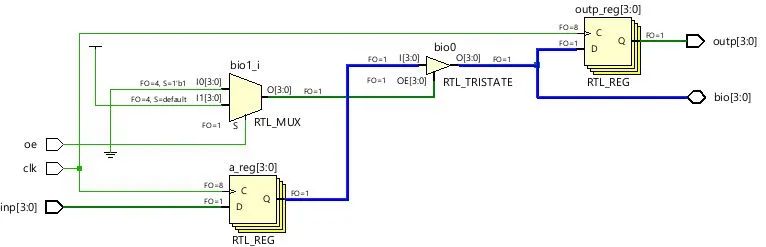

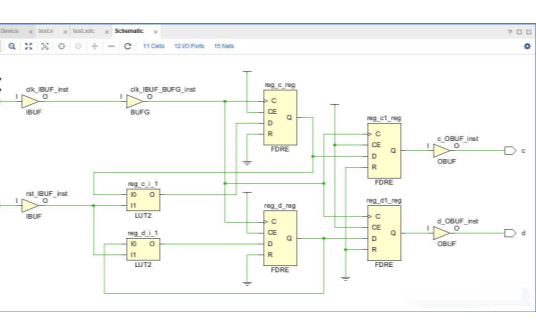

我们看一个案例,相应的VHDL代码和SystemVerilog代码如下图所示。双向端口bio均通过关键字inout定义。bio作为输入时和信号b相关,作为输出时和信号a相关。信号a由寄存器输出,信号b连接输出寄存器的输入端。这两组寄存器都可以放置在IOB内。

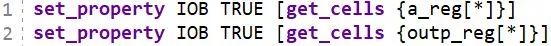

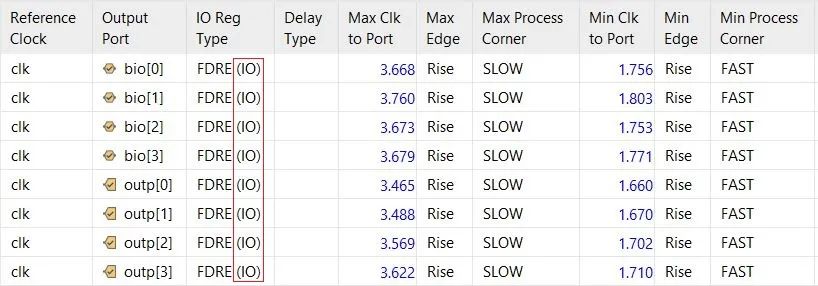

通过如下图所示约束可将这两组寄存器放置在IOB内,这里属性IOB的作用对象是通过命令get_cells获取的寄存器对象。通过命令report_datasheet可查看是否放置成功。如显示FDRE(IO)则说明该寄存器在IOB内。

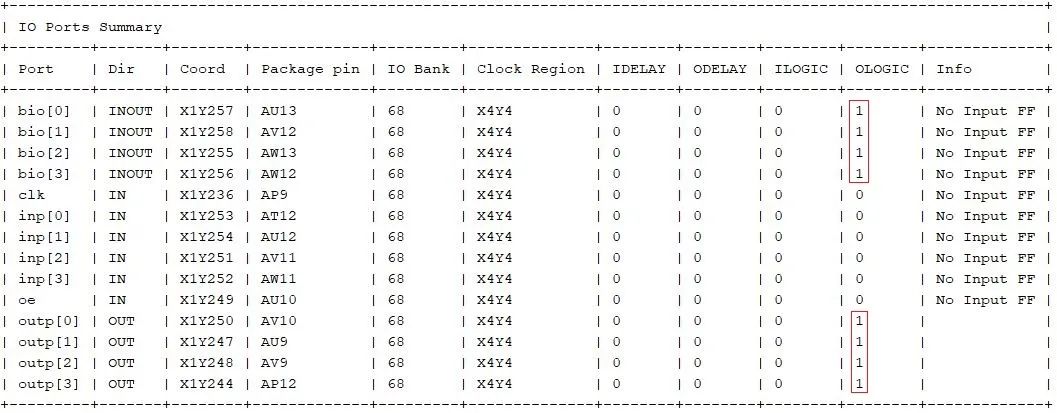

也可以通过report_io_reg查看寄存器是否在IOB内。

-

FPGA

+关注

关注

1625文章

21663浏览量

601666 -

芯片

+关注

关注

453文章

50360浏览量

421634 -

缓冲器

+关注

关注

6文章

1914浏览量

45445 -

Verilog

+关注

关注

28文章

1343浏览量

109970

原文标题:双向IO与IOB

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA中双向端口IO的研究

无法将符号组合到单个IOB中

DCM/IOB不合适

IOB / BUFGCTRL时钟元件对发生错误

不兼容的IOB被锁定到同一个银行11冲突的IO标准是什么

stm32单片机准双向IO口配置介绍

一文详解Spartan-6系列IO Tile结构

《Linux设备驱动开发详解》第9章、Linux设备驱动中的异步通知与异步IO

FPGA中IOB寄存器的使用教程详细说明

FPGA中IOB寄存器的使用心得

xilinx FPGA的IOB使用教程说明

关于stm32单片机准双向IO口配置

双向IO与IOB详解

双向IO与IOB详解

评论