失效分析最常观察到的现象是EOS过电失效,分为过压失效及过流失效的两种失效模式。对于以功率器件为代表的EOS过电失效样品,其失效表征往往表现为芯片的大面积熔融,导致难以进一步判定其失效模式。

本文以常规MOS、IGBT场效应管为例,从芯片内部结构进行分析和明确过压击穿容易出现的失效位置及机理解释。

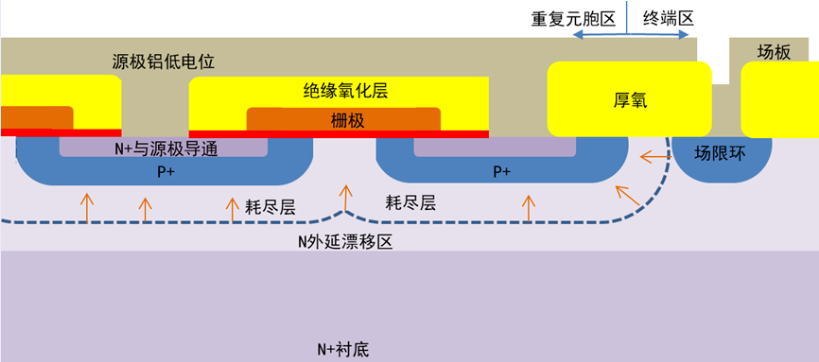

承压结构分析根据芯片结构图示,可见芯片关闭时,承受偏压的结构主要包括栅氧、PN交界面(橙色箭头分布区域)。

不同承压位置分析

元胞区栅氧与PN交界面耐压分析分析

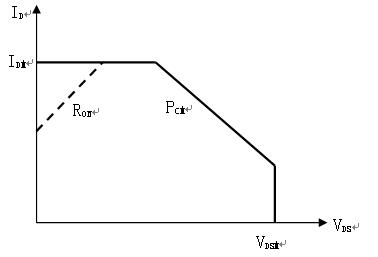

单个元胞,可见承压主要由N-区耗尽层承担。耗尽层的存在,使得电压被均匀分担到该面积区域内。

实物芯片均由以上单个元胞(四方形、六角形、长条形等)重复排列组成,因此只要相邻P区足够近,耐压导致的耗尽层就会重叠,最终表现为整个元胞区耗尽层底面近似平面。耗尽层将栅氧、PN交界面包覆在内,承压主要由耗尽层实现。

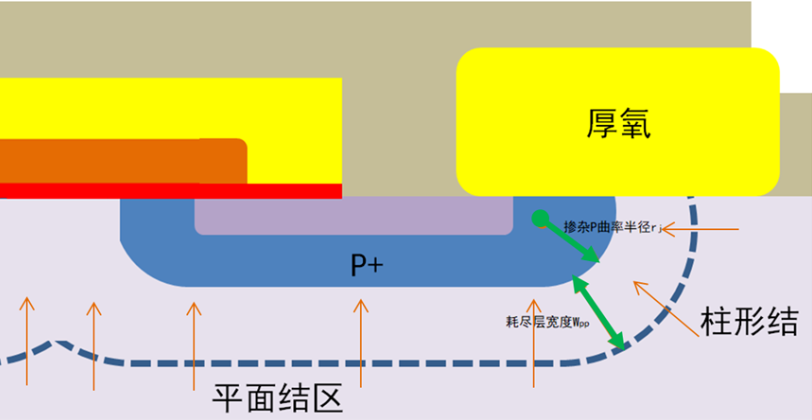

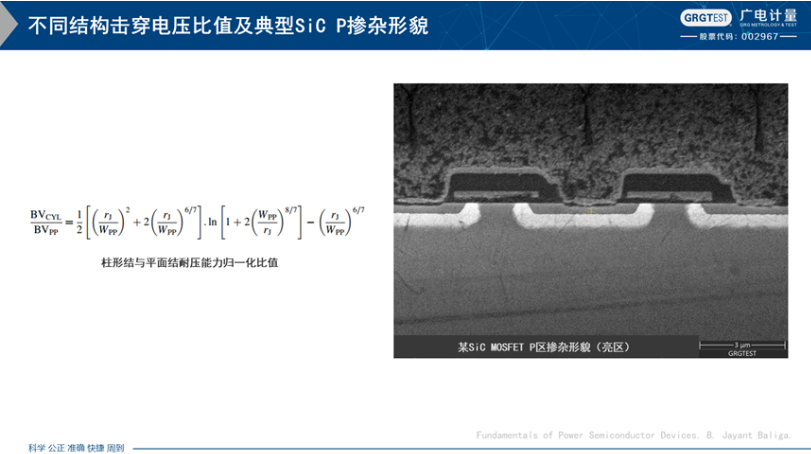

元胞区平面结与终端柱形结耐压分析

芯片最终耐压考量转化为元胞耗尽层平面(平面结)与终端耗尽层曲面(柱形结)耐压能力的对比。

目前业内针对耗尽层耐压能力的研究,主要借助泊松方程推算,最终得到耐压与曲率半径、耗尽层宽度的关系式。由于耗尽层宽度远高于曲率半径,因此算得柱形结耐压强度远低于平面结。(Fundamentals of Power Semiconductor Devices. B. Jayant Baliga.P107~111)从常理也不难理解,侧面P掺杂主要为向下掺杂的副产物,其厚度及浓度均较低,对应感应产生的耗尽层抗压能力会弱很多。

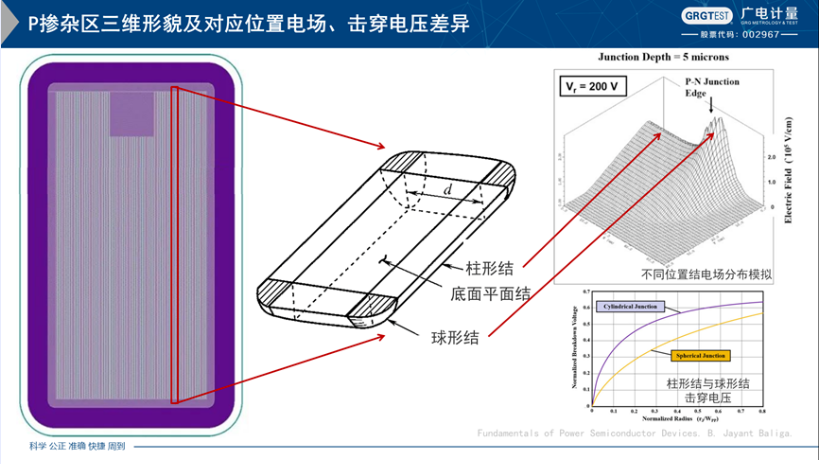

终端柱形结与球形结耐压分析

扩展到三维结构,还需考虑P区掺杂两个柱形结相交球形结。与柱形结同理,球形结位置对应击穿电压会更低。并且无论单个元胞形状如何设计(四方形、六角形、长条型等),只要距离够近其内部掺杂区耗尽层均会重叠,最终均表现为最外围球形结及耗尽层耐压最差。

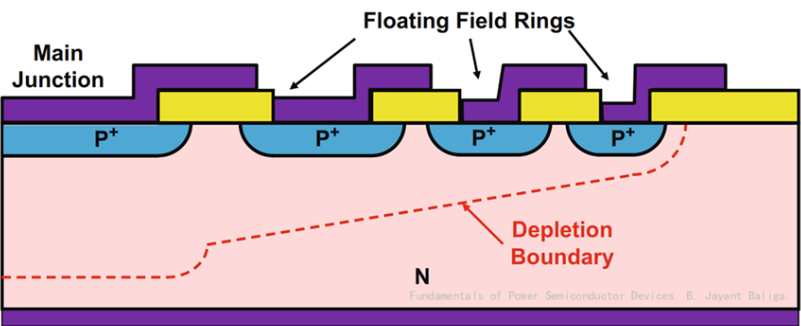

终端区场限环分析

针对此问题,业内普遍选用场限环+场板的工艺结构,进一步延伸终端耗尽层的分布区域,从而达到尽可能扩大承压面积的目的。因此场限环的宽度、间距、数量成为决定器件耐压的主要影响因素,也是各家产品设计重点关注方向。

总结

综合以上分别对元胞区栅氧、PN交界面,耗尽区平面结、柱形结、球形结,终端区场限环的结构、位置原理分析,可以明确芯片耐压最脆弱位置往往表现在源区边缘,特别是转角位置。失效现象表现为较小面积的烧蚀黑点。

广电计量服务能力

广电计量在功率晶体管领域积累了丰富的失效机理及对应失效表现分析经验,包括但不限于:封装失效类别及表现、电压击穿机理及表现、电流烧蚀机理及表现、栅氧缺陷机理及表现、动态/静态闩锁机理及表现、雪崩击穿机理及表现、二次击穿机理及表现、辐照失效机理及表现,协助客户从半导体基础原理深入分析其失效机理。

-

场效应管

+关注

关注

47文章

1171浏览量

64229 -

MOS

+关注

关注

32文章

1283浏览量

94280 -

失效机理

+关注

关注

2文章

27浏览量

11678 -

失效分析

+关注

关注

18文章

219浏览量

66477 -

EOS

+关注

关注

0文章

124浏览量

21245

发布评论请先 登录

相关推荐

场效应管的分类

功率场效应管(MOSFET)的结构,工作原理及应用

【下载】《射频微波功率场效应管的建模与特征》

功率场效应管(VMOS)的结构原理

VMOS场效应管介绍及应用

VMOS场效应管的检测方法

广电计量|功率场效应管过压失效机理及典型特征分析

广电计量|功率场效应管过压失效机理及典型特征分析

评论