共读好书

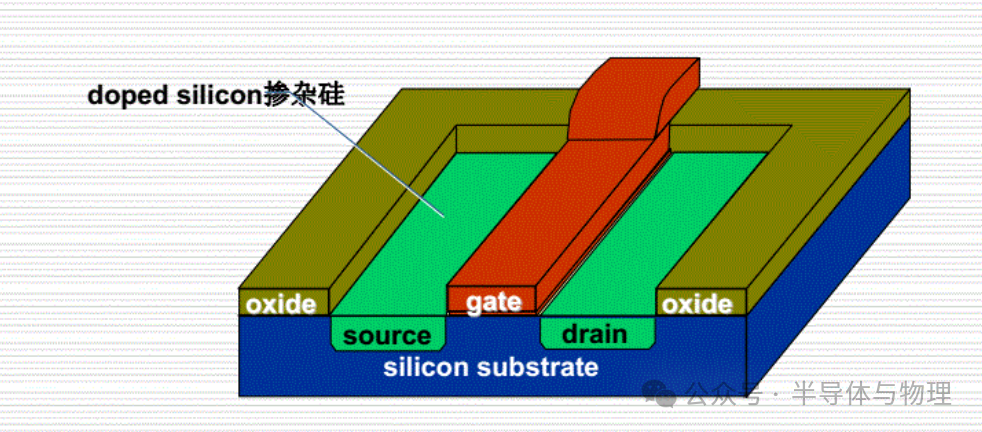

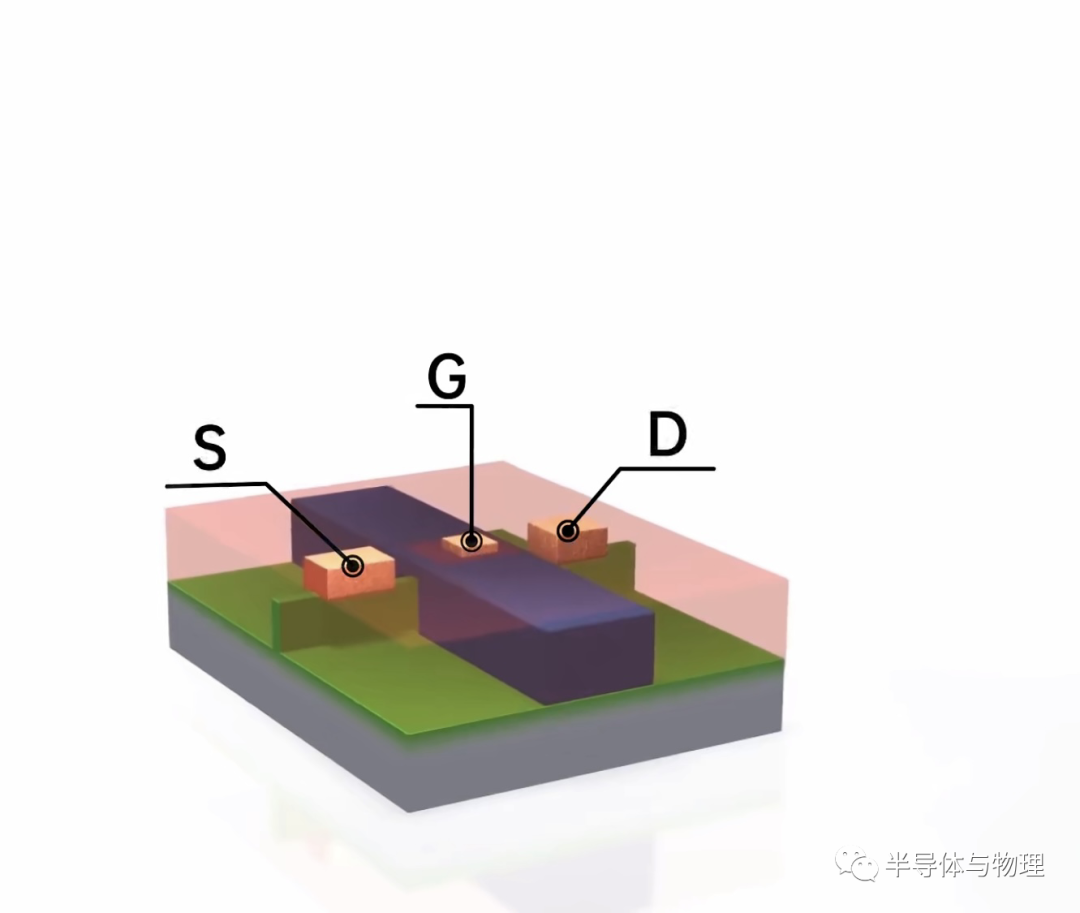

芯片制造工艺流程包括光刻、刻蚀、扩散、薄膜、离子注入、化学机械研磨、清洗等等,在前面的文章我们简要的介绍了各个工艺流程的细节,这篇文章大致讲解这些工艺流程是如何按顺序整合在一起并且制造出一个MOSFET的。

1.我们首先拥有一个硅纯度高达99.9999999%的衬底。

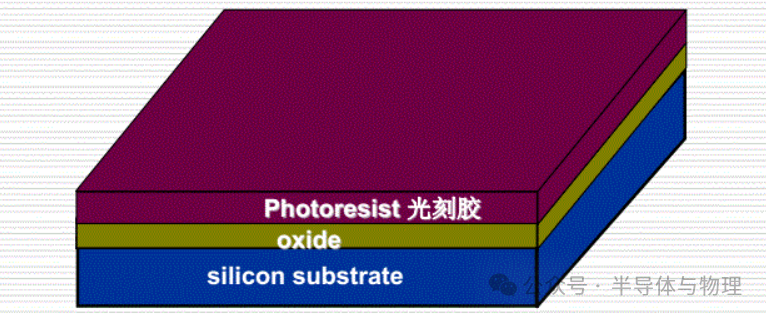

2.在硅晶衬底上生长一层氧化薄膜。

3.均匀的旋涂上光刻胶。

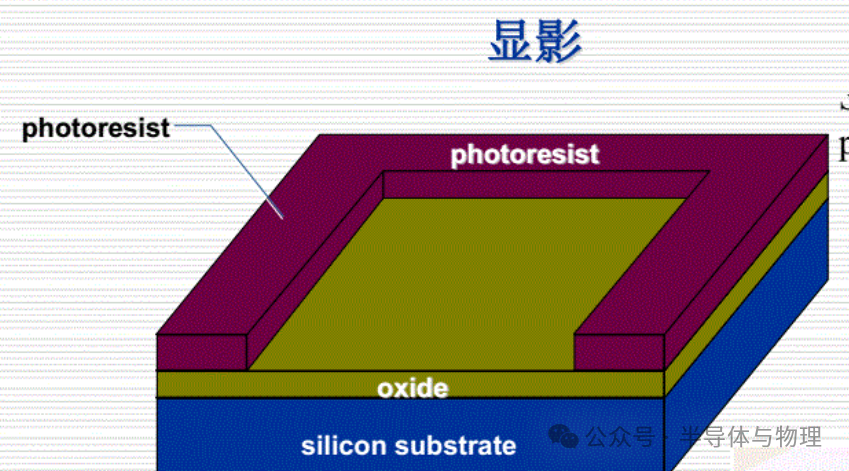

3.通过光掩膜进行光刻,把光掩膜板上的图案转移到光刻胶上

4.感光区域的光刻胶显影之后被清洗掉。

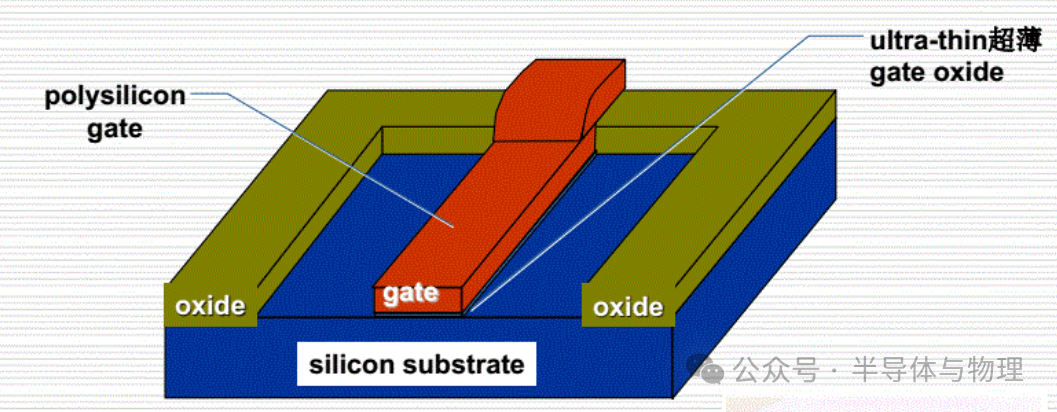

5.通过刻蚀把没有被覆盖光刻胶的氧化薄膜刻蚀掉,这样把光刻图案转移到晶圆上了。

6.清洗去掉多余的光刻胶。

7.再长一层较薄的氧化膜。之后再通过上面的光刻和刻蚀,只保留栅极区域的氧化膜。

8.在上面生长一层多晶硅

9.和第7步一样通过光刻和刻蚀,只保留栅氧化层上面的多晶硅。

10.在进行光刻清洗覆盖住氧化层和栅极,这样就对整片晶圆进行离子注入,就有了源极和漏极。

11,在晶圆上面生长一层绝缘薄膜。

12.通过光刻和刻蚀把源极、栅极和漏极的接触孔刻蚀出来。

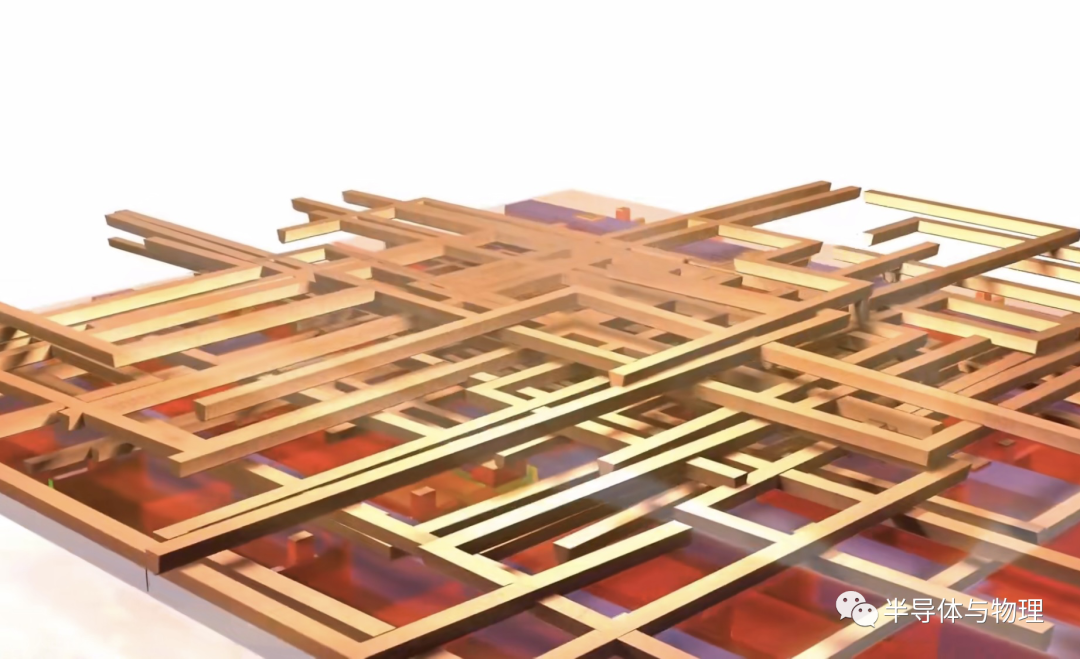

13.再在刻蚀的地方进行金属的沉积,这样就有了源极、栅极和漏极的导电金属线了。

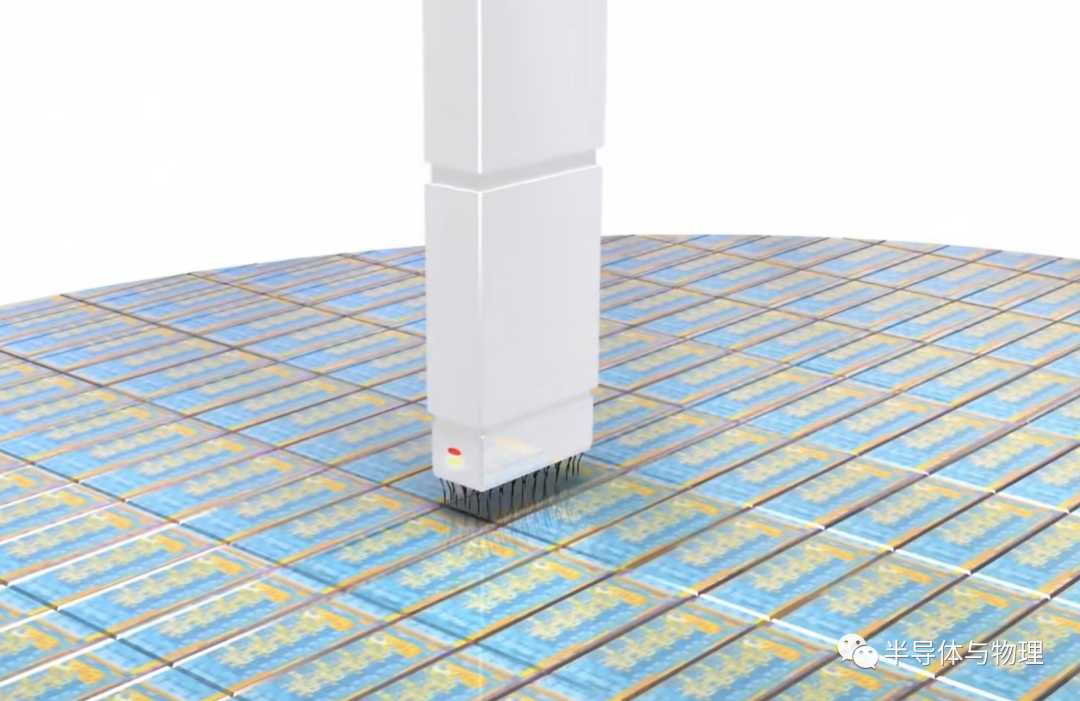

最后通过各种工艺的组合就制造出来一个完整的MOSFET。

------------------------------------------------------------------------

金刚石/GaN 异质外延与键合技术研究进展

吴海平 安康 许光宇 张亚琛 李利军 张永康 李鸿 张旭芳 刘峰斌 李成明

(北方工业大学 机械与材料工程学院 北京科技大学 新材料技术研究院)

摘要:

氮化镓(GaN)功率器件具有功率高、小型化的优势,但散热问题已经成为限制其高功率输出的新问题。金刚石具有块体材料最高的热导率,是GaN功率器件的理想散热材料,将金刚石与GaN功率器件集成,可以降低器件运行温度,提高功率密度,推进器件小型化发展。但是由于金刚石与GaN存在大的热膨胀失配和晶格失配,以及金刚石的高硬度和稳定的化学性质,其与GaN集成存在很多问题,无法发挥金刚石的超高热导率优势。针对金刚石与GaN的集成已经进行了研究与探索,主要包括GaN功率器件的器件层散热和衬底层散热。器件层散热主要有金刚石钝化散热技术,其在GaN器件层中异质外延金刚石散热层;衬底层散热主要有键合技术、异质外延技术,其中键合技术通常需要在金刚石和GaN表面沉积键合层或形成封端,包括表面活化键合技术、亲水键合技术、原子扩散键合技术和水解辅助固化键合技术等;异质外延技术通常需要在外延表面沉积缓冲层,包括金刚石异质外延GaN技术和GaN底面异质外延金刚石技术。详细介绍了GaN材料的优势和应用领域及面临的挑战,对上述集成技术的研究现状和优缺点进行了归纳,展望了金刚石与GaN功率器件集成技术的未来发展方向。

1.引言

GaN作为第三代半导体材料的典型代表,与Si、Ge、GaAs、InP等第一、二代半导体材料相比,在禁带宽度、击穿场强、电子迁移率、热导率、最高工作温度等关键性能上更具优势[1]。使用GaN材料制造的GaN功率器件拥有高转换效率、低导通损耗、高工作频率、大带宽以及高功率密度[2],广泛应用于通信、雷达、卫星、电力电子等领域[3-4]。

随着系统小型化的发展,需要进一步提高GaN功率器件的功率密度,但是GaN功率器件工作时,本身会产生一定的功率耗散,而这部分功率耗散将会在器件内部,尤其是在导电沟道处产生大量热量使得器件结温有明显升高,晶格振动散射大大加强使得漂移区内的电子迁移率降低,器件导通电阻出现明显上升,这种现象被称作“自热效应”。姜守高等[5]发现GaN基HEMT器件在200℃存储300小时后,其饱和电流降低9.05%,最大跨导降低5.3%,因此散热问题越来越重要[6-7]。如何实现有效的散热以减弱自热效应的影响,成为高功率密度GaN功率器件保持高可靠性和长寿命的挑战[8-13]。

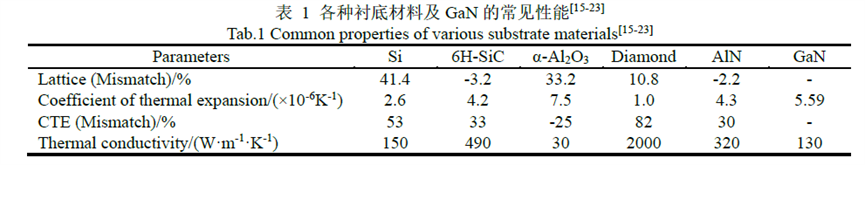

目前GaN材料通常使用外延法制备[14],衬底使用Si、SiC、Al2O3、AlN、GaN等材料[15-17],其热导率如表1所示,无法发挥GaN器件高频率、高功率密度的优势[18-23]。金刚石是块体材料中热导率最高的材料,单晶金刚石在室温下的导热系数高达2400 W·m-1·K-1[24],多晶金刚石热导率也达到了2000 W·m-1·K-1 [25],远高于其他常用GaN衬底材料的热导率,是理想的散热材料[26]。将高热导率的金刚石与GaN功率器件集成,凭借金刚石的超高热导率,热源产生的热量会迅速地横向扩散在基板内,提升了热源与外界的有效换热面积,从而可以极大地提升系统的换热能力,大幅度提高GaN功率器件的散热效果,降低器件沟道温度,从而提高GaN功率器件的工作功率密度[27]。本文对近年来金刚石与GaN集成技术的发展进行了介绍,详细阐述了各种技术的设计方案、工艺流程、优缺点及应用范围,并对未来金刚石与GaN功率器件集成技术的发展方向进行了分析和展望。

2.金刚石/GaN集成技术研究现状

目前金刚石与GaN功率器件的集成通常从两方面进行,一是GaN顶部的器件层散热,主要应用金刚石钝化散热技术,金刚石钝化散热是直接在器件顶部沉积金刚石,提高热点顶部的热扩散,同时起到增大换热面积的作用;二是GaN底部金刚石衬底散热,主要有GaN底部异质外延金刚石、金刚石表面异质外延GaN和键合技术[28-30]。

2018年,美国Akash Systems公司[31]开发出金刚石基GaN,用于卫星功率放大器,相比SiC基GaN,其工作温度从232℃降低到152℃,功率密度提升3.6倍以上。2019年,搭载该金刚石基GaN功率器件的卫星已成功发射,得益于金刚石的高导热率,GaN的高功率高频率优势得以发挥,卫星的数据传输速率达到了14 Gbps。2019年,日本富士通公司[32]报道了一种金刚石-GaN-金刚石的双层金刚石散热结构,如图1所示,结合了金刚石钝化散热技术与金刚石衬底散热技术,经测试,该结构具有优异的散热性能,热点温度较无金刚石的结构下降了77%。

2.1金刚石/GaN键合技术

金刚石/GaN键合技术的技术路线通常是将GaN外延层的原始衬底通过机械研磨,化学蚀刻等方法去除,然后在GaN暴露的底面通过磁控溅射、金属有机化学气相沉积(MOCVD)等方法沉积中间层,之后与金刚石结合。该技术存在的难点是对金刚石的表面粗糙度、弯曲度要求极高,还存在键合强度低,键合层热阻高等问题。目前金刚石表面加工方法主要有机械抛光、化学抛光、等离子体辅助抛光、激光抛光等[33-34],例如Yamamura等[35]使用等离子体辅助抛光获得了粗糙度Sq 0.13 nm的单晶金刚石片,杨志亮等[36]使用机械研磨抛光,得到了粗糙度0.27 nm、弯曲度13.84μm的3英寸多晶金刚石片,但是成本都比较高。根据键合层处理方法与材料的不同,目前常用的键合技术有表面活化键合、亲水键合、原子扩散键合、水解辅助固化键合等。

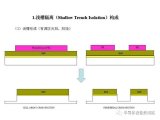

2.1.1金刚石/GaN表面活化键合技术

表面活化键合通常使用Si、SiC等能与金刚石形成稳定化学键的非金属材料作为键合层,基本流程如图2所示,首先通过粘片工艺将GaN固定到载片上,之后去除原始衬底,在待键合面沉积键合层或使用离子束活化待键合表面,最后将键合表面贴合并加压完成键合。由于需要保持待键合表面活性,避免氧化或污染,沉积键合层或离子束活化表面步骤与键合步骤需要在高真空度环境(~5×10-6 Pa)中进行,对设备条件要求很高。

由于键合层通常是非晶态材料,热导率较低,Cheng等[37]为了探究键合层厚度对界面热导的影响,制备了不同键合层厚度的金刚石/GaN结构,分别为13 nm和4.2 nm,并使用时域热反射技术测量界面热导,分别为53 MW·m-2·K-1和92 MW·m-2·K-1,可以看出,键合层厚度与热导率有强相关性,减小键合层厚度对整体热阻的控制十分重要。

为了减小键合层厚度或使键合层转变成晶态材料,有研究人员使用高温退火的方式,使键合层发生扩散、化学反应等。Kagawa等[38-39]使用Si作为中间层, 制备了AlGaN/GaN/3C-SiC/金刚石结构,在800℃退火后,形成欧姆接触,键合结构稳定,得到完整GaN HEMT器件。如图3所示,在1100℃退火后,键合层中Si和C原子发生再结晶生成SiC,厚度从退火前的15.5 nm减小到7.4 nm,且在高温退火过程中键合层拉应力也有所减小。在VGS=2 V,VDS=20 V时,相比于Si和SiC衬底,使用金刚石衬底的器件最高温度分别降低57%和43%,器件电性能也有所提高。Liang等[40]报道了仅通过Ar离子束照射金刚石和GaN表面,不使用其它材料作为键合层的方法制备了金刚石/GaN结构,其中有5.3 nm厚的非晶碳中间层。在700℃、1000℃退火后非晶碳中间层厚度分别减小到2.3 nm和1.5 nm,在其中观察到晶格条纹,部分转化为金刚石。这些研究都表明通过优化退火工艺可以减小甚至完全去除键合层,且键合结构稳定。

为了进一步减小键合层厚度,Matsumae等[41]优化工艺,使用Ar离子束照射Si靶,在金刚石上沉积1 nm厚的Si层,GaN表面使用Ar离子束轰击活化,在4.4 MPa的压力下与GaN成功键合,键合层厚度仅1.5 nm,剪切强度4.5 MPa,如图4所示。推测界面热阻小于10 m2·K·GW-1。相比Liang等[40]的工艺,这个工艺没有高温退火的过程,减小了对GaN层的损伤。

金刚石表面粗糙度控制对键合成功率也十分重要,但是由于金刚石的高硬度、高化学

惰性,将其加工到0.5 nm以下成本很高,有研究人员发现在沉积键合层的过程中,可以降低金刚石键合面粗糙度。Kobayashi等[42]使用射频磁控溅射在金刚石键合面沉积15 nm SiC层,使金刚石键合面粗糙度由0.768 nm降低到0.365 nm,而后在表面活化键合设备中室温键合,成功制备了金刚石/GaN结构,键合面积85%,键合层厚度11 nm,其中3.7 nm为缺陷金刚石层,7 nm为非晶SiC层。在1000℃退火后,由于硅与碳原子反应生成SiC,SiC层厚度略有增加,非晶SiC层在退火工艺之后变成多晶。结果表明,SiC层的沉积可以降低金刚石表面的粗糙度,并有利于多晶金刚石与异种材料的室温结合,通过退火工艺,还可以将低热导率的非晶SiC转变成高热导率的多晶SiC。

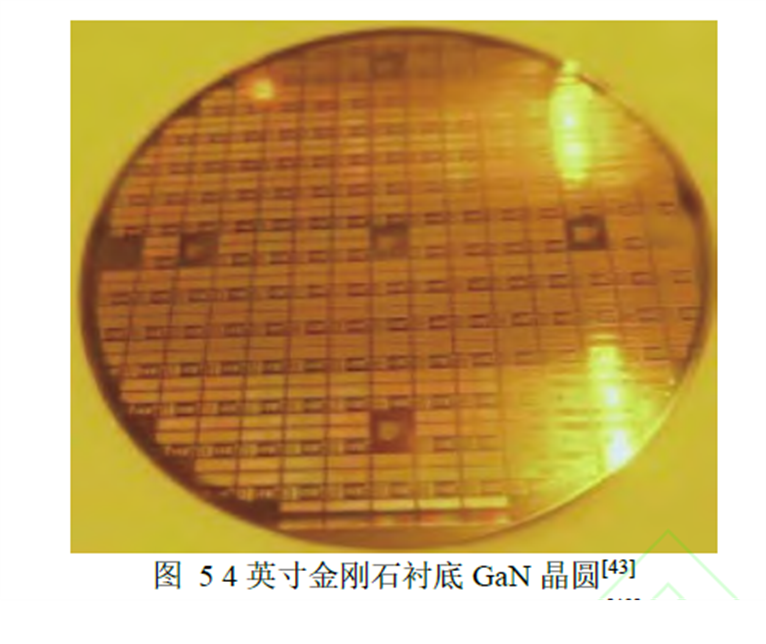

目前的研究大多处于小尺寸探索阶段,针对大面积键合的工艺优化和实验验证,廖龙忠等[43]使用纳米级氧化硅作为键合层,使用优化的键合工艺,成功实现了4英寸金刚石与GaN的键合,如图5所示。所制备的金刚石/GaN器件热阻较转移前降低了39.5%,在6.5 W总耗散功率下其结温降低了33.77℃,电气性能经测试也有提高。实现了大尺寸金刚石与GaN的键合,验证了大尺寸键合的可行性,为产业化提供了依据。

2.1.2金刚石/GaN亲水键合技术

亲水键合是在金刚石和GaN表面生成OH端,通过OH端之间的反应实现金刚石与GaN的键合,目前已广泛应用于金刚石与Si、SiO2、InP,InGaP,Ga2O3等材料的键合[44-47]。Matsumae等[48]使用NH4OH/H2O2混合溶液在70℃下处理金刚石,使用HCl溶液在70℃下处理GaN,在金刚石和GaN表面成功生成了OH端,后将金刚石与GaN在1 MPa的压力下200℃处理2小时,成功得到金刚石/GaN结构,如图6所示。剪切强度8.19 MPa,有3nm由sp2-C、Ga和O组成的键合层。亲水键合的方法相对于表面活化键合,步骤简单,对设备要求低,但是OH端反应产物包括大量高温水分子,在大尺寸键合过程中可能无法及时逸出,影响键合效果,且据Sumiya等[49]报道,高温水蒸气会对GaN产生不利影响。

2.1.3金刚石/GaN原子扩散键合技术

原子扩散键合技术使用Au、Mo、Ag、Cu等金属材料作为键合层,利用金属原子在温度和压力下的扩散实现键合,已经应用于金刚石与Si、GaN与Si的键合[50-51]。Wang等[52]在单晶金刚石、多晶金刚石和GaN上沉积5 nm Mo层和11 nm Au层,在室温下加载2000N的载荷完成键合,制作了单晶金刚石/GaN和多晶金刚石/GaN两个样品。单晶金刚石与GaN完全键合,在680 N的拉力下,样品从Au-Au键合层断裂。多晶金刚石键合面积98.5%,经过45℃到125℃的1000次热循环后,键合面积降低到73%,如图7所示。使用原子扩散键合成功制备了金刚石/GaN结构,但是由于金属材料与金刚石和GaN之间热膨胀系数失配很大,导致其热稳定性较差,且并未报道金属键合层厚度、热导率以及金属层对GaN器件电气性能的影响。

2.1.4金刚石/GaN水解辅助固化键合技术

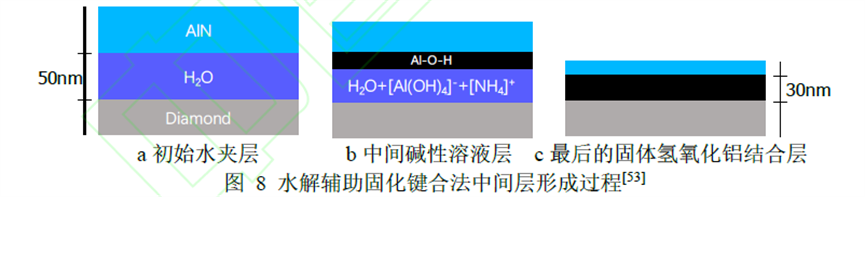

水解辅助固化键合是一种利用中间层发生化学反应来进行键合的方法。Gerrer等[53]在Si基AlN/AlGaN/GaN上黏贴一块650μm厚的蓝宝石,而后放入HNO3/HF混合溶液中去除Si层,后在去离子水中将AlN/AlGaN/GaN的AlN面与金刚石接触,旋转去除接触面多余的水,放入真空炉中在200℃完成键合,去除蓝宝石片后得到金刚石/AlGaN/GaN结构。在键合过程中,键合层是通过AlN与水在40℃以上温度反应形成的,生成物为Al(OH)3和AlO(OH),键合层厚度30 nm,如图8所示。整个工艺流程都是在液体中进行的,工艺简单,对金刚石粗糙度要求较低,但是键合层材料导热率极低,且厚度难以控制,导致其热阻高,据Fatimah等[54]报道Al的氢氧化合物可以在高温下分解成热导率更高的Al2O3,后续可以开发其它高热导率的键合层材料或通过高温退火等方法提高键合层热导率。

2.2金刚石异质外延GaN技术

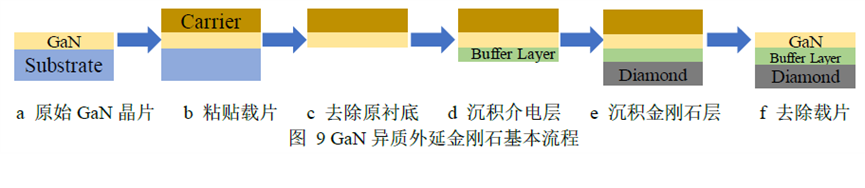

另一种金刚石衬底散热技术是异质外延技术,由于金刚石是立方晶体结构,不同于GaN的纤锌矿晶体结构,GaN和金刚石之间存在很大的晶格失配和热膨胀系数失配,如表1所示,给异质外延技术带来了许多难题,如何有效控制应力以及生长的晶体质量都是其中的关键问题。按照外延层的区别可以分为GaN异质外延金刚石技术和金刚石异质外延GaN技术。GaN异质外延金刚石技术,是在去除GaN原衬底及部分缓冲层后,先在GaN背面沉积一层介电层用于保护GaN,而后再沉积金刚石层;金刚石异质外延GaN技术,是在金刚石上直接使用分子束外延(MBE)、MOCVD等方法沉积GaN层。目前研究使用较多的异质外延技术是GaN异质外延金刚石技术。

GaN异质外延金刚石技术相比键合技术,界面结合强度高,成本较低,但是也存在一些问题,如异质外延金刚石的形核层质量差、热导率低,金刚石的生长环境通常都是高温、高氢等离子体密度,GaN在高温冷却到室温的过程中会发生翘曲甚至破裂,在氢等离子体环境中会发生严重的刻蚀、分解[55-59]。因此需要在GaN表面先制备一层保护层,缓解热应力,同时保护GaN不受刻蚀。技术基本流程如图9所示。

Field等[60]研究了保护层对金刚石/GaN结构的影响,比较了具有SiC保护层和没有保护层的两种样品的形貌特征和热导率。从结果来看,没有保护层的样品结合面粗糙,GaN被刻蚀,结合强度低,界面热阻高(107±44 m2·K·GW-1),具有SiC保护层的样品结合面平整光滑,有较低的界面热阻(30±5 m2·K·GW-1),认为是SiC保护层与金刚石有更强的结合力,相比于直接在AlGaN上沉积金刚石,SiC与金刚石之间形成了更多的碳化物键,有助于界面的声子传热,改善了热传输。

由于保护层的材料和厚度都对热阻有很大影响,很多研究人员对此展开了研究。Yates等[61]研究了没有保护层、具有5 nm厚SiN保护层、具有5 nm厚AlN保护层的金刚石/GaN结构的界面热阻,在没有保护层和具有5 nm厚AlN保护层的样品中,发现GaN被刻蚀,导致界面粗糙,使样品的界面热阻增加,界面热阻分别为41.4 +14.0/-12.3 m2·K·GW-1、18.2+1.5/-3.6 m2·K·GW-1,而且在没有保护层的样品中,金刚石与GaN之间发生了分层。在具有5 nm厚SiN保护层的样品中,金刚石与GaN结合界面清晰,平整光滑,GaN层完整,没有受到刻蚀,界面热阻最低,为9.5 +3.8/-1.7 m2·K·GW-1。

金刚石异质外延工艺对所制备金刚石层的质量有很大影响,金刚石形核层由于晶粒较小,晶界多,导致其热导率低,如何提高金刚石形核层热导率也是一个问题。Malakoutian等[62]使用快速形核的方法,减小形核层厚度,降低界面热阻。他们使用MOCVD法在GaN表面沉积5 nm Si3N4作保护层,而后使用聚合物辅助浸晶技术,使氧终端金刚石颗粒呈-50mv zeta电位,Si3N4层表面呈+50 mv zeta电位,由于金刚石颗粒与Si3N4层表面巨大的电位差,可以实现金刚石颗粒的高密度播种,最终播种密度大于1012 cm-2。而后放入微波等离子体化学气相沉积(MPCVD)装置中,金刚石在低温度(~700℃)、低功率(600 W)、低腔压(20 Torr)、高甲烷浓度(5%)中10分钟快速形核,形核层厚度仅25-30 nm。形完成后迅速提高功率(1800 W)和腔压(70 Torr),降低甲烷浓度,金刚石生长完成后在氢等离子体环境中缓慢冷却至室温。他们使用这种方法成功制备了金刚石/GaN结构,如图10所示。其中保护层的厚度由最初的5 nm降至仅1 nm,其中1 nm的Si3N4层被氢等离子体刻蚀,还有3 nm转化为热导率更高的SiC,极大地降低了界面热阻(3.1±0.7 m2·K·GW-1)。

对于异质外延金刚石的形核层质量差、热导率低的问题,Smith等[63]也提出了一种混合金刚石晶粒播种的方法,他们使用MOCVD分别制备了Si基GaN和Si基AlN两个样品,在两个样品上使用静电喷雾法分两步播种微米金刚石(2±1μm)和纳米金刚石(3.3±0.6nm),然后使用微波等离子体增强化学气相沉积法(MWCVD)生长了厚金刚石层。发现在Si基GaN上金刚石和GaN大部分在冷却时分层,未分层的样品在结合面也有大的间隙或裂纹,而在Si基AlN上金刚石和AlN结合良好,热面热阻低(1.47±0.35 m2·K·GW-1),远小于仅使用纳米金刚石引晶生长的界面热阻(67±58 m2·K·GW-1)。这种方法制备的金刚石形核层大部分为微米金刚石,纳米金刚石填充了微米金刚石之间的空隙,大幅减小了金刚石形核层热阻,但是没有使用该方法制备GaN/AlN/金刚石结构样品。

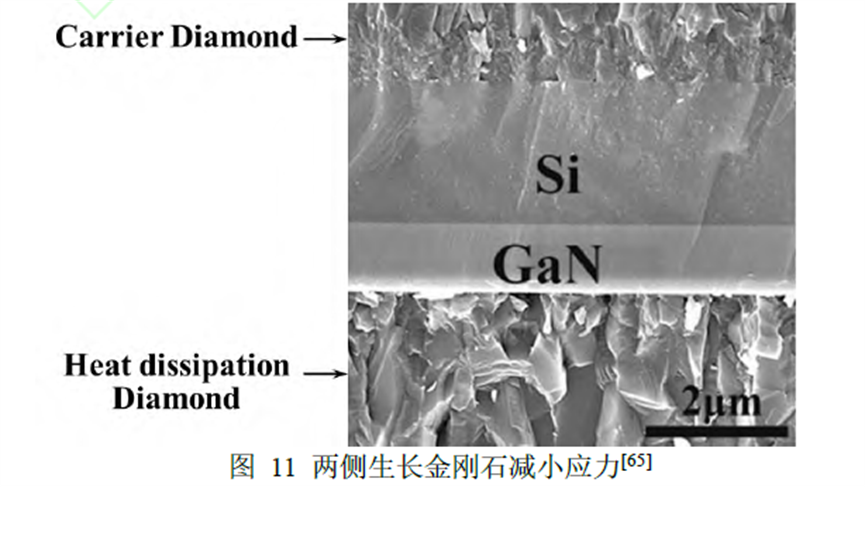

金刚石在GaN上异质外延的过程中,通常是在700~1000℃的高温环境中[64],由于金刚石与GaN材料之间存在大的热膨胀系数失配,在金刚石生长完成冷却下来后,在金刚石与GaN之间会存在1 GPa左右的应力。Jia等[65]针对热应力的问题,提出了一种GaN两侧生长金刚石的方法,首先在GaN上层沉积2μm厚Si层,然后在Si层上低温、高甲烷浓度沉积低质量牺牲层金刚石,GaN下层先去除原衬底、沉积SiN保护层,再沉积高质量金刚石作为散热层。如图11所示,制备了金刚石-GaN-金刚石结构,牺牲层金刚石和散热层金刚石共同分担了GaN收缩带来的应力,在经过退火、去除Si层和牺牲层金刚石后,GaN/金刚石结构的GaN层有0.5 GPa的张应力,GaN转移过程产生的应力得到有效缓解。

2.3 GaN异质外延金刚石技术

2.3.1金刚石钝化层散热技术

金刚石钝化散热技术,是一种利用金刚石薄膜替换原有源区的传统钝化层SiNx的技术,使用金刚石包覆器件层,可以显著提高器件的性能。相比其他技术,这项技术的优势在于金刚石层与热源接近,散热效率更高,但是存在金刚石层生长工艺与GaN器件层工艺的兼容性问题。

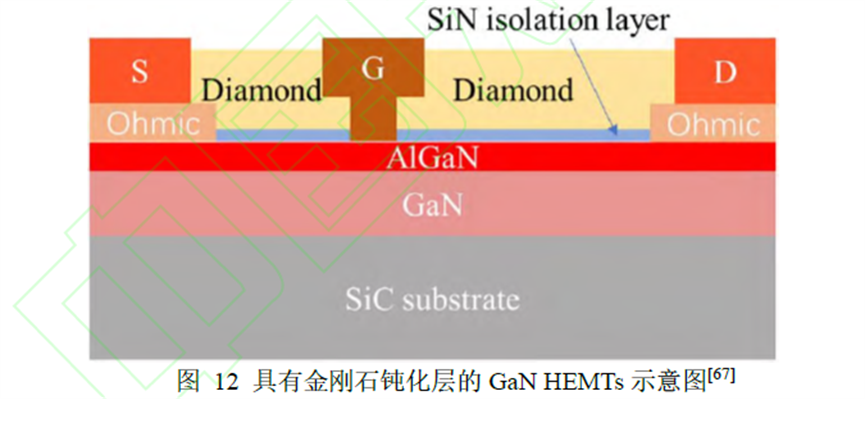

金刚石钝化层通常使用异质外延的方法制备,如MPCVD、HFCVD等,这些方法都需要高温、富氢等离子体的条件,GaN会发生严重的刻蚀、分解,为了解决这个问题,通常在GaN器件层上沉积保护层用于保护GaN,且由于金刚石和GaN之间大的热膨胀失配,需要在低温环境中沉积金刚石钝化层,减小应力。例如Yaita等[66]在沉积金刚石钝化层之前,先沉积40 nm厚SiNx层,然后在700℃的温度下沉积了2.5μm厚金刚石钝化层,由于沉积温度较低,金刚石层热导率仅为200 W·m-1·K-1,但是GaN器件的热阻也从12.7mm·K·W-1降低到7.4 mm·K·W-1,降幅达到了41.7%。国内南京电子器件研究所Guo等[67]进一步优化工艺,采用栅前金刚石的方法,使用三步金刚石刻蚀技术和20 nm SiN保护层,成功在GaN HEMTs器件的顶端制备了500 nm厚的金刚石钝化散热层,其结构示意图如图12所示。经测试,金刚石/GaN HEMTs的热阻比传统SiN/GaN HEMTs低21.4%,截止频率为34.6 GHz,比SiN/GaN HEMTs提高了1.8%,尤其是电流电压(VGS=1 V)和小信号增益(10 GHz)分别提高了27.9%和36.7%。金刚石钝化散热技术具有很好的应用前景,但是制备过程需要高精度的加工工艺,同时,由于金刚石膜沉积温度低,导致其晶体质量不高,无法发挥金刚石导热率高的优势,在实际应用中还需要进一步研究和改进。

2.3.2金刚石衬底外延技术

随着金刚石制备技术不断发展和完善,金刚石衬底异质外延GaN技术也被用于改善散热需求,和金刚石衬底异质外延GaN技术一样,也存在热膨胀系数失配和晶格失配的问题,会使GaN外延层发生剥离或破裂,需要使用额外的缓冲层缓解失配。同时金刚石衬底质量对GaN外延层质量也有很大影响,现在常用(111)单晶金刚石作为衬底,但是成本昂贵[68-71]。Pantle等[72]研究了单晶金刚石取向和缓冲层对GaN质量的影响,在(111)单晶金刚石、(001)单晶金刚石和具有AlN缓冲层的(001)单晶金刚石上使用MBE工艺选择性沉积了GaN纳米线,GaN纳米线结构如图13所示,在(111)金刚石上生长的GaN纳米线具有一致的形貌,在(001)金刚石上生长的GaN纳米线有多重形核和聚结。在具有AlN缓冲层的(001)金刚石上生长的GaN纳米线有最一致的形貌,表面光滑,生长偏转角度小,且缺陷最少。Xu等[73]在多晶金刚石上使用MOCVD工艺生长了GaN薄膜,发现在具有2.5 nm h-BN插入层和1000℃低温AlN层时GaN层晶体质量最好,相比没有h-BN插入层的GaN层,其表面光滑,(002)摇摆曲线的半峰全宽从4.67°降低到1.98°。

Ahmed等[74-75]结合了GaN异质外延金刚石技术和金刚石异质外延GaN技术,工艺步骤如图14所示,在GaN表面使用PECVD沉积一层SiNx保护层,而后使用纳米金刚石颗粒和光刻工艺相结合的方法,经过纳米金刚石加光刻胶旋涂、UV曝光、显影、干燥和刻蚀过程,在SiNx保护层上选择性的沉积多晶金刚石层,刻蚀掉未被金刚石覆盖的SiNx保护层部分,暴露出GaN层,之后在暴露的GaN和金刚石上层使用优化的MOCVD工艺横向外延过生长GaN层,再生长GaN层质量比原始GaN有更好的结晶度和更低的缺陷密度,但是由于金刚石与GaN热膨胀系数失配较大,以及多晶金刚石的粗糙表面(RMS>30 nm),在金刚石与GaN之间出现了图15所示的孔隙和空洞,进一步降低金刚石表面粗糙度也许可以获得完全结合的界面。

3.总结与展望

本文对近年来金刚石和GaN集成技术的研究现状进行了详细的综述。GaN功率器件的高功率密度优势受制于其衬底材料的低导热率而无法完全发挥,使用高导热率的金刚石作为器件的钝化层和衬底层,可以大幅度降低器件热点温度,提高器件功率密度。对于各种金刚石与GaN的集成技术,优缺点以及可能的改进方法可以总结为以下几点:

(1)键合技术的优势在于键合温度普遍较低,键合后金刚石与GaN之间热应力小,对GaN层的热损伤小,缺点在于键合层质量、厚度难以控制导致键合层热阻高,且大尺寸、低粗糙度、低弯曲度的金刚石获取成本高,可以从键合后处理工艺以及键合设备开发入手,还需要优化金刚石精密抛光工艺,探索新型金刚石表面处理技术;

(2)GaN异质外延金刚石技术优势在于金刚石与GaN结合强度高,结合均匀性好,但是由于金刚石与GaN之间的热膨胀失配和晶格失配,冷却后金刚石与GaN之间热应力大,可能导致分层或外延层开裂,还存在保护层、金刚石形核层热阻高的问题,可以从金刚石低温沉积以及提高形核层晶粒尺寸、减小形核层厚度入手,同时探索新型保护层材料和保护层制备工艺;

(3)金刚石异质外延GaN技术优势在于可以使用大尺寸高导热率金刚石作为散热层衬底,但是也存在热膨胀失配和晶格失配的问题,同时缓冲层热阻高,可以从开发新型缓冲层或多层缓冲层入手,以减小热应力和缓解晶格失配。

总的来说,目前的金刚石与GaN集成技术已经大大提升了GaN的实际应用功率密度,但是仍有许多问题亟需解决。目前的研究大多是对器件层或衬底层单独的研究,将其高效的结合起来,金刚石用于GaN功率器件的三维散热,将大幅度降低器件温度,有望在未来完全发挥GaN的高功率密度高频率优势。

欢迎扫码添加小编微信

扫码加入知识星球,领取公众号资料

原文标题:芯片制造:MOSFET的一个工艺流程

文章出处:【微信公众号:半导体封装工程师之家】欢迎添加关注!文章转载请注明出处。

-

封装

+关注

关注

127文章

8142浏览量

143853

发布评论请先 登录

相关推荐

芯片制造:MOSFET的一个工艺流程

芯片制造:MOSFET的一个工艺流程

评论