本系列所有演示实验均出自由东南大学汤勇明教授、张圣清教授与Xilinx大学计划经理陆佳华先生所编著的教材《搭建你的数字积木·数字电路与逻辑设计(Verilog HDL&Vivado版)》。此教材为教育部Xilinx公司产学合作专业综合改革重点支持项目,并作为Xilinx公司大学计划指定教材。

本书系统论述了数字电路与逻辑设计的理论、方法与实践技术。全书基于Verilog HDL与Vivado开发环境,共18章,详尽介绍了如下内容: 逻辑设计与Vivado基础、布尔代数与Verilog HDL基础、组合逻辑电路设计基础、时序逻辑电路设计基础、有限状态机设计基础、逻辑设计工程技术基础、Vivado数字积木流程、串行通信接口控制器、RAM接口控制器、字符点阵显示模块接口控制器、VGA接口控制器、数字图像采集、数字逻辑系统设计案例、单周期CPU设计案例、数字信号处理设计案例(FIR)、数字图像处理设计案例、大学生FPGA设计案例以及Xilinx资源导读。

为便于教师和广大读者学习与动手实践,本书配套提供了教学课件、教学视频及程序代码等教学资源。本书适合作为普通高等院校电子信息类、电气信息类、自动化类专业的本科生教材,也可作为相关专业研究生参考教材,并适合作为电子与电气工程技术领域的科研工程技术人员的参考用书。

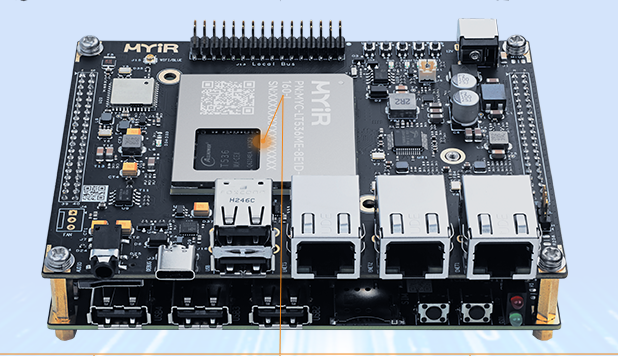

实验步骤实验内容本实验介绍32位单周期处理器设计,并在EGO1开发板上实现。

实验原理本实验用以下模块来实现:

ALU:ALU算术逻辑单元,是处理器中的一个重要功能模块,用来执行多组加减乘除等算术运算以及或与非等逻辑运算。算术逻辑单元的操作和种类由控制器觉定,处理的数据来自存储器,处理后的结果送回存储器或者暂存于算术逻辑单元中。ALU框图如下所示,alu为控制信号,包括了ALU需要执行的运算的命令,a和b为两个输入,r是运算结果,z为carry。

REGFILE:一个32位深度的寄存器文件,用于缓存来自memory或ALU的数据指令op和func将被转换成wreg、regrt、shift等信号,如下图所示:

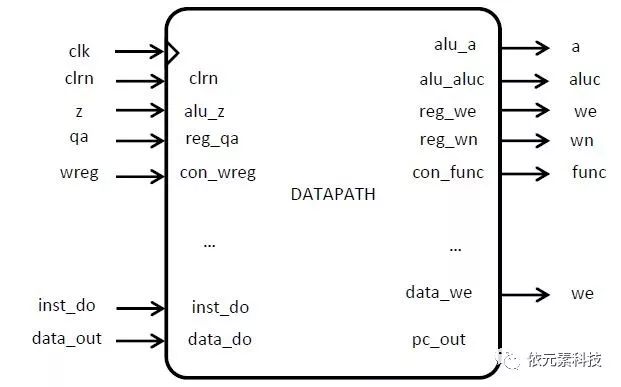

DATAPATH: DATAPATH用于连接所有的子模块,同时具备指令计数器的功能,其框图如下图所示:

INSTMEM:instruction memory,指令储存器,用于存放工程的测试指令。

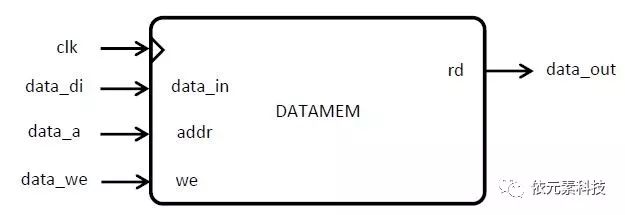

DATAMEM:用于存储所有工程测试数据例如ALU计算结果等。输入为写使能、时钟、地址以及写入的数据,输出为data_out信号,其框图如下所示:

KEY2INST:将开关状态转换为CPU的指令。

SHOWONLED:将最终计算结果或者开关状态按照预先设定好的模式通过LED展示给用户。输入计算结果和开关状态,输出为控制LED的信号,其框图如下所示:

通过本实验,可实现一个CPU,根据输入的指令控制LED灯。

实验资料:可以通过github下载,下载链接请点击这里。

代码说明:本实验的代码已经全部封装成IP核,用户只需将IP核调用并正确连续即可,MIPS_CPU.xdc为本实验的管脚约束文件。

-

本实验使用Vivado 2017.1 进行开发,开发界面如下。如果您未安装vivado,安装流程请点击这里。

2.实验RTL视图:

3.代码综合后效果图:

4. 代码实现后效果图:

具体vivado步骤请参看之前的微信文章,文章链接请点击这里。

验证流程将代码下载到板卡后,可按照下面的操作实现一个简单的加法运算,两个家数分别为16位的0000000100000000和16位的0000000000000000,操作过程如下:

-

将B14-B0设置为0,将B15设置为0,然后再设置为1,完成系统复位。

-

将B9-B8设置为10,将B7-B0设置为00000001,然后将B13设置为1后马上设置为0,目的是加载data+bh。

-

将B9-B8设置为11,将B7-B0设置为00000000,然后将B13设置为1后马上设置为0,目的是加载data_bl。

-

将B9-B8设置为00,将B7-B0设置为00000000,然后将B13设置为1后马上设置为0,目的是加载data_ah。

-

将B9-B8设置为01,将B7-B0设置为00000000,然后将B13设置为1后马上设置为0,目的是加载data_al。

-

将B12-B10设置为000,这样就选择了加法运算模式。然后将B14设置为1,此时CPU运行运算,结果为0000000100000000,此时的结果将显示在16位LED上。

-

ALU

+关注

关注

0文章

34浏览量

13562 -

eg01开发板

+关注

关注

0文章

1浏览量

1862 -

单周期处理器

+关注

关注

0文章

1浏览量

1478

原文标题:【玩转EGO1系列教程三】:在EGO1开发板上实现RISC

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

新品!从MINI到工业板:米尔T153开发板工业场景全覆盖

【ESP32-P4C5系列】WTDKP4C5-S1开发板上手指南

【ESP32-P4C5系列】WTDKP4C5-S1开发板规格书

NXP S32G-VNP-EVB3开发板全方位解析

探索MCIMX93-QSB开发板:开启嵌入式开发新征程

探索FRDM - IMX8MPLUS开发板:开启嵌入式开发新旅程

AM62x开发板的常见接口问题及排查思路(第2期)

RK3568开发板暗藏32位兼容开关?飞凌嵌入式带你一键解锁!

基于米尔全志T536开发板的多协议物联网关的方案测试

基于RK处理器,创龙TL3562-MiniEVM开发板试用体验

基于EGO1开发板的32位单周期处理器设计案例

基于EGO1开发板的32位单周期处理器设计案例

评论