逻辑电平输出是数字电路中的一个重要概念,它涉及到数字信号的表示和传输。在数字电路中,逻辑电平通常指的是电路中用于表示二进制数字(0和1)的电压水平。逻辑电平输出则是指电路输出端能够提供的逻辑电平信号。

逻辑电平输出的定义

逻辑电平输出是指数字电路中的输出端能够产生的电压水平,这些电压水平用于表示逻辑状态。在数字电路中,通常使用两个不同的电压水平来表示逻辑0和逻辑1。例如,逻辑0可能对应于0V,而逻辑1可能对应于5V或3.3V,这取决于电路的设计。

逻辑电平输出的重要性

- 信号表示 :逻辑电平输出是数字电路中信号表示的基础。

- 信号传输 :逻辑电平输出决定了信号在电路中的传输方式和效率。

- 兼容性 :不同的电路和设备可能需要不同的逻辑电平,逻辑电平输出的兼容性对于系统的整体性能至关重要。

- 功耗 :逻辑电平输出的电压水平也影响电路的功耗。

逻辑电平输出的类型

- TTL(晶体管-晶体管逻辑) :TTL逻辑电平输出是早期数字电路中常用的一种标准,逻辑1通常为3.3V或5V,逻辑0为0V。

- CMOS(互补金属氧化物半导体) :CMOS逻辑电平输出具有更低的功耗和更高的噪声容限,逻辑1和逻辑0的电压水平可能因不同的CMOS标准而异。

- LVDS(低压差分信号) :LVDS是一种高速、低功耗的信号传输技术,使用差分信号来表示逻辑电平。

逻辑电平输出的应用

- 微处理器与内存 :在微处理器和内存之间的数据传输中,逻辑电平输出用于确保数据的正确表示和传输。

- 通信接口 :在串行通信接口如RS-232、USB、以太网等中,逻辑电平输出用于信号的编码和解码。

- 传感器与控制器 :在传感器与微控制器之间的接口中,逻辑电平输出用于信号的传输和处理。

技术细节

- 电压水平 :逻辑电平输出的电压水平需要精确控制,以确保信号的正确解释。

- 驱动能力 :输出端需要有足够的驱动能力,以确保信号能够被接收端正确接收。

- 抗干扰能力 :逻辑电平输出需要具备一定的抗干扰能力,以保证信号在噪声环境下的稳定性。

- 功耗 :逻辑电平输出的设计需要考虑功耗,尤其是在电池供电的便携设备中。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

数据传输

+关注

关注

9文章

1901浏览量

64625 -

电压

+关注

关注

45文章

5607浏览量

115816 -

数字信号

+关注

关注

2文章

970浏览量

47554 -

逻辑电平

+关注

关注

0文章

152浏览量

14424

发布评论请先 登录

相关推荐

逻辑电平转换说明

逻辑电平转换说明自从TTL和5V的COMS成为逻辑电路的主导标准以来,电子设计已发生了相当大的改变。现代电子系统日益增加的复杂性导致了低电压逻辑的产生,但同时又引起在一个系统内部输入

发表于 10-24 13:43

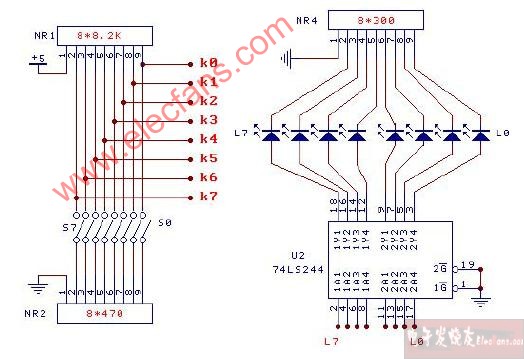

逻辑电平开关电路

逻辑电平开关电路如图所示实验台右下方设有8个开关K7~K0,开关拨到“1”位置时开关断开,输出高电平。向下打到“0”位置时开关接通,输出低

发表于 03-25 09:29

•6478次阅读

逻辑电平详细介绍

逻辑电平详细介绍逻辑电平有:TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVDS、GTL、BTL、ETL、GTLP;RS232、RS422、RS485等。 常用

发表于 04-12 12:03

•1.1w次阅读

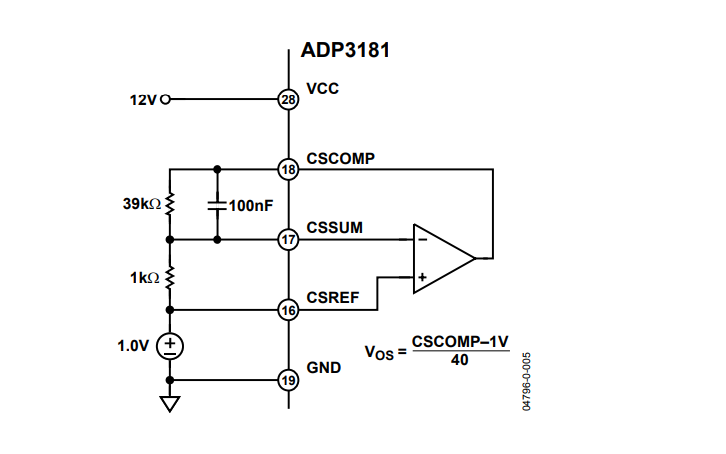

ADP3181多相同步降压开关调节器控制器的数据手册免费下载

电压。CPUID输入选择DAC代码是否与VRM 9或VRD 10规格匹配。它使用多模式PWM架构,以可编程的开关频率驱动逻辑电平输出,该频率可针对VR尺寸和效率进行优化。输出信号的相位

发表于 09-30 08:00

•7次下载

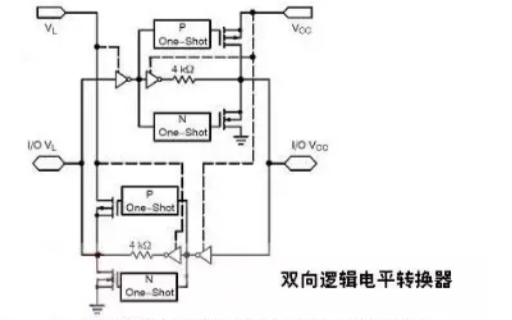

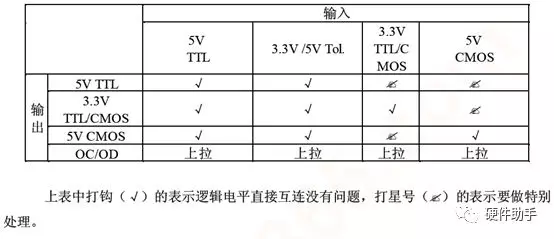

FPGA逻辑电平的互连电平转换详细说明

电平电压等级越来越低(好多控制器对外接口都直接输出1.8V或更低了),而同种逻辑电平、不同电压等级之间的转换就变得更为常见了。

发表于 01-07 17:07

•13次下载

逻辑电平--差分信号(PECL、LVDS、CML)电平匹配

由于各种逻辑电平的输入、输出电平标准不一致,所需的输入电流、输出驱动电流也不同,为了使不同逻辑

【硬声推荐】逻辑电平视频合集

为了精简电路 电器中会用到逻辑电平代替复杂的接线 他们都是如何设计的呢? CMOS器件与TTL器件 CMOS电平与TTL电平 如何利用MOS管实现双向

引脚可编程输出频率、输出逻辑电平及扇出功能的时钟分配电路

电子发烧友网站提供《引脚可编程输出频率、输出逻辑电平及扇出功能的时钟分配电路.pdf》资料免费下载

发表于 10-08 09:24

•0次下载

逻辑电平输出是什么意思

逻辑电平输出是什么意思

评论