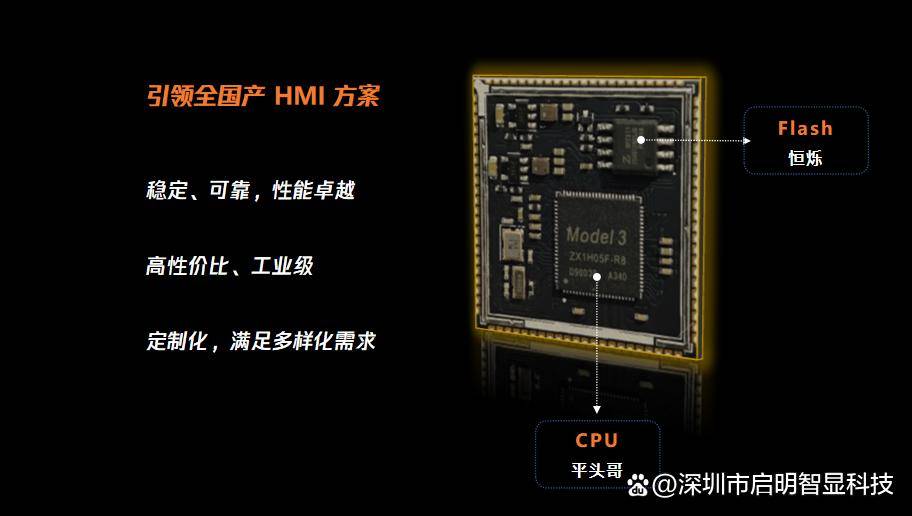

Model系列芯片目前已经在智能家居、工业HMI、工业串口屏、智能仪表、充电桩等各个领域实现应用,也得到了客户的一众好评。在应用的过程中,我们也发现了很多小伙伴对Model系列PWM调试方面存在一些问题,因此,本期我们将深入探讨PWM-DAC原理及实现方法,希望通过本期内容带给大家一些启发。

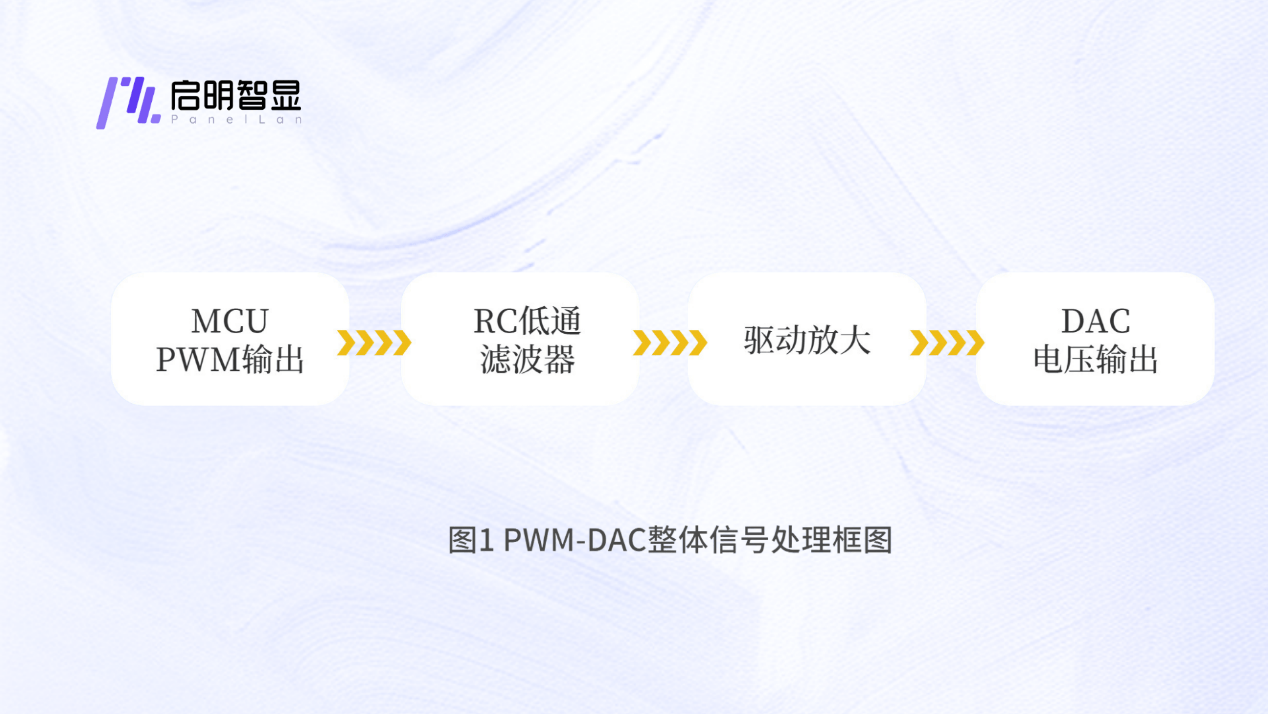

一、整体方案概述

二、PWM→DAC原理分析

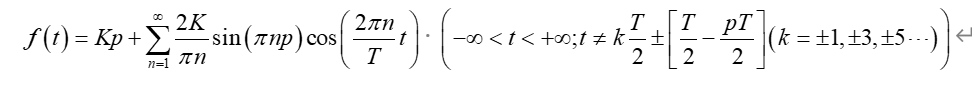

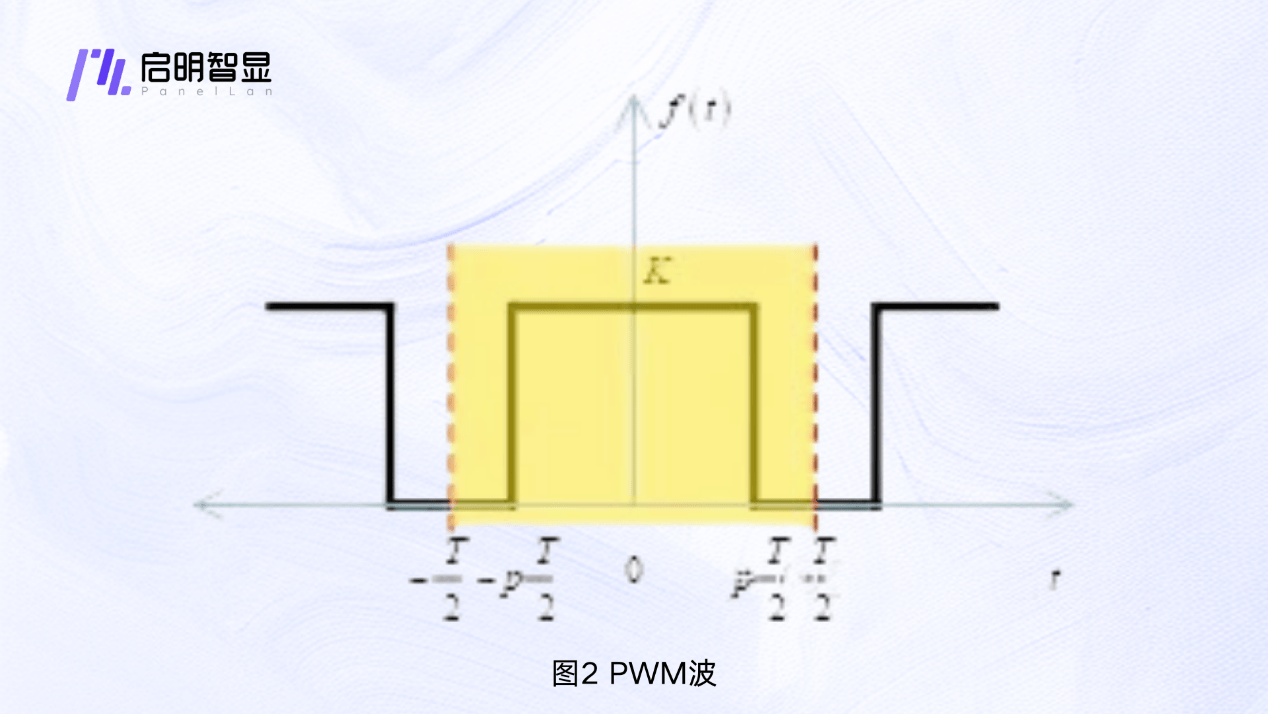

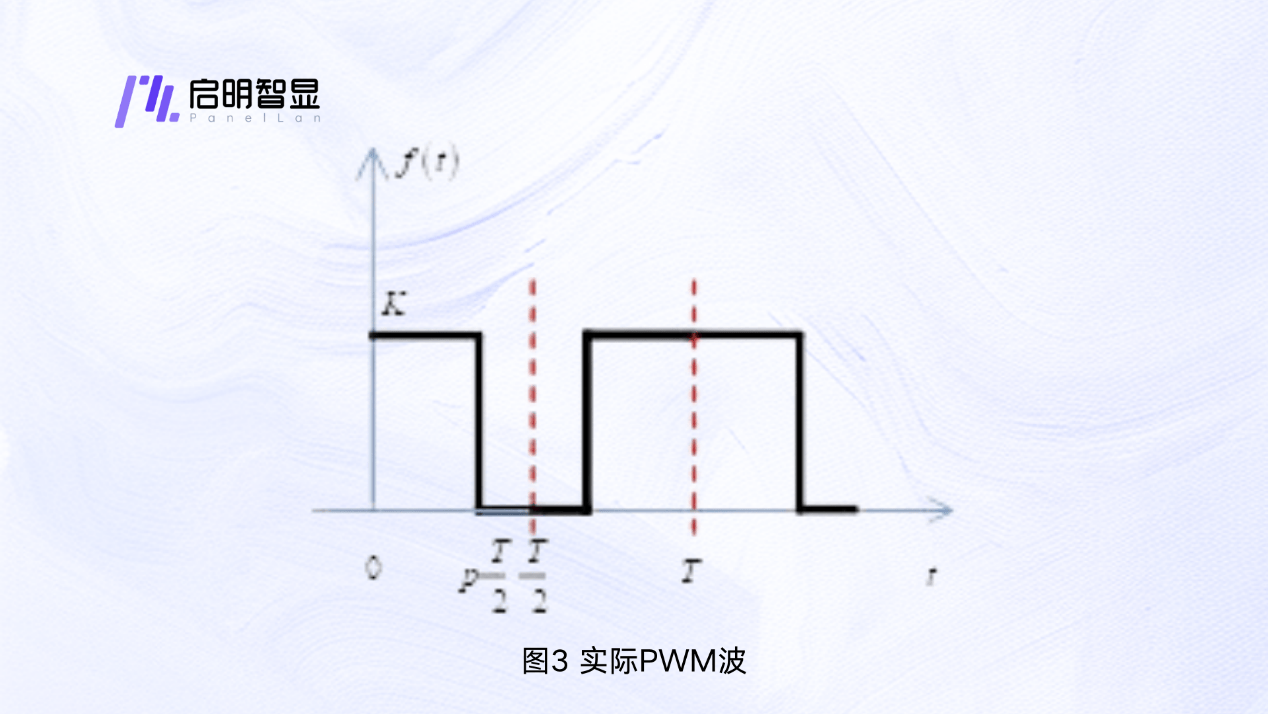

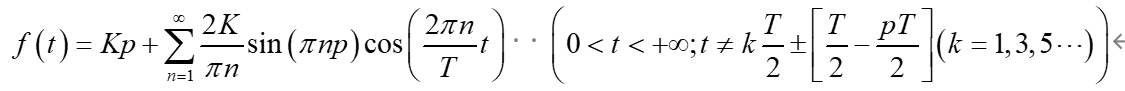

图2中的周期为T,占空比为p的PWM波按照傅里叶级数(Foerioe series)展开为:

关注t>0的部分,即:

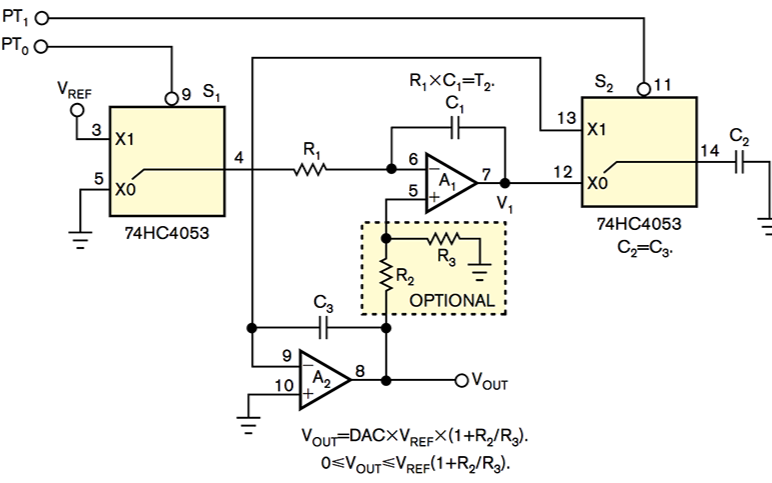

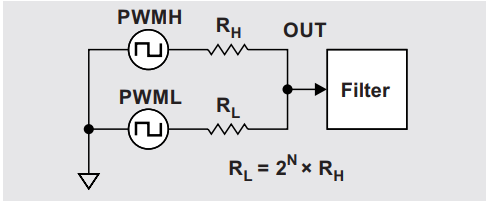

实现可调的DAC需要两个步骤,其一是根据输出电压需要及PWM波傅里叶级数的直流分量“Kp”确定MCU输出PWM波的占空比p。其二是设计RC低通滤波器将PWM波傅里叶级数的谐波分量滤除掉,即可得电压值为“Kp”的输出。

三、低通滤波器(RC)

(一)DAC输出电压分辨率、滤波器衰减系数的确定

DAC电压输出可分为静态输出和动态输出,下面分别介绍。在静态输出是指输出不随时间变化的恒定电压。静态输出评价指标输出分辨率(8位、12位)和输出稳定性。其中输出分辨率越高输出精度越高。低通滤波器对PWM波的谐波分量的抑制效果对电压输出的稳定性起着决定性的作用。一般而言,抑制效果越好,输出电压越稳定。通常根据一次谐波对输出电压的影响不要超过最低位的精度,来确定低通滤波器对一次谐波的衰减系数(dB)。

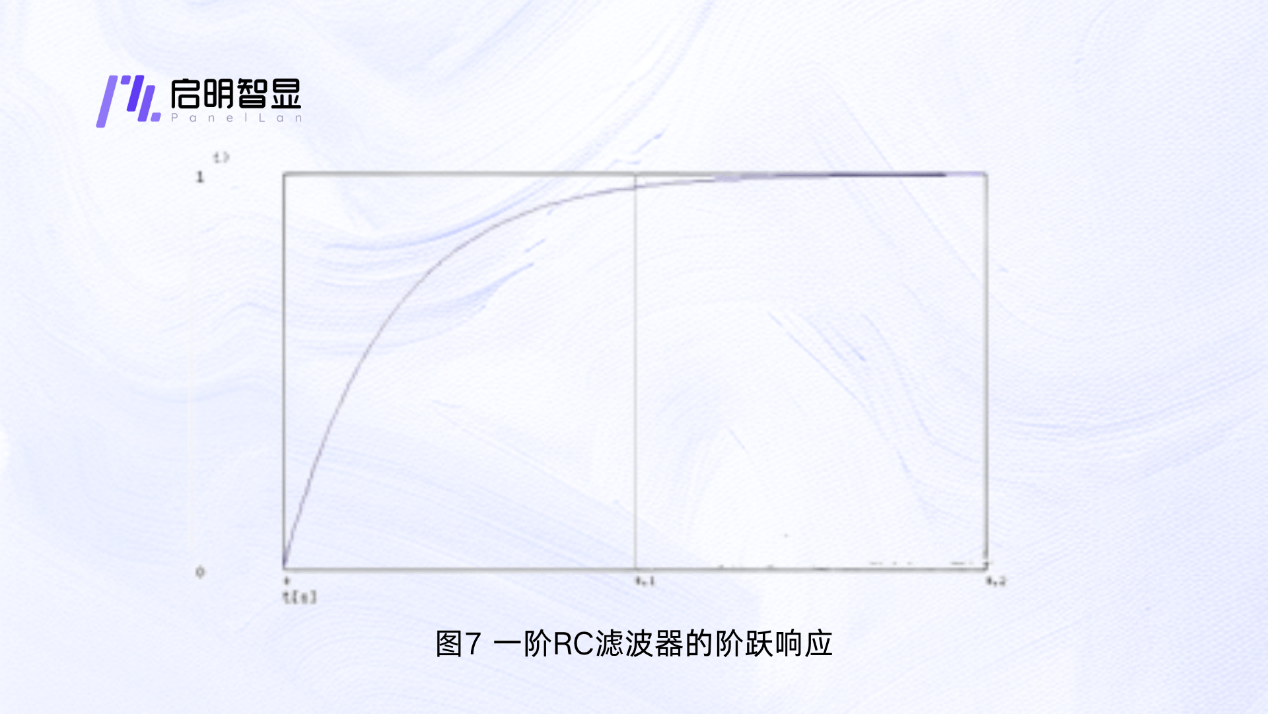

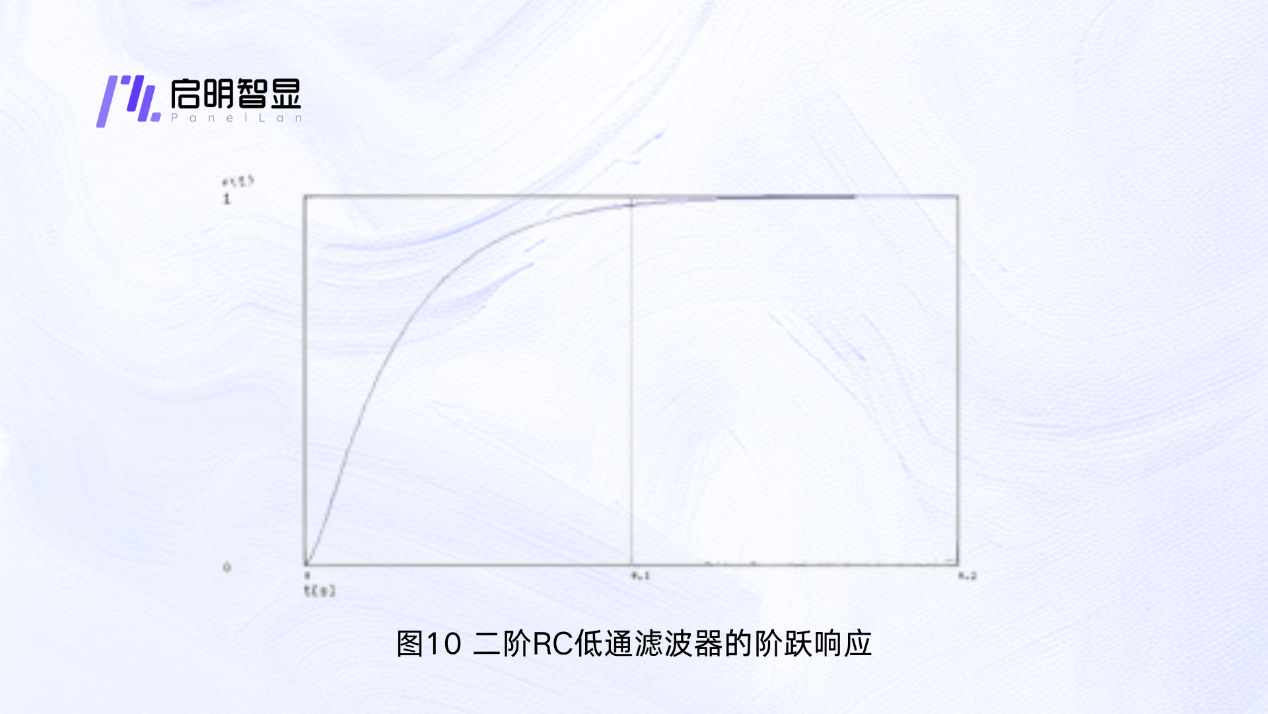

动态输出是指输出电压需要随时间变化的输出形式。动态输出的评价指标包括输出分辨率、输出稳定性和低通滤波器的阶跃响应时间(暂态响应)。

一般情况下,微处理器的系统时钟周期是一定的。在输出稳定性一定的情况下,阶跃响应时间与输出电压分辨率呈现出此消彼长的关系。即输出分辨率越高,一阶谐波分量的周期越长,要想维持输出稳定性需要的低通滤波器的RC值越大。而RC值越大,系统的阶跃响应时间越长,动态输出效果越差。

在输出分辨率(PWM波的周期)一定的情况下,阶跃响应时间与输出稳定性呈现反比关系,当输出稳定性越高,即低通滤波器对PWM波一次谐波有越强的衰减特性,采用RC滤波器,此时,RC值越大。而RC值越大,系统的阶跃响应时间越长,动态输出效果越差。

一般策略:

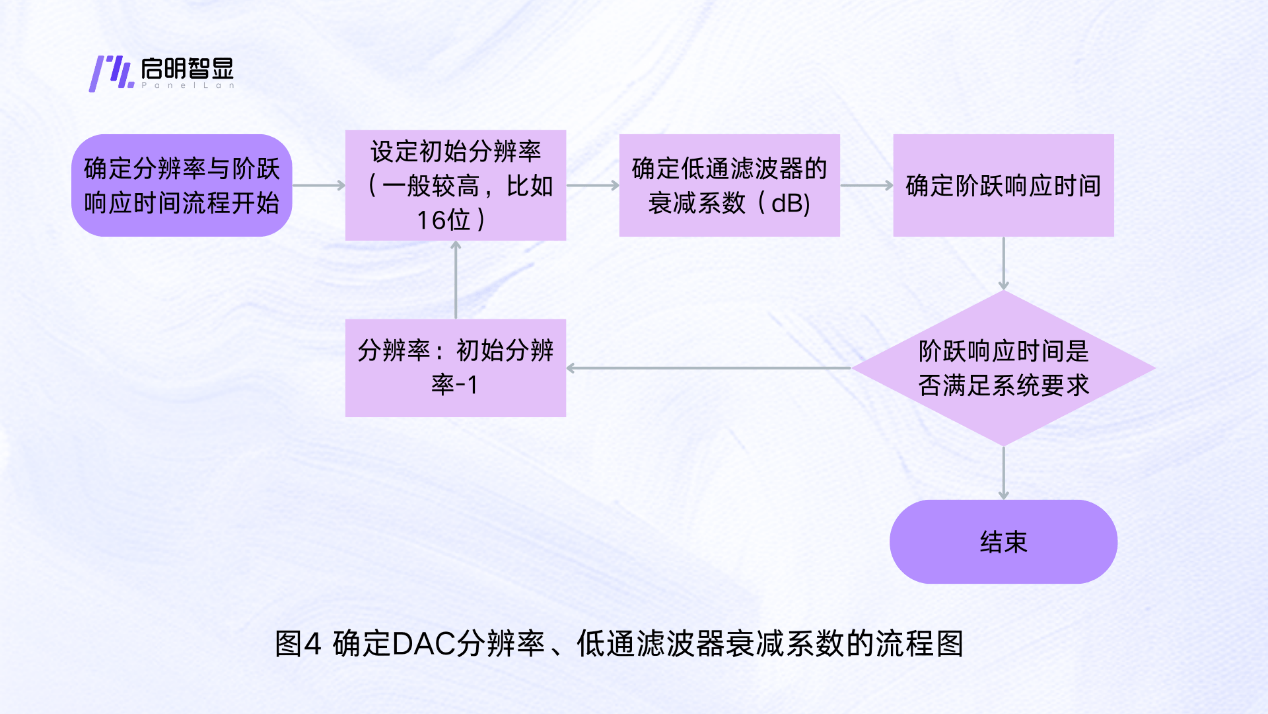

一般实在保证阶跃响应时间的同时,使得电压输出的分辨率尽可能高。确定输出分辨率、衰减系数(dB)具体流程如图4所示。在输出分辨率(PWM波的周期,从分辨率由高到低进行尝试)一定的情况下,根据一次谐波对输出电压的影响不要超过最低位的精度,来确定衰减系数(dB)(输出稳定性),进而确定低通滤波器的RC值,也即阶跃响应时间。如果阶跃时间不满足应用需要,对分辨率进行减一操作,重复上述操作,直至阶跃响应时间满足应用需要。

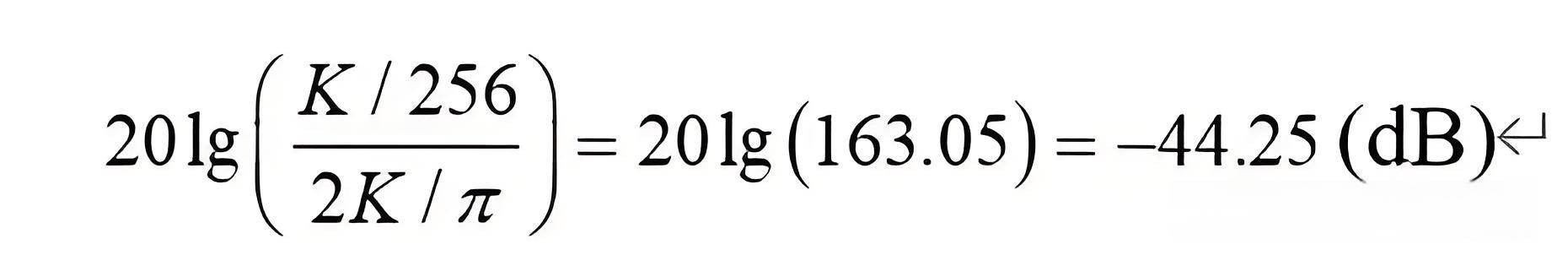

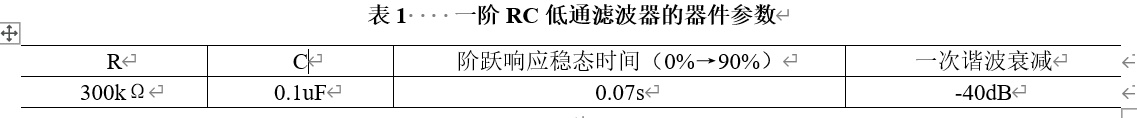

本文采用PWM波的频率为500Hz(T=2ms),其一次谐波频率为500Hz。DAC在8位分辨条件下,要求一次谐波对输出电压的影响不要超过1个位的精度,来确定低通滤波器的衰减系数(dB)。

一个位的精度:K/256=0.0195V,一次谐波的最大赋值(p=0.5):2K/π。低通滤波器的衰减系数:

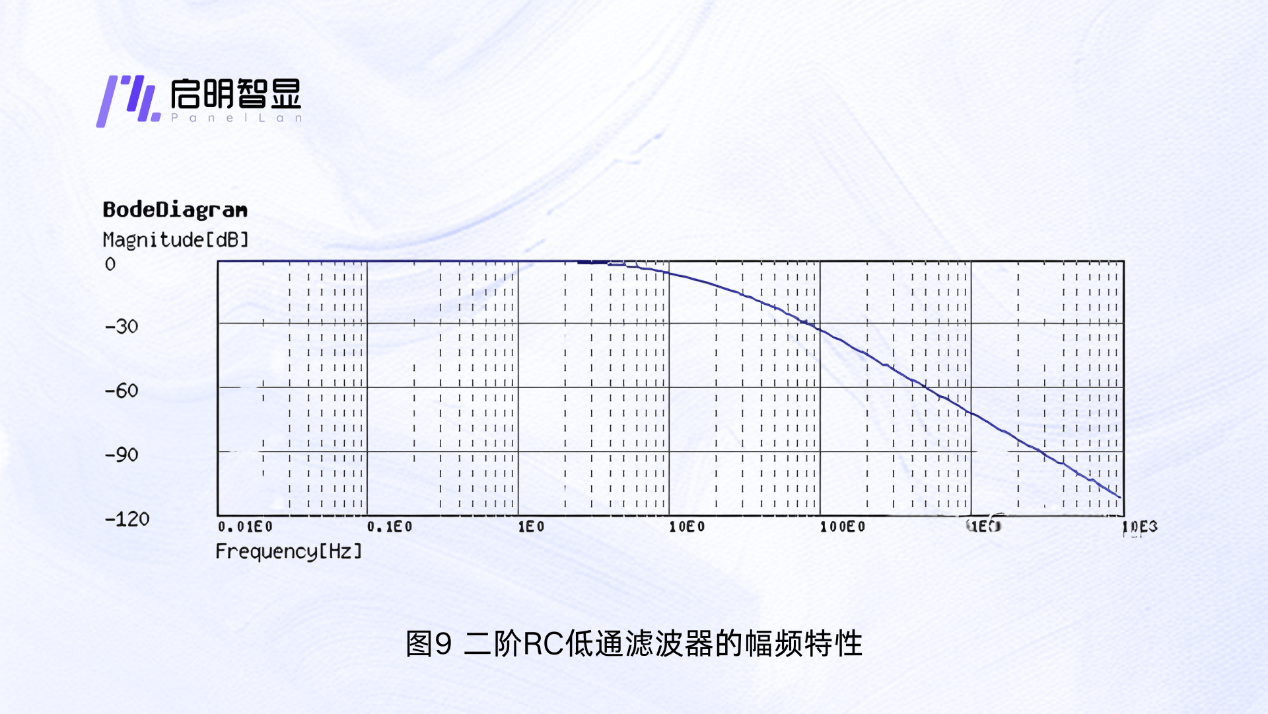

也就是要求RC滤波电路至少在一次谐波处,即500Hz处提供-44.25(dB)的衰减。此处设计低通滤波器主要考虑两个方面,其一是要在500Hz处实现-44.25(dB),这里为了方便,取-40(dB)(衰减到输入的1/100)。这往往可以通过增加RC的乘积来实现,但较大的RC,意味着较长的稳态时间(0%→90%),影响系统的暂态响应。此处低通滤波器的设计原则:在保证在500Hz实现-40(dB)的条件下,尽量减少RC的乘积。

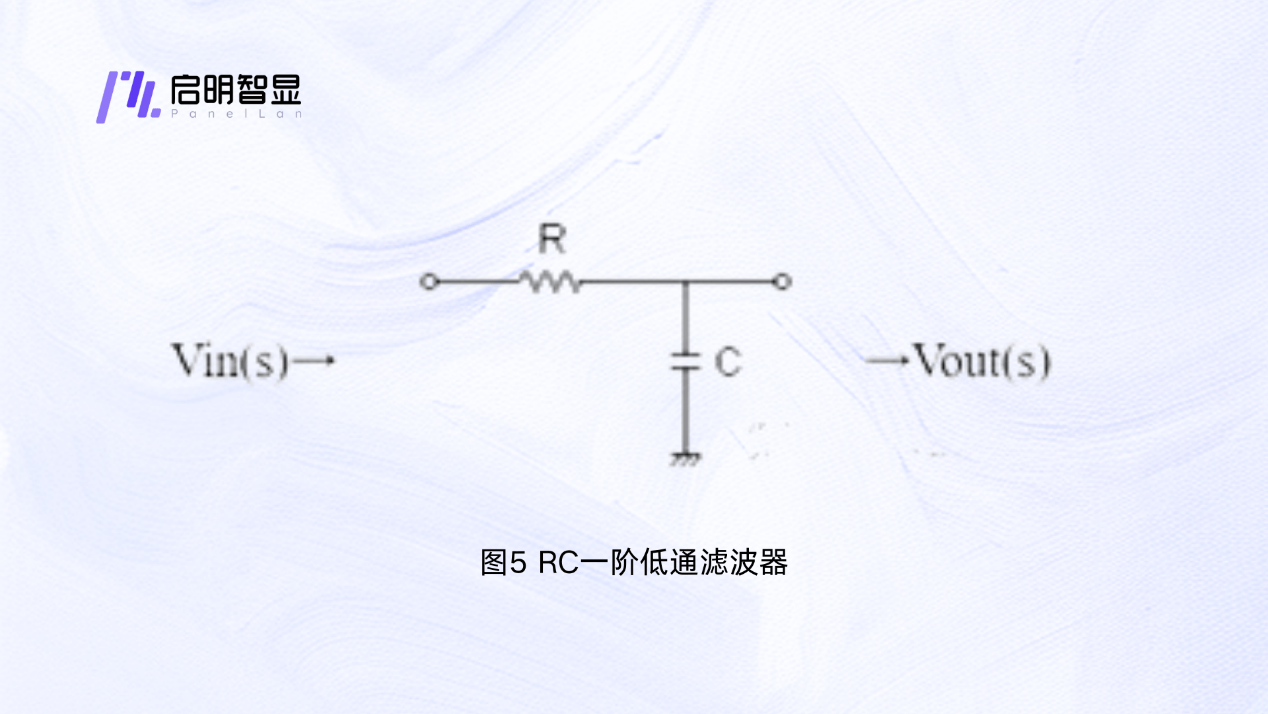

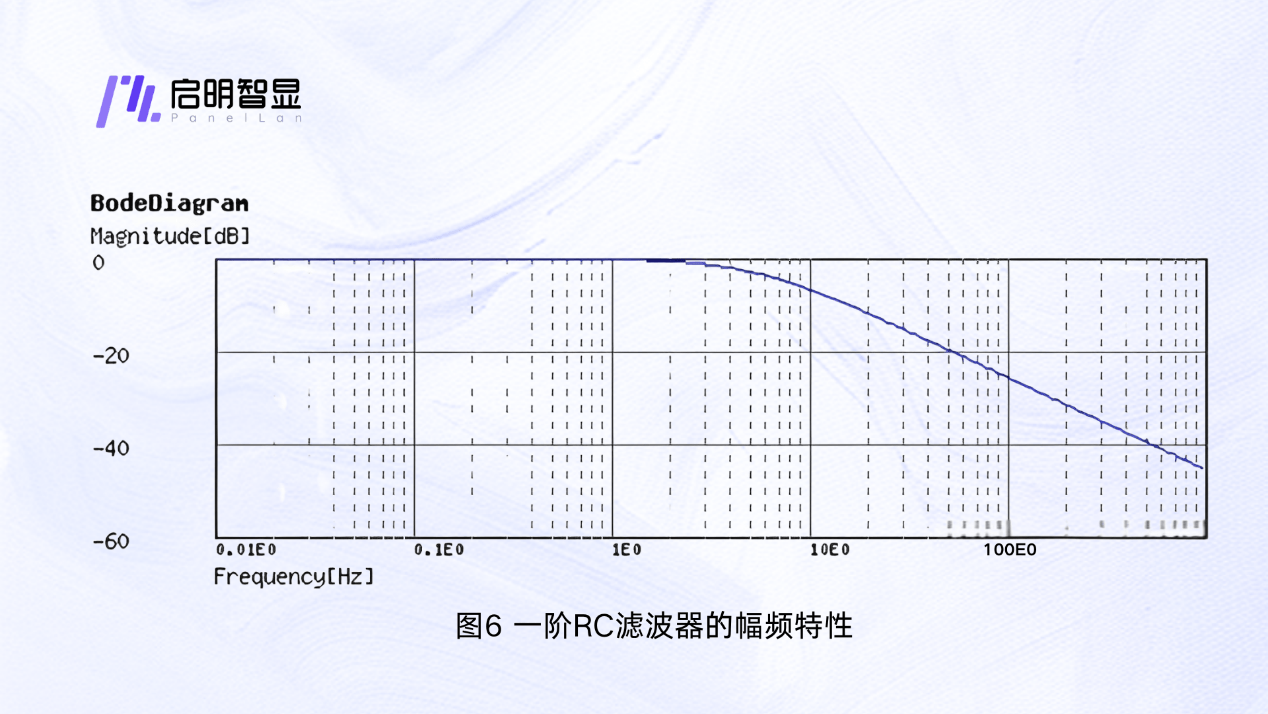

(二)RC一阶低通滤波器

RC一阶低通滤波器:

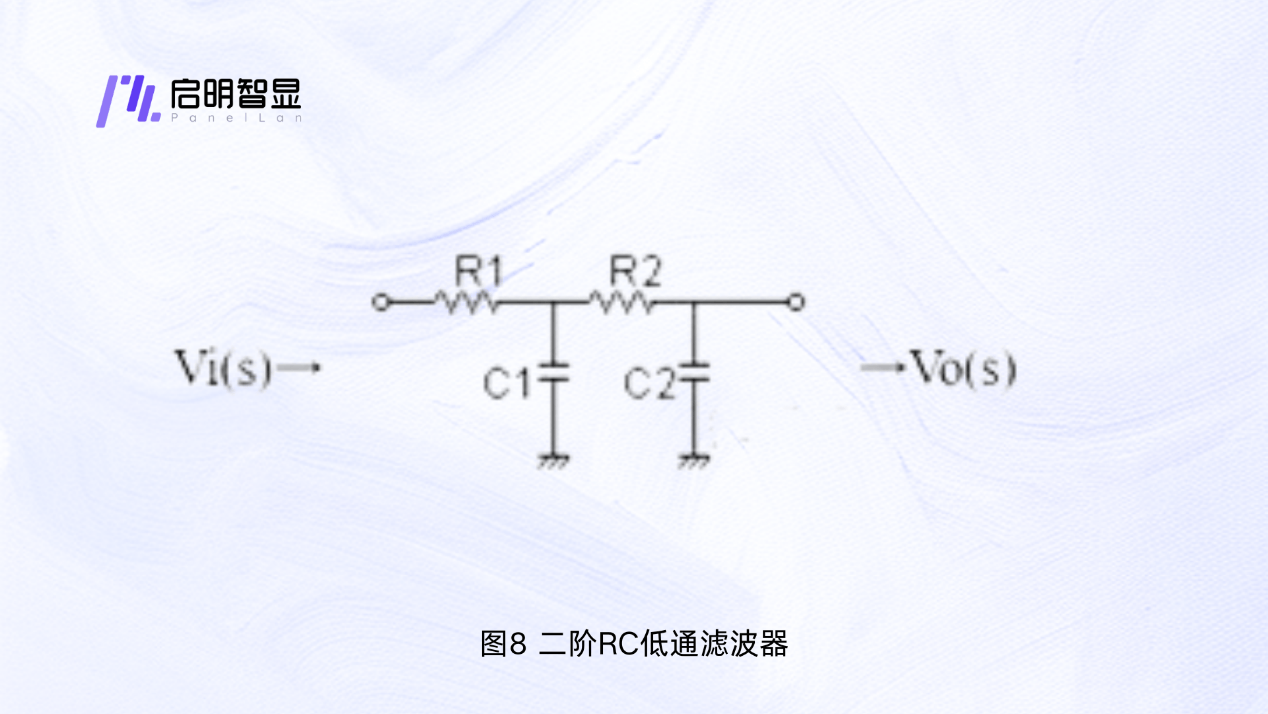

(三)二阶RC低通滤波器

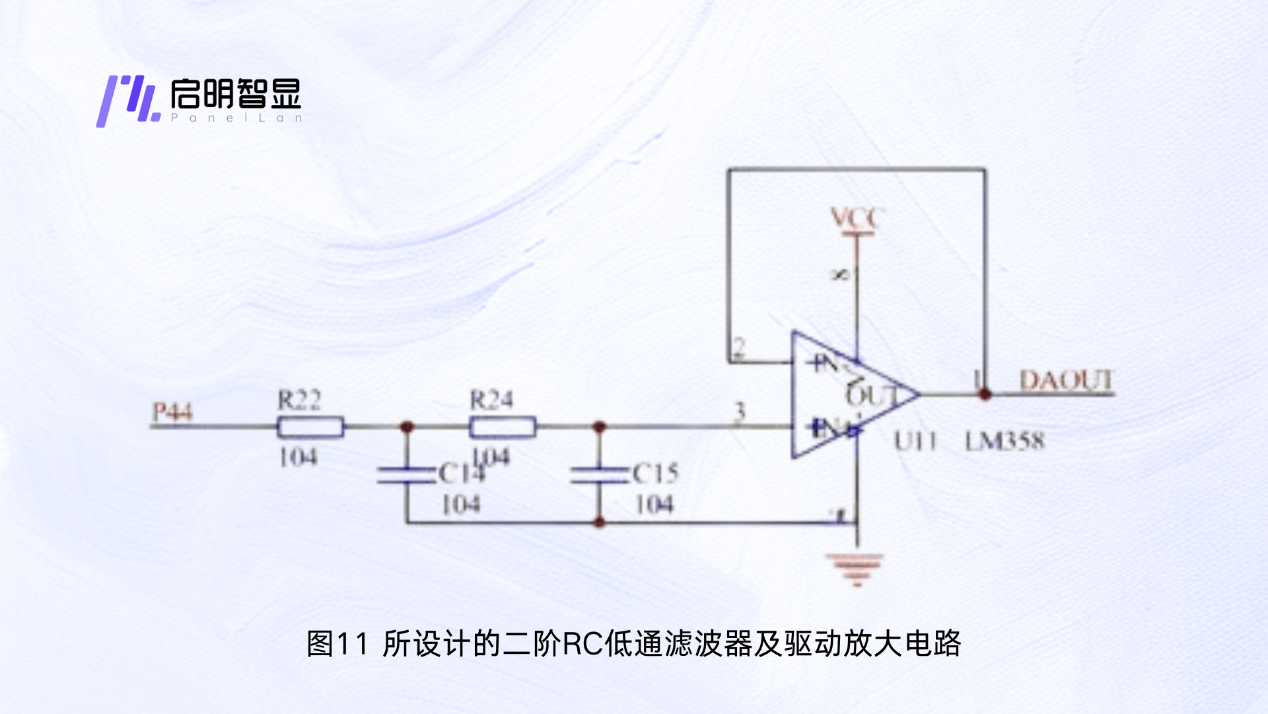

本文中所用的低通滤波器采用的是二阶RC低通滤波器,具体参数见表2。

(四)驱动设计

为了提高DAC驱动能力(输出电流能力),将二阶RC低通滤波器的输出接到运放设计的电压跟随器上。

以上就是对PWM-DAC技术的详细分享,希望能对大家有所帮助。

-

PWM

+关注

关注

114文章

5209浏览量

215691 -

dac

+关注

关注

43文章

2320浏览量

192038 -

工业

+关注

关注

3文章

1907浏览量

47110 -

HMI

+关注

关注

9文章

608浏览量

48978

发布评论请先 登录

相关推荐

如何快速建立的同步PWM-DAC滤波器没有纹波?

如何快速建立的同步PWM-DAC滤波器没有纹波?

STM32F4 PWM-DAC实验例程

Model3C工业级HMI芯片详解系列专题(一):芯片性能

技术分享:国产工业级HMI芯片Model系列PWM-DAC实现指南

技术分享:国产工业级HMI芯片Model系列PWM-DAC实现指南

评论