SOC(System on Chip,芯片上的系统)芯片的测试是一个复杂且全面的过程,涉及多个参数和模块。以下是对SOC芯片测试的主要参数和模块的归纳:

一、测试参数

- 电性能测试 :

- 性能测试 :

- 内存带宽 :衡量芯片处理数据的能力。

- CPU执行速度 :反映芯片处理指令的速度。

- 功耗 :在不同工作模式和负载下的功耗表现。

- 其他特定参数 :

二、测试模块

SOC芯片的测试模块通常与其内部集成的功能模块相对应,包括但不限于:

- 处理器内核测试 :

- 测试CPU的执行速度、指令集支持情况等。

- 内存测试 :

- 接口控制器测试 :

- 模拟电路测试 :

- 数字电路测试 :

- 包括逻辑电路的测试,如扫描测试(SCAN)、自动测试向量生成(ATPG)、逻辑内建自测试(LBIST)等。

- 边界扫描测试 :

- 低功耗模式测试 :

- 测试芯片在不同低功耗模式下的功耗和性能表现。

- 静电放电(ESD)测试 :

- 测试芯片对静电的耐受性,确保其在静电环境下能够正常工作。

三、测试阶段

SOC芯片的测试通常分为以下几个阶段:

- 晶圆测试(Wafer Test) :

- 包括WAT(Wafer Acceptance Test)和CP(Chip Probe)测试,用于在封装前筛选出有问题的芯片。

- 最终测试(Final Test,FT) :

- 在芯片封装后进行的最终测试,确保芯片在用户模式下所有功能正常。

- 板级测试(Board Test) :

- 将芯片安装在电路板上后进行的测试,以验证其在系统环境中的表现。

四、测试挑战与未来趋势

SOC芯片测试面临着复杂性增加、成本控制、低功耗测试、测试自动化等挑战。未来趋势包括利用人工智能和机器学习技术提高测试效率和覆盖率、通过大数据分析优化测试流程、在片测试(On-Chip Testing)等。

综上所述,SOC芯片的测试是一个多维度、多阶段的复杂过程,需要综合考虑多个参数和模块以确保芯片的质量和性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

模块

+关注

关注

7文章

2666浏览量

47327 -

参数

+关注

关注

11文章

1773浏览量

32075 -

SoC芯片

+关注

关注

1文章

608浏览量

34862 -

漏电流

+关注

关注

0文章

260浏览量

16992

发布评论请先 登录

相关推荐

SoC芯片的开发流程有哪几个阶段

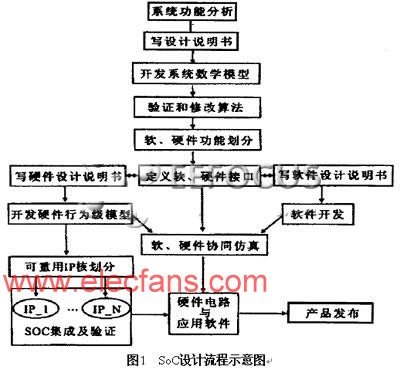

SoC芯片的开发流程SoC芯片开发流程大致分为四个阶段,其中大部分工作都是借助于电子设计自动化(EDA)工具完成的。总体设计总体设计阶段的任务是按照系统需求说明书确定

发表于 11-08 08:33

SoC和在线测试的好处

电压调节器、锁相环控制系统和振荡器、时钟和定时器、模拟到数字和数字到模拟转换器等。连接所有单个块的内部接口总线或网络。SoC 测试Soc 使单个芯片上的组件能够紧密集成,但这需要在发送

发表于 04-01 11:18

SOC测试访问机制

以复用为基础,通过测试访问机制(TAM, Test Access Mechanism)实现对深嵌在SOC(System On Chip)内部的IP 核(Intellectual Property, 知识产权模块)的

发表于 08-27 14:39

•8次下载

SOC芯片的DFT策略的可测试性设计

SOC是在同一块芯片中集成了CPU、各种存储器、总线系统、专用模块以及多种I/O接口的系统级超大规模集成电路。ASIC是专用于某一方面的芯片,与SO

发表于 04-03 16:04

•6818次阅读

soc芯片如何测试 soc是处理器吗 soc是数字芯片还是模拟芯片

测试SoC芯片需要专业的测试设备、软硬件工具和测试流程,同时需要一定的测试经验和技能。并且在

发表于 05-03 08:26

•5984次阅读

chiplet和soc有什么区别?

和芯片设计专家而言,这两个词汇已经不局限于概念或者开发平台,而是协同推进模块化设计、锐化产品线。那么,chiplet和SoC有什么区别?今天我们将详尽讲解。 概念解释: 所谓

SoC芯片设计中的可测试性设计(DFT)

随着半导体技术的飞速发展,系统级芯片(SoC)设计已成为现代电子设备中的主流。在SoC设计中,可测试性设计(DFT)已成为不可或缺的环节。DFT旨在提高

一文了解SOC的DFT策略及全芯片测试的内容

SOC ( System on Chip)是在同一块芯片中集成了CPU、各种存储器、总线系统、专用模块以及多种l/O接口的系统级超大规模集成电路。

由于SOC

发表于 12-22 11:23

•2712次阅读

soc芯片测试有哪些参数和模块

soc芯片测试有哪些参数和模块

评论