静电放电(ESD)是一种常见的电子设备损坏原因,尤其是对于敏感的半导体芯片。

引言

在电子行业中,静电放电(ESD)是一个不可忽视的问题。它可能导致芯片损坏,从而影响整个电子系统的稳定性和可靠性。本文将详细介绍如何判断芯片是否被静电打坏,包括静电的产生、影响、检测方法和预防措施。

静电的产生

- 摩擦起电 :当两种不同材料的表面相互摩擦时,电子从一个表面转移到另一个表面,导致电荷的不平衡。

- 接触起电 :当两种不同材料的表面接触并分离时,也会产生电荷。

- 感应起电 :当一个带电物体靠近另一个物体时,由于电场的作用,电荷会在物体表面重新分布。

静电对芯片的影响

- 热损伤 :静电放电产生的瞬间电流可能导致芯片局部过热,从而损坏晶体管。

- 电击穿 :高电压可能导致芯片内部的绝缘层击穿,造成永久性损坏。

- 数据丢失 :静电放电可能干扰芯片的存储单元,导致数据丢失。

- 性能下降 :即使不造成永久性损坏,静电放电也可能导致芯片性能下降。

判断芯片是否被静电打坏的方法

1. 外观检查

- 烧焦痕迹 :检查芯片表面是否有烧焦或变色的痕迹。

- 裂纹 :检查芯片是否有裂纹或破损。

2. 功能测试

- 自检程序 :运行芯片的自检程序,检查是否能够正常工作。

- 性能测试 :进行性能测试,比较测试结果与标准值,判断是否有性能下降。

3. 电气测试

4. 显微镜检查

- 显微镜 :使用显微镜检查芯片的微观结构,寻找可能的损伤。

5. 热成像

- 热成像仪 :使用热成像仪检查芯片的热分布,寻找过热区域。

6. X射线检查

- X射线 :使用X射线检查芯片内部结构,寻找可能的损伤。

7. 扫描电子显微镜(SEM)

- SEM :使用扫描电子显微镜检查芯片的微观结构,寻找损伤。

8. 透射电子显微镜(TEM)

- TEM :使用透射电子显微镜检查芯片的晶体结构,寻找损伤。

9. 电子束测试

- 电子束 :使用电子束测试芯片的导电性能,寻找损伤。

10. 逻辑分析仪

- 逻辑分析仪 :使用逻辑分析仪检查芯片的逻辑信号,寻找异常。

预防措施

- 接地 :确保所有设备和人员都接地,以减少静电积累。

- 防静电工作服 :穿着防静电工作服和鞋,减少静电产生。

- 防静电包装 :使用防静电包装材料,保护芯片免受静电影响。

- 湿度控制 :保持适当的湿度,减少静电产生。

- 防静电设备 :使用防静电设备,如防静电垫、防静电腕带等。

- 培训 :对员工进行防静电培训,提高他们的意识。

结论

静电放电是电子行业中的一个严重问题,可能导致芯片损坏。通过上述方法,我们可以判断芯片是否被静电打坏,并采取相应的预防措施,以保护芯片免受静电的影响。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

458文章

51408浏览量

428510 -

静电

+关注

关注

1文章

511浏览量

36542 -

半导体芯片

+关注

关注

60文章

921浏览量

70843

发布评论请先 登录

相关推荐

ISE VHDL 如何判断信号被更新

我有一个累加器,当信号a,b被更新之后a加b,然后累加。 我想用active判断信号是否更新。 if (a'active and b'active) then 机器提示错误 不支持。 请问在不增加信号的前提下,能不能判断信号

发表于 03-04 15:11

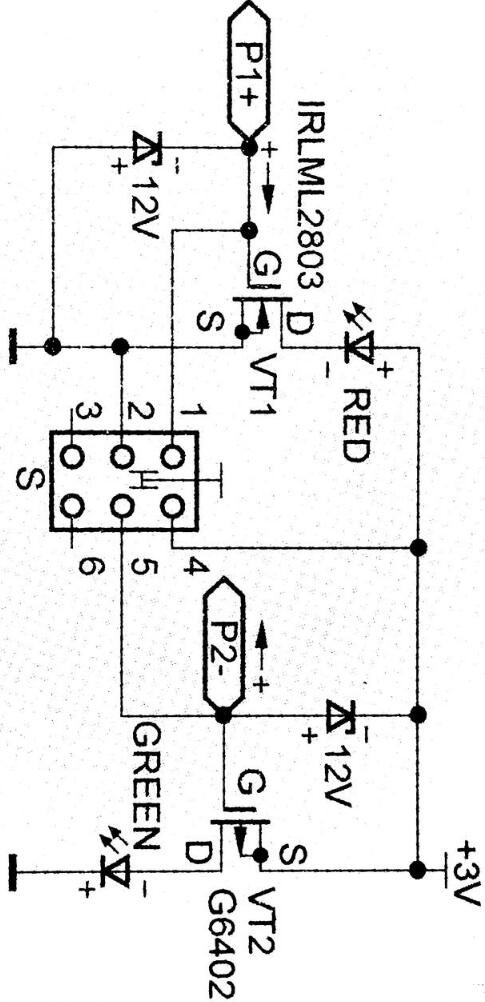

请教下!这个电路如何防止静电

`我用光耦(PC817)搭了个桥式电路,控制LED灯。这样不管LED灯哪个方向都能点亮!A B点是两个引线引出接在机台上面的LED(绝缘)。但实际应用过程中,光耦经常被静电打坏。有啥好的方法?1:加TVS?2:用专门的桥式芯片?

发表于 03-25 15:13

STM32Fxxxx芯片需要在焊接时防静电吗?

最后1片也是在立创买的,其他的都不能被识别。立创的比前边的两个商店贵一倍,包装也比较正规点,一个芯片一个大点的纸盒,上下各一片防静电泡沫塑料。立创公司在盒子上明确写了“静电”两字,我就

发表于 12-27 09:05

请问这个电路如何防止静电?

我用光耦(PC817)搭了个桥式电路,控制LED灯。这样不管LED灯哪个方向都能点亮!A B点是两个引线引出接在机台上面的LED(绝缘)。但实际应用过程中,光耦经常被静电打坏。有啥好的方法?1:加TVS?2:用专门的桥式芯片?

发表于 12-27 10:49

系统层级静电放电与芯片层级静电放电有什么差异

军方所制定的人体静电放电模型最具代表性,又称之为芯片层级静电放电测试。而针对终端消费者所使用的电子产品,则以IEC 61000-4-2所制定的人体静电放电模型为测试主流,这就是一般认知

发表于 07-25 06:45

图文并茂Layout对开关电源的重要性

图文并茂Layout对开关电源的重要性。1、静电打坏IC。1.1 VCC电容跟VCC脚越近越好。如下图VCC电容与IC脚太远,静电和耐压都会打坏IC,当然这还要看

静电对LED的危害及LED防静电常识

。蓝宝石衬底的蓝色芯片其正负电极

均位于芯片上面,间距很小;对于 InGaN/AlGaN/GaN 双异质结,InGaN 有源层仅

几十纳米,对静电的承受能力很小,极易被

发表于 05-23 14:25

•5次下载

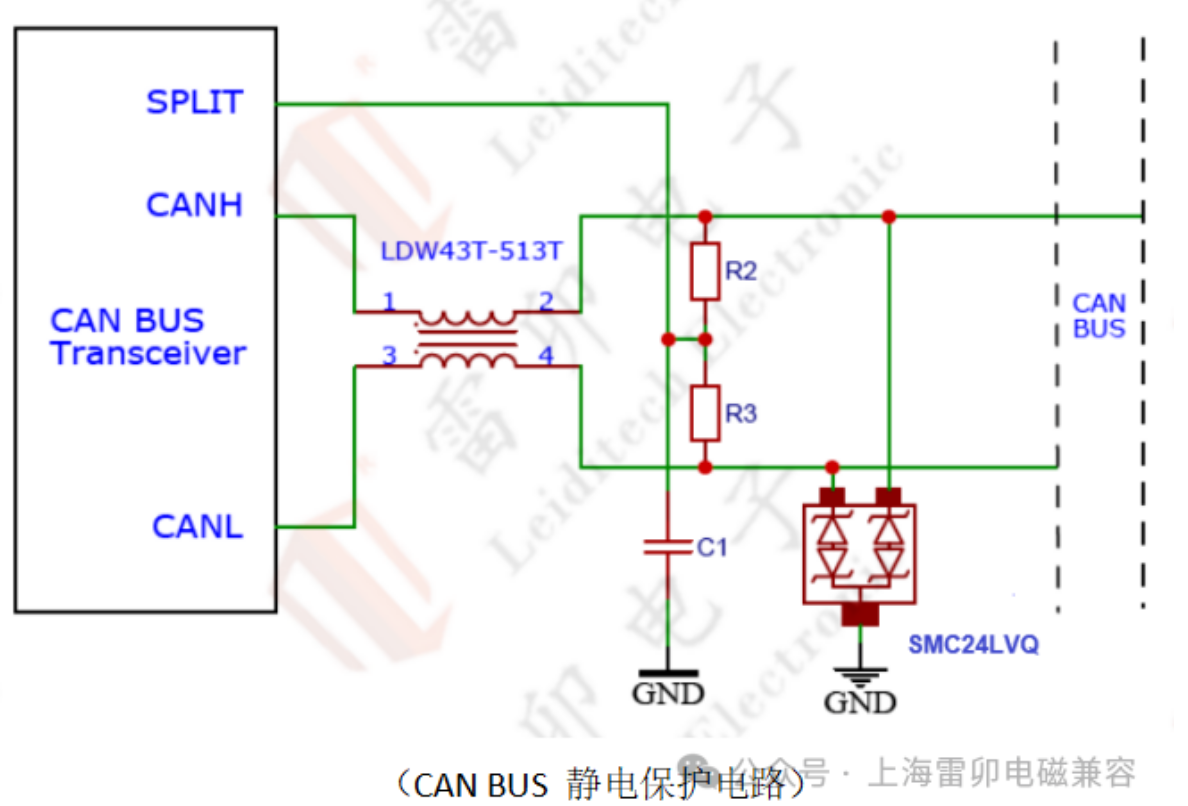

AMEYA360:上海雷卯电子CAN BUS芯片静电浪涌击穿整改方案

工程师们都放置ESD二极管以作静电浪涌防护用,但还会出现IC被静电浪涌打坏,造成不能正常工作,这是什么原因? 一.放置ESD二极管为什么后端还会损坏的原因 上海雷卯

Canbus芯片静电浪涌击穿整改方案

中工程师们都放置ESD二极管以作静电浪涌防护用,但还会出现IC被静电浪涌打坏,造成不能正常工作,这是什么原因? 一、 放置ESD二极管为什么后端还会损坏原因

如何判断芯片被静电打坏

如何判断芯片被静电打坏

评论