本系列,我们的产品技术专家将结合电子系统设计软件的新功能和应用热点进行选题,本期主题为Xpedition Schematic Analysis 原理图完整性分析工具简介,敬请参阅!

如今的原理图设计变得非常复杂,无法仅凭目视评审进行全面检查。如果没有适当的原理图验证,可能会导致额外的硬件重新设计、延迟上市时间、增加现场退货率以及降低产品质量的风险。通过进行原理图完整性分析,可以避免潜在的设计缺陷和边际性问题。

Xpedition Schematic Analysis提供了预定义的检查和广泛的智能组件模型库,能够自动对原理图上的所有网络进行全面检查,从而节省设计团队数百小时的目视检查和实验室调试时间。

Xpedition Schematic Analysis原理图完整性分析可以集成多个板设计的数据进行系统级验证。它是一种基于规则且不限定CAD软件的技术,可以与您的设计同时进行,提高设计质量,而不会影响硬件开发的进度。

使用Xpedition Schematic Analysis,可以在产品设计的早期阶段通过原理图网表和BOM来查找原理图上的缺失或错误,从而避免在项目晚期浪费时间和材料。

由于对原理图上的所有网络进行全面检查,Xpedition Schematic Analysis有可能发现仅使用仿真工具无法察觉的问题。以下是一些示例:

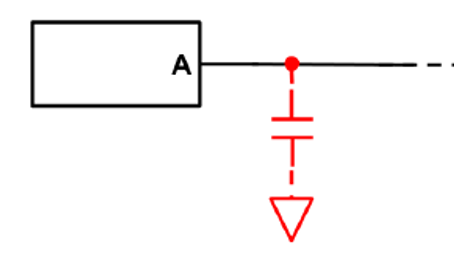

例如,某个IC的管脚根据厂家规范需要连接一个电容到地,如果在原理图中未进行连接,将会触发错误提示。

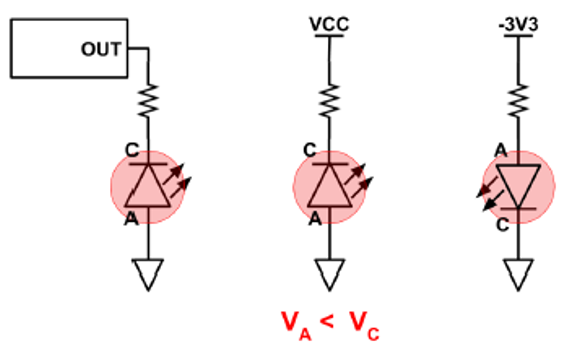

或者如下图所示的二极管方向验证。

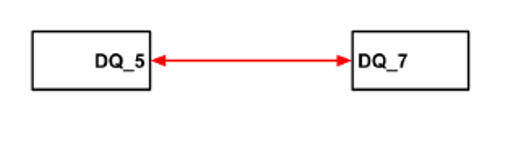

又或者是总线上的错误。如下图所示,一个IC的bit 5连接到另一个IC的bit 7。

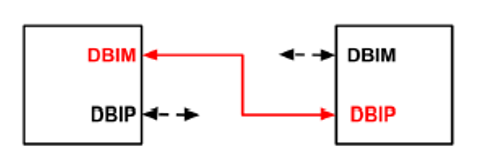

还有差分管脚验证,例如下图所示的差分对的正负两端接反的情况。

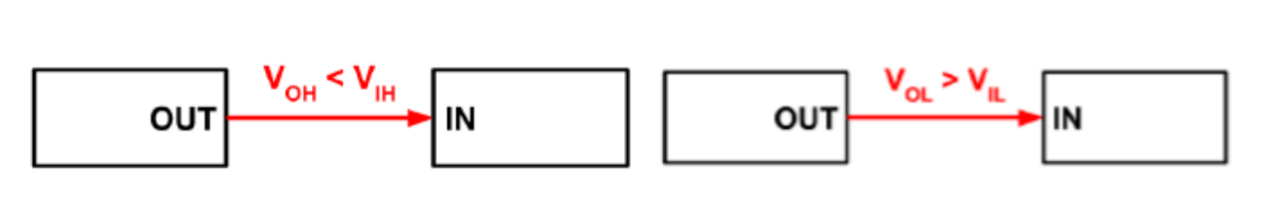

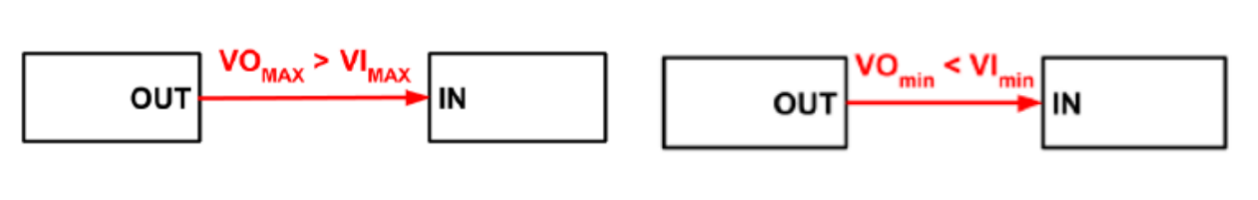

此外,还可以验证组件的管脚电压参数,包括最大、最小和逻辑阈值。例如,过高或过低的输出电平可能导致接收端的逻辑位误判:

或者过高或过低的电平输出可能导致接收端组件损坏:

要进行这些类型的检查,需要有相应的组件模型来提供每个管脚的特性和要求。Xpedition Schematic Analysis提供了一个包含数百万个组件的在线模型库,方便用户使用。对于特殊的组件,用户还可以利用付费咨询服务或使用Xpedition Schematic Analysis提供的模板自行对有源或无源组件进行建模。

通过在原理图捕捉过程中而不是之后进行全自动化的原理图验证,开发过程可以向左移动。其中一个明显的好处是减少硬件重新设计,从而缩短设计周期和降低成本。

-

原理图

+关注

关注

1298文章

6346浏览量

234301 -

电子系统

+关注

关注

0文章

417浏览量

31178 -

总线

+关注

关注

10文章

2888浏览量

88138 -

Xpedition

+关注

关注

0文章

19浏览量

8446

原文标题:Xpedition Schematic Analysis原理图完整性分析工具简介

文章出处:【微信号:gh_a47ef5dbc902,微信公众号:西门子PCB及IC封装设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCB信号完整性分析入门

信号完整性与电源完整性的仿真分析与设计

Altium Designer中进行信号完整性分析

【下载】《信号完整性分析》

基于信号完整性分析的PCB设计流程步骤

电源完整性分析

Mentor Expedtion PCB信号完整性分析入门

信号完整性与电源完整性仿真分析

信号完整性分析

基于信号完整性分析的PCB设计解析

Xpedition Schematic Analysis原理图完整性分析工具简介

Xpedition Schematic Analysis原理图完整性分析工具简介

评论