当今世界,人工智能的迅猛发展已经成为热门话题,当人们都在关注它将如何改变我们未来生活的时候,身处芯片业的工程师们开始关注如何在有限的物理空间内,将芯片的性能提升到更高的水平,以及如何在单位体积内集成更多的晶体管,以满足高性能计算的需求;人工智能对高性能计算的需求是无止尽的,然而,当单位体积内集成的晶体管数量受到物理极限的限制时,我们必须寻找新的解决方案来延续其扩展性。

那么,新的方向在哪里呢?答案就在异构集成、先进封装或者Chiplet等技术上。这些技术正在悄然兴起,它们将为芯片制造业带来新的机遇和挑战。异构集成技术可以将不同类型、不同功能的芯片模块集成在一起,从而实现更高的性能和效率。先进封装技术则可以将多个芯片封装在一起,形成一个更大的芯片,从而提高算力。异构集成、先进封装或者Chiplet等技术的应用,将为芯片制造业带来新的生机,也将进一步推动人工智能等技术的发展 。

1芯片和先进封装的制程挑战

面临物理极限带来的挑战和对高性能计算的迫切需求,异构集成和先进封装技术应运而生。如果我们把单位体积内集成的晶体管数量理解成Vertical (纵向发展),异构集成就是Horizontal(横向发展),那么我们可以利用更大的横向扩展并联合更多芯片来弥补单颗芯片晶体管数量的限制。

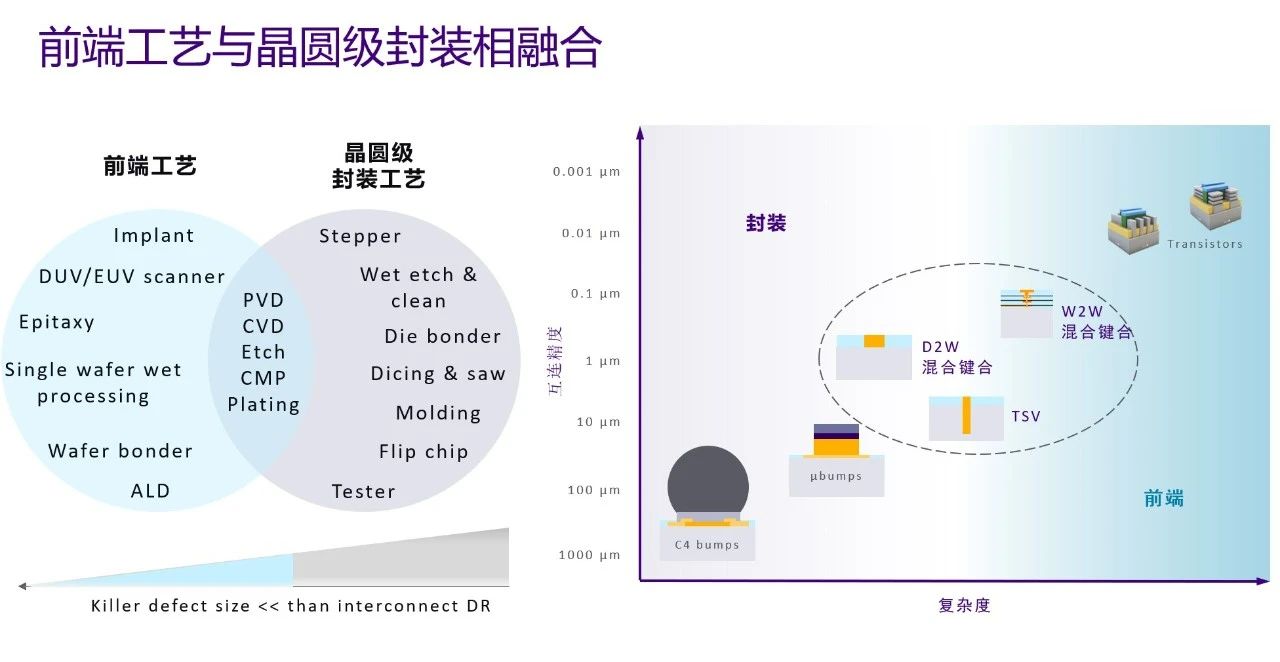

异构集成可以有效延续高性能计算的扩展需求,但在实际制造过程中并非一帆风顺,否则也不会成为当下的热门话题。简单多芯片组合封装并不是高新科技,然而把所有尖端的芯片集成一体并保证其性能数倍增长,这种集成看似简单可行,实则不得不靠牺牲部分良率才能有限获得,这主要是由于采用新的制造工艺、新的材料,以及FE(前道)和BE(后道)的制程混合应用(如图1)等带来的挑战;这种制造工艺虽然从性能上可以维持摩尔定律的发展,但是也带来更多制造和良率的挑战(图2)。

图1

图2

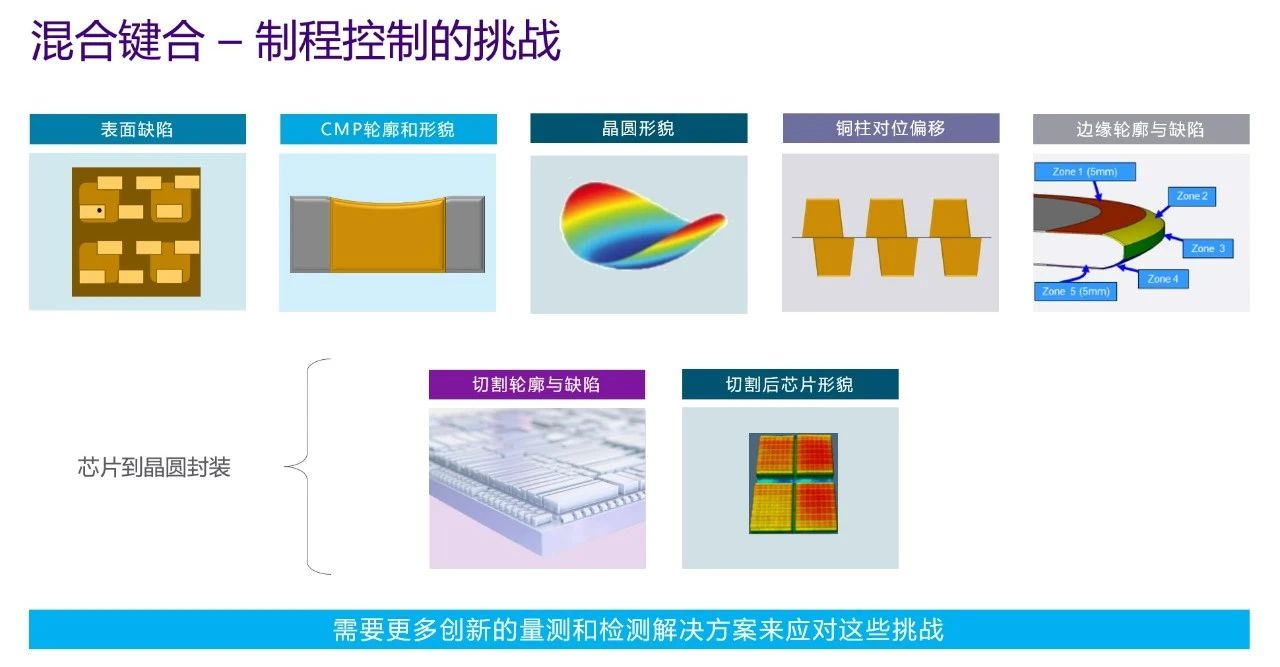

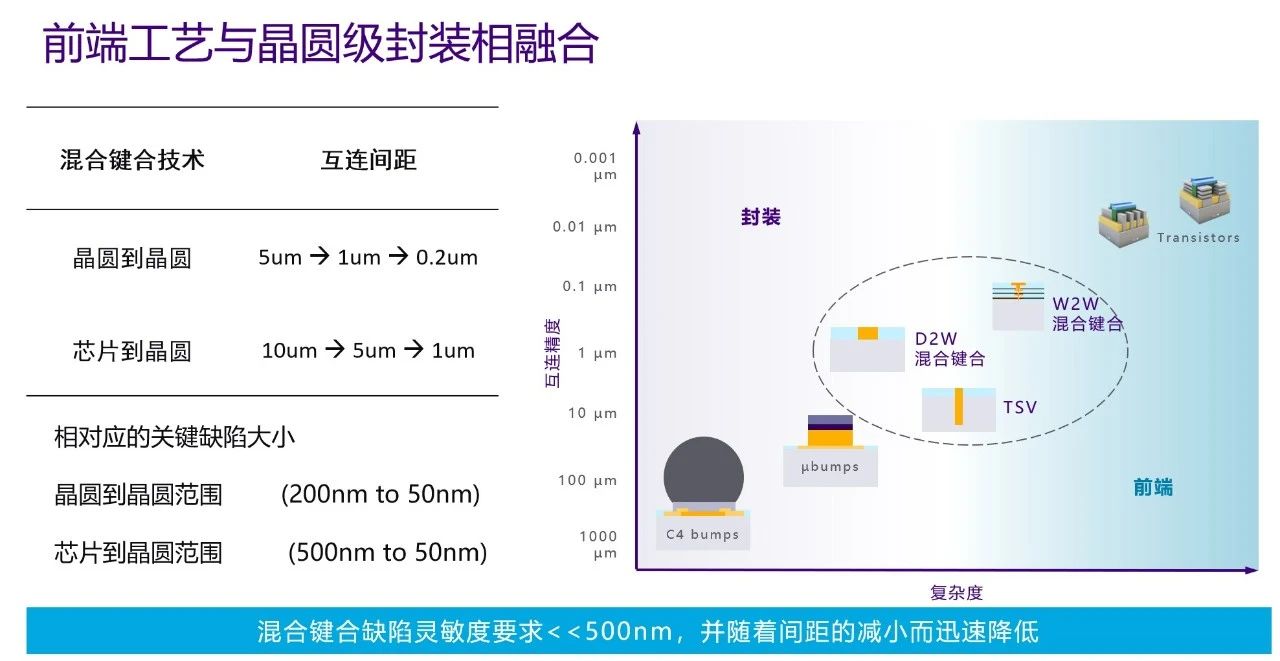

Bumping 连接密度带来的挑战:当横向扩展使单位面积内的芯片数量得到提升,接下来需要去解决与之匹配的芯片到芯片的传输速率问题,先进封装的混合键合Bumping制程,就是其中的方案,Bumping间距越来越小(图3),这种封装技术虽然让芯片之间具备更短的连接路径和更多的连接数量,但是如何互连KGD(无缺陷芯片)并不容易;特别是当前异构集成制造生态还没有完全成熟并还在不断演变的状况下,需要更可靠的制程控制与良率管理解决方案来帮助其稳定的投入量产, 混合键合成为异质集成的关键转折。

图3

2芯片和先进封装制程控制解决方案

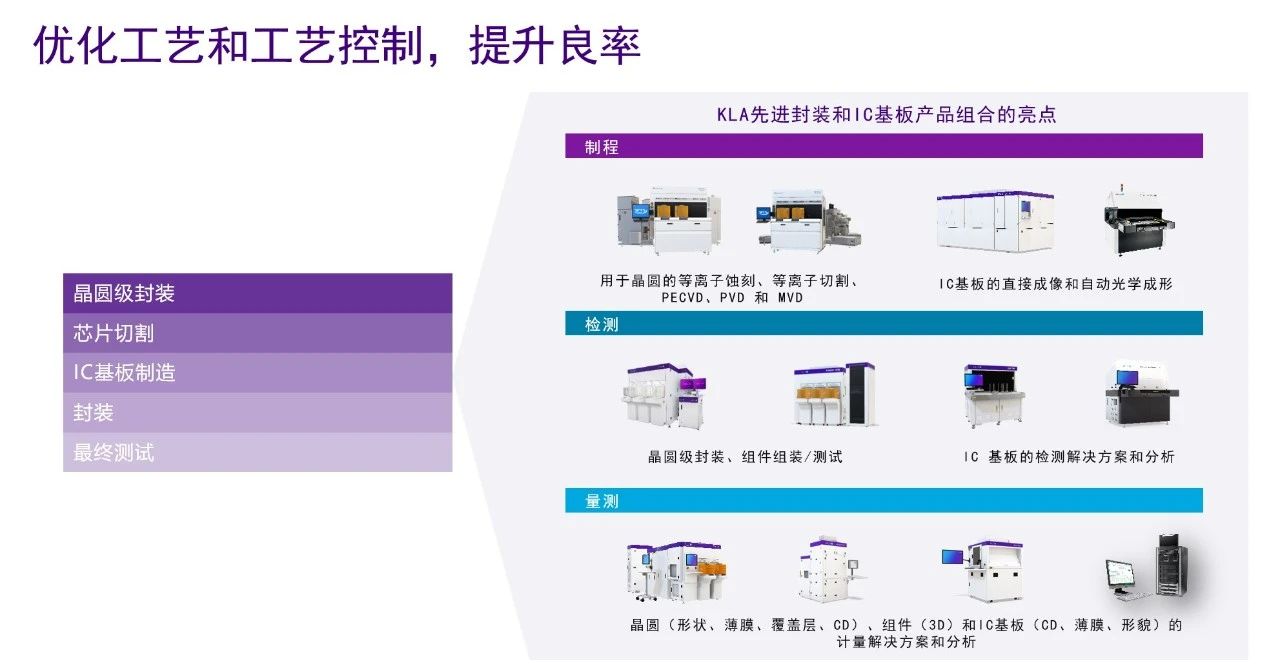

异构集成和先进封装的混合键合工艺是扩展各类封装与应用的关键技术。混合键合的主要优势是通过提高互连密度从而提升速度、带宽和电源效率;混合键合的 W2W(晶圆到晶圆)集成是用于制造CMOS图像传感器和3D NAND的关键;混合键合的D2W(芯片到晶圆)集成多用于 AI 逻辑芯片和高带宽存储器。这些在各个工艺段复杂的制程,给最终成品良率带来巨大的挑战,怎样保证最终的成品良率并可批量生产,制程控制与良率管理生产工具至关重要。KLA提供专业的、通过产业界充分验证过的制造、检测与量测解决方案(图4)

图4

3结语

如果人工智能的高性能计算需求引领了异构集成和先进封装的浪潮,那么克服良率和产能的挑战就是KLA开发创新型技术不可或缺的一部分,我们可以想象因一个集成芯片的缺陷而导致昂贵的多芯片封装报废或者额外的筛查,这种损失是不可接受的。KLA致力于研发封装制程综合解决方案,包括制程方案:保证制造过程中的良率;量测方案:对生产工艺过程量化分析控制,确保新产品和量产中的工艺误差时刻在规格范围内;检测方案:有效管理每一片在制产品的良率,从而确保最终良率长期可管可控。KLA将这些经验与广泛的良率管控、检测和量测系统相结合,致力于成为先进封装制造商们的理想合作伙伴。

-

芯片

+关注

关注

458文章

51526浏览量

429500 -

晶圆

+关注

关注

52文章

5021浏览量

128609 -

chiplet

+关注

关注

6文章

437浏览量

12669 -

先进封装

+关注

关注

2文章

437浏览量

338

原文标题:芯片和封装技术发展趋势

文章出处:【微信号:KLA Corporation,微信公众号:KLA Corporation】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

芯片和先进封装的制程挑战和解决方案

芯片和先进封装的制程挑战和解决方案

评论