CMOS(cornplementary MOS)由成对的互补p沟道与n沟道MOSFET所组成.CMoS逻辑成为目前集成电路设计最常用技术的缘由,在于其有低功率损耗以及较佳的噪声抑止才干.事实上,由于低功率损耗的需求,目前仅有CMOS技术被运用于ULSI的制造.

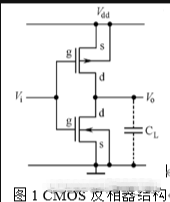

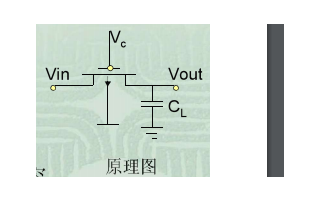

CMOS反相器

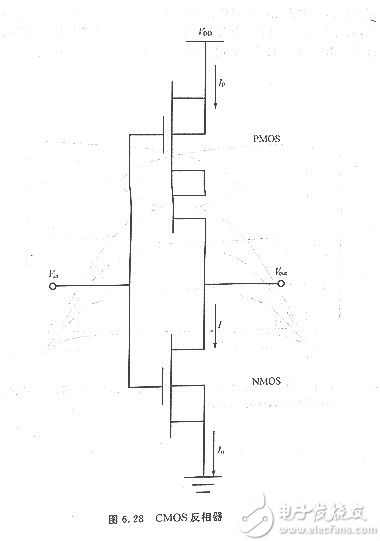

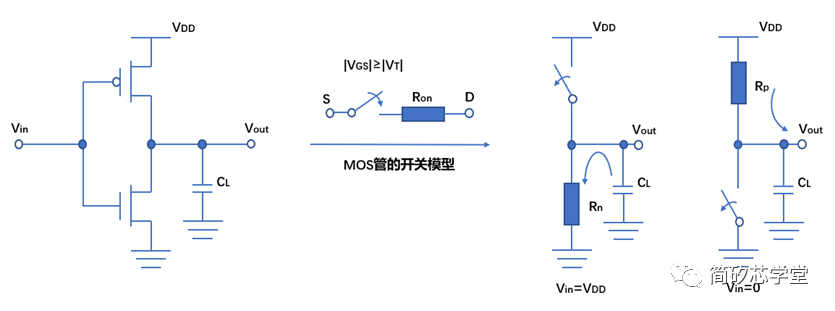

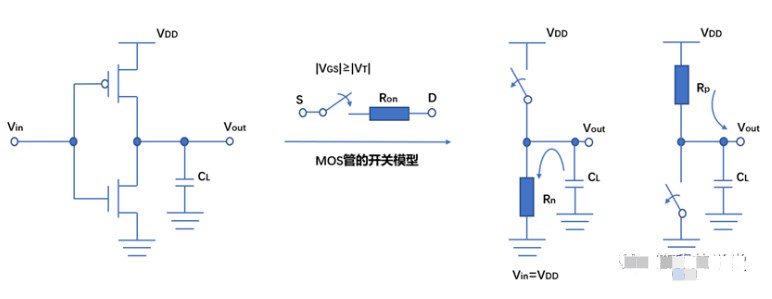

如图6. 28所示,CMOS反相器为CMOS逻辑电路的基本单元.在CMOS反相器中,p与n沟道晶体管的栅极衔接在一同,并作为此反相器的输入端,而此二晶体管的漏极也连接在一同,并作为反相器的输出端.n沟道MOSFET的源极与衬底接点均接地,而p沟道MOSFET的源极与衬底则衔接至电源供应端(VDD),需留意的是p沟道与n沟道MOSFET均为增强型晶体管,当输入电压为低电压时(即vin=O,VGsn=o

因此,输出端经过p沟道MOSFET充电至VDD,当输入电压逐渐升高,使栅极电压等于VDD时,由于VGSn=VDD>VTn,所以n沟道MOSFET将被导通,而由于|VGSp |≈O<|VTp|,所以p沟道MOSFET将被关闭.因此输出端将经n沟道MOSFET放电至零电势,

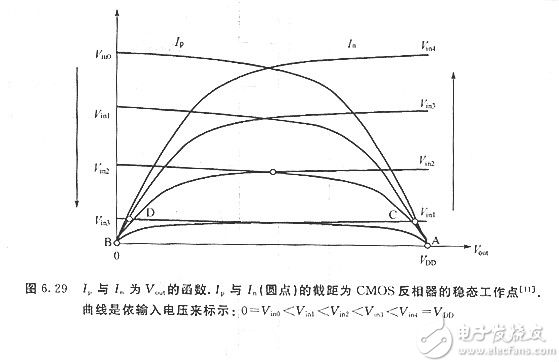

欲更深化天文解CMOS反相器的工作,可先画出晶体管的输出特性,如图6.29所示,其中显现Ip以及In为输出电压(Vout)函数.Ip为p沟道MOSFET由源极(衔接至VDD)流向漏极(输出端)的电流;In为n沟道MOSFET由漏极(输出端)流向源极(衔接至接地端)

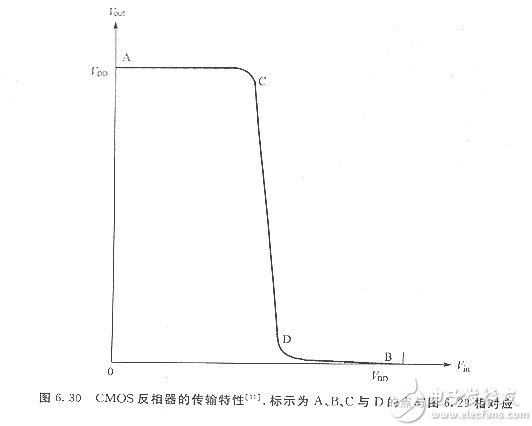

的电流.需留意的是在固定Vout下,增加输入电压(vin)将会增加In而减少Ip,但是在稳态时,In应与Ip相同,关于给定一个Vin可由In(Vin)与Ip(Vin)的截距,计算出相对应的Vout如图6. 29所示.如图6.30所示的Vin-Vout曲线称为CMOS反相器的传输曲线.

CMOS反相器的一个重要的特性是,当输出处于逻辑稳态(即Vout=或VDD)时,仅有一个晶体管导通,因此由电源供应处流到地端的电流非常小,且相当于器件关闭时的漏电流.事实上,只需在两个器件暂时导通时的极短暂态时间内才会有大电流流过,因此与其他种类如n沟道MOSFET、双极型等逻辑电路相比,其稳态时的功率损耗甚低.

-

CMOS

+关注

关注

58文章

5735浏览量

236050 -

CMOS反相器

+关注

关注

0文章

19浏览量

6794

发布评论请先 登录

相关推荐

virtuoso中进行CMOS反相器和静态寄存器的电路设计

CMOS反相器构建Big Muff

CMOS反相器工作原理及传输特性

什么叫CMOS电流源(漏)反相器?它有什么优点?

为什么可以用CMOS反相器作为逻辑门电路缓冲级?

影响CMOS反相器特性的因素

TTL反相器和CMOS反相器的区别

CMOS反相器的工作原理和应用

详细讲解cmos反相器的原理及特点

详细讲解cmos反相器的原理及特点

评论