引言

射频收发系统需要一个高精度、低相位噪声的频率参考源。在实际的应用中,频率参考源一般都采用振荡器来实现,高精度低相位噪声的晶体振荡器具有十分明显的优势。而为了节约成本,提高频率综合器输入基准时钟的相位噪声性能,实现射频收发系统的单芯片化,把晶体振荡器除晶体之外的部分都集成到片上就成了大势所趋。

本文采用SMIC0.18μm工艺设计了一种20MHz的晶体振荡器。该晶体振荡器由振荡主电路、振荡幅度控制电路两部分组成,具有较好的相位噪声性能和较低的功耗。除石英晶体外,振荡器电路全部集成在片上实现,可以作为整个射频芯片的高精度频率源。

1 电路原理及设计

1.1 石英晶的模型和原理

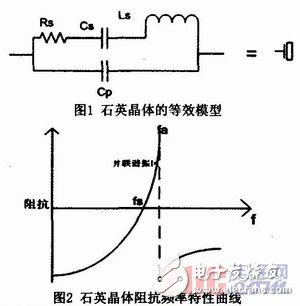

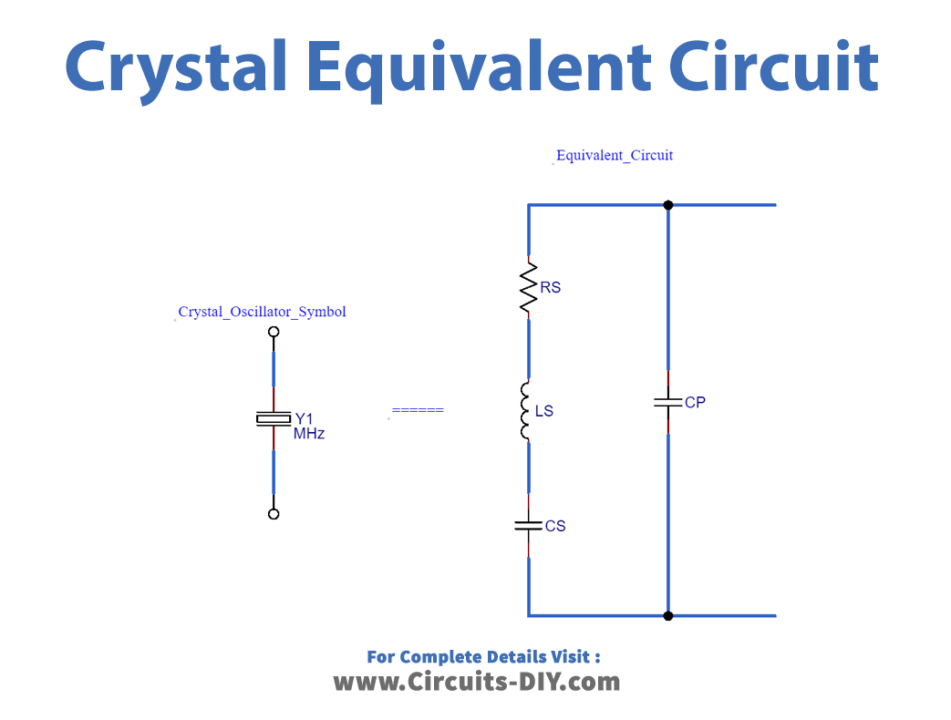

本文采用的谐振晶体是石英晶体。按一定的方向将石英切成很薄的晶片,再将晶片两个表面抛光涂银并引出管脚加以封装,就制成了石英晶体。这种石英晶体薄片受到外加交变电场的作用时会产生机械振动,当交变电场的频率与石英晶体的固有频率相同时,振动便变得很强烈,这就是晶体谐振特性的反映。石英晶体的电子模型如图1所示,是串并联的LRC电路,其阻抗表达式为:

RsLsCs组成串联谐振支路,决定了串联谐振频率,串联电阻Rs模拟晶体的等效电阻,Cp是晶体两块平板之间的电容,也包括了封装电容和焊接电容。

本文采用的20M晶体模型为:Ls=6.3mH,Cs=10fF,Rs=40Ω,Cp=5pF。

图1石英晶体的等效模型

图2表示的是晶体的频率特性,可以看到该晶体存在着串联谐振和并联谐振两个谐振点,在振荡时晶体就工作在这两个谐振点之间,表现为电感特性。

1.2 晶体振荡器的基本原理

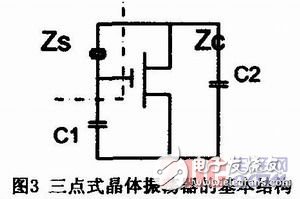

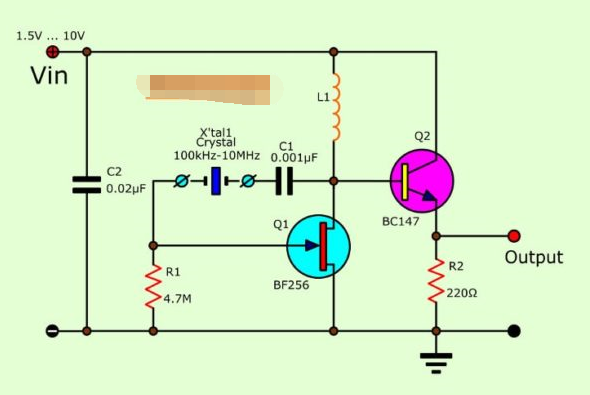

晶体振荡器的实现方式有很多种,最常见的是三点式结构,如图3。

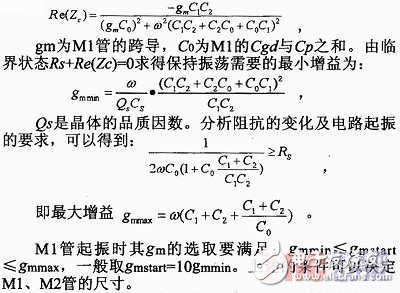

根据巴克豪森准则,采用负阻模型来分析振荡的启动条件:一个振荡器如果要起振,所有的阻抗之和必须小于等于0。对于晶体振荡器来说,工作在振荡频率时,除晶体之外的其余电路必须表现为一个负阻以补偿晶体的串联电阻Rs。

Zs表示的是晶体的串联支路的阻抗,Zc为其余电路阻抗之和,满足振荡的临界状态为:Zs+Zc=0,

由此可以得到能起振的gm的最小值。

根据晶体接入点偏置点的不同,晶体振荡器可以分为皮尔斯(Pierce)振荡器、科尔皮兹(Colpitts)振荡器、桑托斯(Santos)振荡器三种结构。本文设计的晶体振荡器采用的是Santos结构。Santos结构中晶体从主振荡管的栅端接入,由于是单端接入,所以可以节约引脚,另外Santos结构也比较容易起振。

1.3 具体电路设计

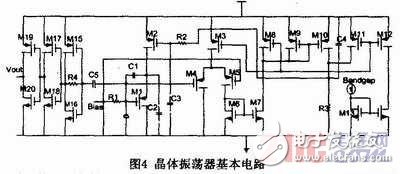

本晶体振荡器的基本电路如图4所示。

振荡器的核心振荡电路由M1、M2、C1、C2以及石英晶体组成。晶体管M1作为振荡主管,M2管作为偏置电流源,振荡器的输出在M1管的栅端。为了得到比较理想的频率偏移,C1、C2都取得比较大,分别为5p、10p。利用上节提到的负阻抗模型,对该电路进行分析,可得:

当振荡器起振之后,振荡波形幅度会不断增大,一直到振荡器件出现饱和为止。这期间可能会引起MOS管的击穿,因此需要设计一个振幅控制电路。本文设计的振幅控制电路由M3~M14组成。M4、M5是一对非对称差分管,M4的宽长比远大于M5,M3是它们的偏置电流源。由于直流偏置一样,这样在起振的时候M5的电流远小于M4,M8可以提供该电流,此时M9、M10关断只有很小的亚阈值电流。R3的电流只由M11、M12、M13、M14以及带隙基准组成的电流镜提供,M2的栅源电压VSG2=VDD-R3I11,所以M2能够提供较大的电流,使振荡器在较大的正反馈增益下迅速起振。

在起振之后输出电压振幅不断增大,M4、M5的反向交流电流也按尺寸比例分配,使通过两者的平均电流不断接近,当振荡幅度达到一定大小时,两个管子平分M3的电流。此时M8不足以提供M5的电流,M9就进入饱和态导通补足所需的电流,同样M10也导通,所以流过R3的电流增大变为I10+I11,M2的栅源电压变小,从而M2的电流下降,振荡器趋于稳定,输出幅度稳定下来。R3和C4决定振幅控制电路的时间常数,它的值太小会引入幅度波动,太大则会使响应过慢,需要进行折衷考虑。

相位噪声是晶体振荡器最重要的指标,它直接影响锁相环回路的工作性能,决定了芯片对射频信号接收与处理灵敏度,甚至决定了整个电路能否正常工作。通过仿真和分析可知,振荡器电路的主要噪声源是电流镜M11、M12、M13、M14的闪烁噪声,通过影响M2的栅源电压,把噪声传递到主振荡电路,从而影响振荡输出的相位噪声。因此本文提出在M2的栅端添加一个由R2、C3组成的RC滤波器,滤掉振幅控制电路的噪声,显著地提高相位噪声指标。选取R2、C3的值时,要综合考虑滤波器的带宽及电阻电容的面积。

晶振的输出缓冲级由隔直电容C5、自偏置结构R4、M15、M16、以及M17、M18、M19、M20组成的反相器链构成,可以得到全摆幅的方波输出。

2 电路版图及仿真

电路使用SMIC 0.18μm工艺实现,图5是该电路芯片的显微镜照片,面积约为550×185μm。

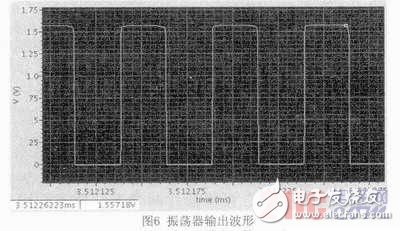

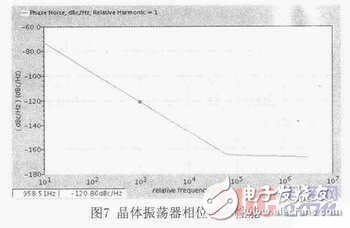

利用Cadence Spectre软件工具对晶体振荡器进行仿真,其输出波形如图6所示的方波,峰峰值为1.56V,起振时间约为0.6ms。图7表示的是振荡器的相位噪声性能,在偏离中心频率1kHz、10kHz、1MHz处的相位噪声分别为:-121dBc/Hz、-145dBc/Hz、165dBc/Hz。

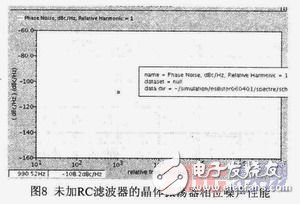

对加RC滤波器之前的晶体振荡器进行仿真,起振时间振荡幅度都基本没有改变。但其相位噪声性能如图8所示,在偏离中心频率1kHz、10kHz、1MHz处的相位噪声分别为:-110dBc/Hz、-127dBc/Hz、-143dBc/Hz。

可见,滤波器显著提高了晶体振荡器的相位噪声性能,达到了设计的目的。

3 结论

本文使用SMIC 0.18μm工艺,设计了一种20MHz单端晶体振荡器,除石英晶体外所有电路都集成在片上。从仿真结果分析,本文设计的晶体振荡器频率精度高,相位噪声优良,启动时间短,面积也较小,满足集成射频电路的应用要求。

-

晶体振荡器

+关注

关注

9文章

636浏览量

29295 -

SMIC

+关注

关注

0文章

21浏览量

20002

发布评论请先 登录

相关推荐

基于SMIC工艺设计的晶体振荡器电路原理

基于SMIC工艺设计的晶体振荡器电路原理

评论