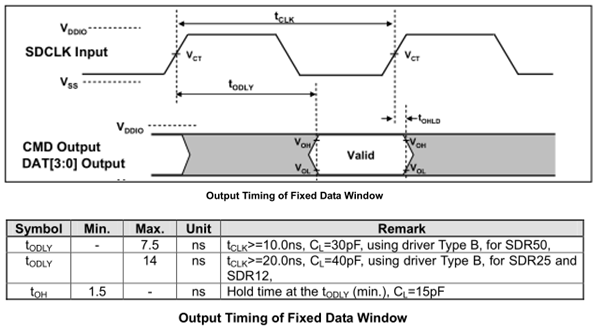

固定数据窗口输出时序(SDR12、SDR25、SDR50)

固定数据窗口插卡输出时序如下图所示,SDR12、SDR25、SDR50的输出时序

有效窗口由输出延迟(topy)的最小值和最大值指定。

无论温度和电压如何变化,与SDCLK同步的有效数据窗口都是可用的。

输出有效窗口由tclk-todly +toH计算。

主机可以通过延迟SDCLK创建采样时钟。

下图中voH表示最小值,VoL表示最大值。

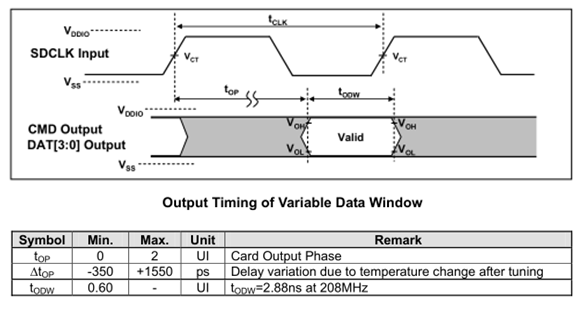

可变窗口输出时序(SDR104)

可变数据窗口卡的输出时序如下图所示。

引入Top来表示输出延时。不包括包括所有延迟变化的对比todly中的长期温度漂移。

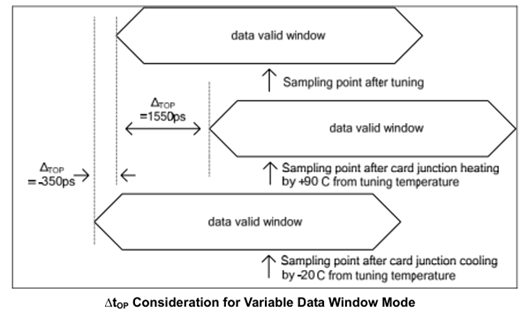

温度漂移用△Top表示。顶部初始化后,可以在0到2UI的范围内。在确定数据采样点时,应考虑长期漂移,而长期漂移主要取决于温度漂移。

输出有效数据窗口(todw)是可用的,而不管漂移(Top),但数据窗口的位置随漂移而变化。

下图中的voH为最小值,VoL为最大值。

卡△Top是输出有效窗口(Topw)从上一个系统的总允许位移调谐程序

卡△Top=1550pS结温AT= 90℃在操作过程中。

卡△Top=-350pS工作时结温△T=-20℃时,

当卡温度在工作过程中从-25℃到125℃变化时,△Top的范围为2600ps。

需要注意的是,图Output Timing of Fixed Data Window两组参数是同一输出电路在不同条件下的输出时序。需要两个输出时序图,因为根据主机实现,假定有两种类型的读取数据采样方法。这些输出时序在测试电路测量点定义,由输出计时定义的有效窗口包括由卡创建的CMD和DAT[3:0]之间的倾斜。

主机设计者应该考虑到主机传输路径会增加一些信号完整性引起的噪声、总线成员之间的倾斜和时序误差。主机输入的期望Todw大于0.50UI。

应用注意:主机需要考虑数据窗口的漂移。

调优过程完成后的温度漂移转化为有限的输出有效窗口漂移(△Top)。

主机设计人员应该考虑到这种漂移,并正确设计以避免受到这种漂移的影响。

在睡眠后激活调谐程序是一种很好的做法。

主机可以采用不同的技术来克服温度效应(包括降低工作频率)。

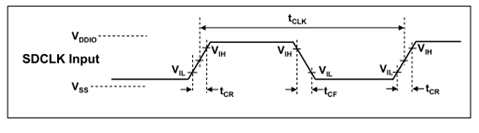

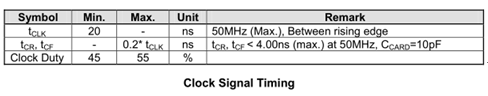

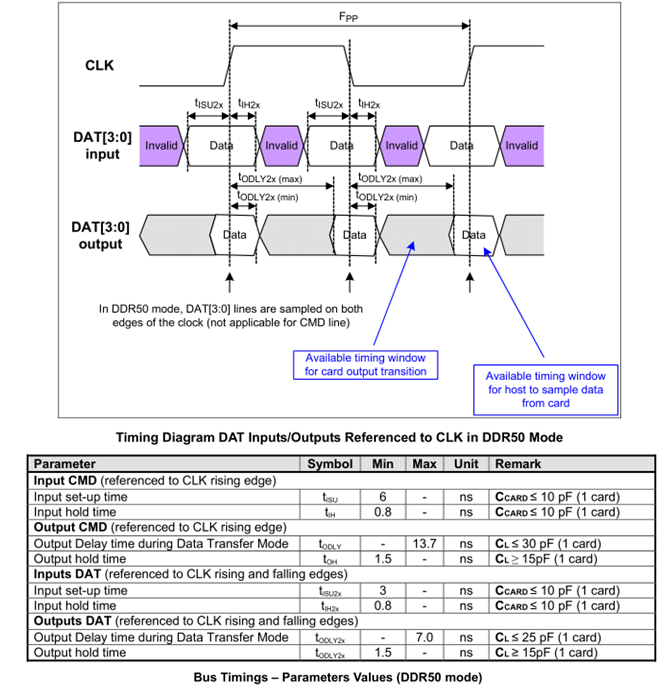

DDR50模式下总线时序规范

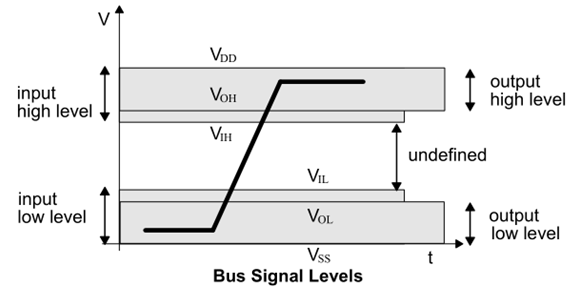

时钟时序时钟信号时序要求如下图所示,具体参数如下图所示。

主机需要定时。Tclk用来定义上升/下降的时间。

升降时间应小于0.2* tclk。SDCLK输入应满足所有可变条件下的时钟时序,并在CMD和DAT[3:0]处于安静状态(不切换)时尽可能接近SD插口引脚到卡。

下图中ViH代表最小值, ViL代表最大值.

总线DDR50时序

-

NAND

+关注

关注

16文章

1682浏览量

136158 -

信号

+关注

关注

11文章

2791浏览量

76761 -

时钟

+关注

关注

10文章

1733浏览量

131480

发布评论请先 登录

相关推荐

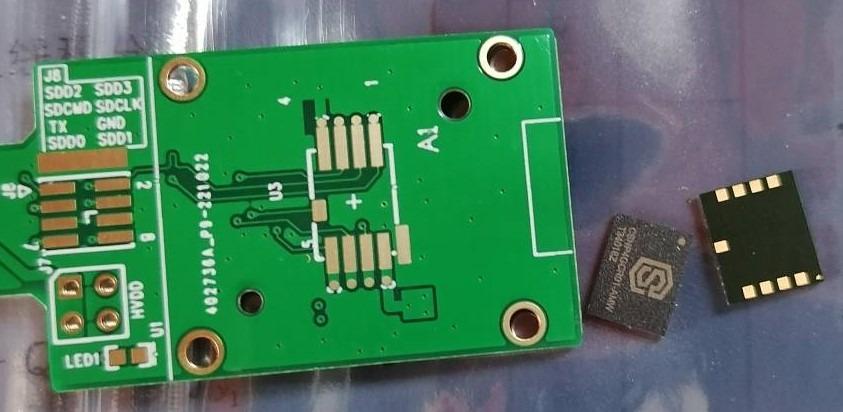

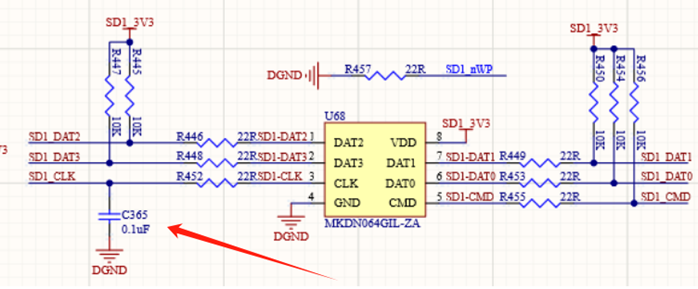

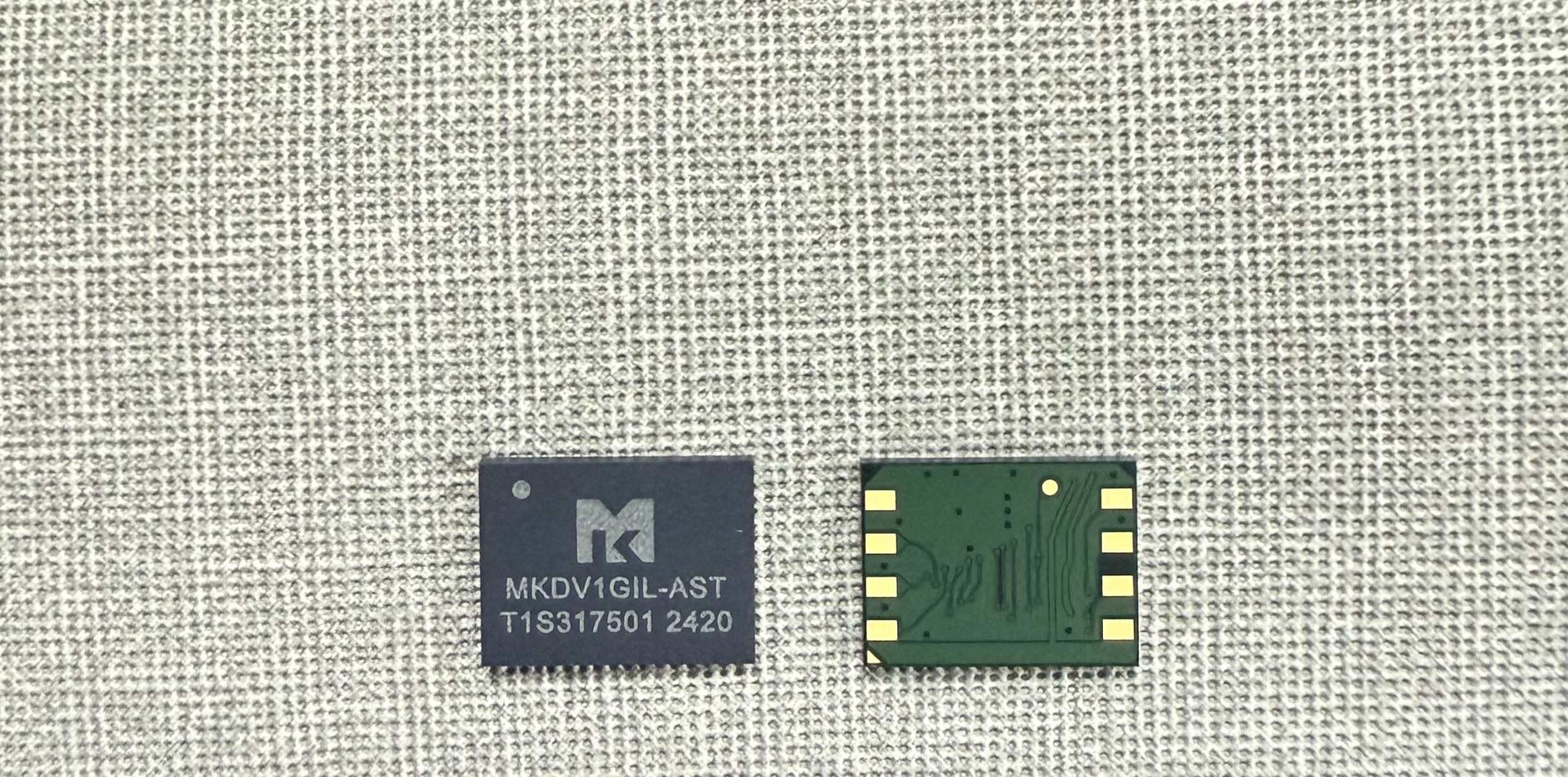

基于FPGA的SD卡的数据读写实现(SD NAND FLASH)

MK SD NAND 1.8v IO电压应用分享

什么是SD NAND存储芯片? SD NAND与TF卡的区别

SD NAND的CLK引脚的注意事项和走线规范

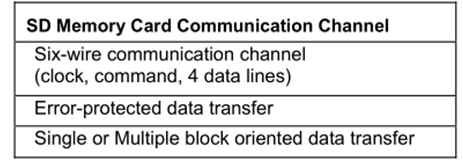

瀚海微SD NAND应用之SD协议系统功能和概念 1 基础知识

瀚海微SD NAND之SD 协议(29)硬件接口

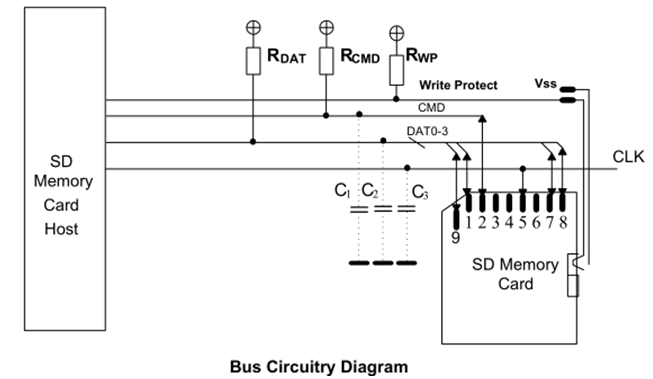

瀚海微SD NAND之SD 协议(31)总线的信号和时序

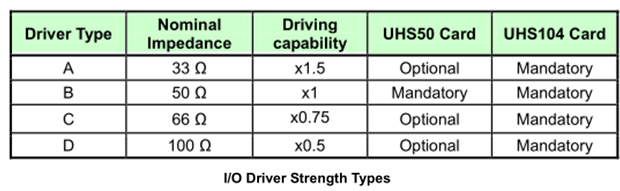

瀚海微SD NAND之SD 协议(32)1.8V信令的驱动强度和总线时序

瀚海微SD NAND之SD 协议(33)1.8V供电的驱动强度

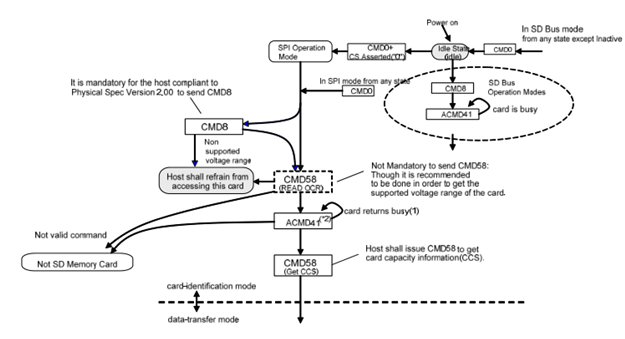

瀚海微SD NAND之SD 协议(36)SPI模式

瀚海微SD NAND之SD 协议(37)SPI总线保护和读写

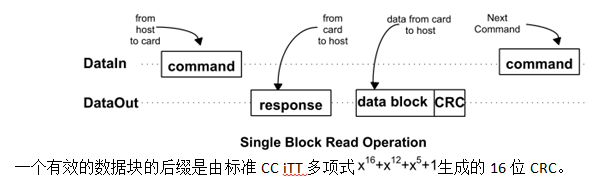

瀚海微SD NAND之SD 协议(39)SPI模式 Transaction Packets

瀚海微SD NAND之SD 协议(42)SPI总线时序

瀚海微SD NAND之SD 协议(34)1.8V信号的时序

瀚海微SD NAND之SD 协议(34)1.8V信号的时序

评论