现在做电源,除了效率以外,空载或者待机功耗也变得越来越重要了。这不仅是因为各种各样的能效标准的执行,也确实很符合实际应用的需求,因为大部分的用电设备都长期工作在待机状态。以离线式的AC/DC电源为例,不同的应用要求不一样,有500mW、300mW、再到100mW,甚至是很多充电器所追求的10mW以下。

实际上把待机功耗做低也不是什么太高深的事儿,不需要高等数学频谱分析什么高大上的理论,基本只是需要一些经验,有时要做些妥协。这里就把和大家分享一些本人的浅见。

先从AC输入端说起, 这里最大的损耗就来自于X电容放电的电阻。大部分的安规标准都要求1s内把X电容的电压放到安全电压以下。这样容值越大,放电的电阻就越小,损耗也就越大。举个例子,.33uF的电容并个3M的电阻,230Vac条件下的空载损耗就有~18mW。

也就是说为了节约这部分功耗,X电容要尽量小,这个节约成本倒也是一致的。但是必要的情况下,为了降低损耗也不得不多花点钱了,也就是用专门的X电容放电芯片,比如CAPZero或者HF81。这类芯片可以 自动检测AC是否掉电,所以在正常工作的时候几乎没有损耗。这类芯片放在桥前面都需要有相应的安规认证的,也都是比较可靠的。

也有一些吧这个功能集成到主控芯片里面的,比如FAN6756。有一个HV脚通过两个二极管直接接到AC,同时实现X电容放电和启机的功能。

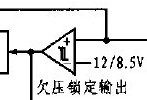

虽然没这么做过,但据说是可行的。个人感觉这个管子要注意两点,一是要足够的耐压;二是要放在信号的上端以防后端芯片过压,(图中红色箭头位置),为了做到这一点就要有个足够高的驱动电压。

接着说整流桥的后面。在母线上会有很多高压器件,所以需要特别注意漏电。300V的母线每10uA就产生3mW的损耗。

半导体器件一般来说都还好,像整流桥、MOSFET,关断时的漏电基本都在1uA以下。高温情况下会大得多,但是空载损耗基本也只看常温条件,没有负载电路本身也没什么热量产生。

电解电容的漏电在有些情况下就不能忽略了,电容越大漏电越强,基本上是和CV成正比关系的。而且电容的质量参差不齐,质量差的电容漏电要大好几倍。可以测试一下如果达到10uA这个数量级了使用的时候就要小心一些了。

对了,如果是比较老的或者低成本的开关电源芯片,还有一组启动电阻挂在高压母线上,用来提供启机的初始电流,正常工作后一般由辅助绕组供电,启动电阻就没有用了,但是功耗还在那里。

现在内置高压启动电流源的芯片都不新鲜了,没必要举例。还用电阻做启动的话那是明显没有把待机功耗做低的诚意了。

今天主攻电源芯片

前面已经提过了,有意做低待机功耗,至少要先一个有内置高压启动电流源的控制芯片。如果真没有的话,也至少要外搭一个。 一些没有高压引脚的芯片也提供一个控制引脚来连接外置的高压开关管。这样就是BOM复杂一点。

芯片本身的功耗是Icc*Vcc/Ƞ。 Icc是工作电流,Vcc是工作电压,Ƞ是转换效率。因为芯片稳定工作的工作电压一般都来自辅助绕组,所以Ƞ取决于开关频率和功率电路的设计,后面也会陆续提到影响转换效率的一些因素。

就目前看到的水平,AC/DC类的功能电源芯片,只要功能不是特别复杂的,Icc都应该能做到百uA这个数量级。只有一些很复杂的芯片,比如PFC+LLC combo这种,或是大功率电源中所采用的数字芯片耗电才会在mA级别。特别大功率的电源有时会采样辅助电源的方式来节约待机功耗。

Vcc则是取决于辅助绕组的设计。为了是芯片功耗最小化,设计的时候当然应采用尽量低的供电电压。只是要注意辅助绕组提供的电源一般会随着负载减轻而降低。必须保证Vcc在空载条件下也能保持在最低工作电压以上。

芯片的控制方式可以说是决定待机功耗最重要的一环。相信大家都清楚,轻载或空载状态下,开关损耗在转换效率中占主导地位。所以为了降低待机功耗,大部分电源芯片都采取载轻降频的控制方式。以中小功率常用的反激电源为例,现在比较流行的一种复合控制模式如下,重载时采用PWM,随着负载减轻频率下降,在接近空载的区域采用Burst的工作模式进一步降低开关频率。

这种控制方式在实际应用中有一个矛盾需要考虑。理论上来说保持最大的ipk可以再空载状态下获得最低的开关频率(1/2 *Lm*ipk^2*fs)。但开关频率在20kHz一下就会有噪音的问题,从这个角度来看就需要ipk越小越好。因此在实际应用的时候就需要找到最佳的折衷设计了。

实际上Burst的方式也有一些细节是值得注意的。每隔100ms连出10个开关和每10ms出一个开关,看起来平均频率是一样的,但转换效率会不会有差别呢?仔细考虑还是会有一写区别的。比如反激电源中,有RCD钳位电路中的能量每次Burst都是充满再放光的,这样的话连出的开关数多一点会比较好。

LLC的情况会不一样,因为LLC的Burst基本前一两个周期把能量已经都输出来了,后面再开关基本上只剩励磁电流了,换句话说后面出的开关都是在做无用功,除了产生开关损耗外没干别的。这样就是连出的开关数少一点会比较好。

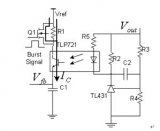

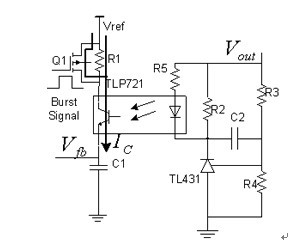

原边反馈和副边反馈的芯片在待机功耗上的表现也是有所区别的。大家都知道原边反馈的好处是省了光耦和TL431,但可以说还有一个附赠的礼品就是降低了空载损耗,因为光耦和TL431也都不是省油的灯。

这里是一个典型的副边反馈的配置,空载状态下典型的偏置电流都在500uA-1mA之间,那么假设副边和辅助绕组的供电都是12V的话,这里就产生了10-20mW的损耗。哦,别忘了还要考虑转换效率

有人减小偏置电流来降低这部分损耗,但是别忘了,满载时的偏置电流空载时还要小很多。这样做可能会影响整个的环路性能甚至失调。

再谈谈一些周边辅助电路设计的影响。

RCD是比较常用的吸收电路,主要是吸收漏感的能量以限制开关管上的尖峰电压。相信大家都清楚,RCD如果做的太强的话会对效率有很明显的影响,那自然也会影响轻载效率和待机功耗。如果考虑到待机状态下电源都是工作在极低频率的Burst状态下的话,实际上C的大小对待机功耗的影响比R要大得多,因为每次C都会充满再放光的。这部分能量就像一个假负载挂在那里 一样

从这个角度出发,有一种做法是把C彻底拿掉,用一个TVS来代替,这样就拿掉了这个“假负载”。

在多路输出的应用里面还有一些小手段可以减小待机功耗的,之前提到过作反馈用的光耦和431的损耗,这里再补充一点。在多路绕组输出的应用里面,光耦和431的偏置电流应该取自电压最低的那一路,(当然是在不影响反馈性能的前提下),这样可以非常明显的节约待机功耗。

有一种在家电、智能家居应用中非常常见的两路输出的结构,是基于LDO的。一般比较高的电压是18V、12V等供风扇、继电器或者背光的,再通过一个LDO提供稳定的5V或3.3V给MCU。因为风扇、继电器这些基本上在待机状态下都是不用的,那么就可以用MCU提供一个待机信号,把18V、12V降到5-6V只要能保持MCU正常工作就行了。这个是从系统的角度出发来实现节约的。

-

电源

+关注

关注

184文章

17693浏览量

249913 -

开关电源

+关注

关注

6456文章

8325浏览量

481619 -

功耗

+关注

关注

1文章

810浏览量

31935

原文标题:深入分析开关电源的待机功耗

文章出处:【微信号:Power-union,微信公众号:电源联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何降低LED照明开关电源待机功耗

怎么提高开关电源的待机效率

【技巧分享】降低开关电源的待机功耗

怎样对开关电源进行环路分析?

低待机功耗开关电源充电器的设计

详解如何实现开关电源待机低功耗

开关电源功耗分析和提高待机效率的方法

对开关电源的待机功耗的分析

对开关电源的待机功耗的分析

评论