如果需要重读,需要用ram,如果不需要重读的话就用FIFO

双buffer不太好实现错误重传机制!!!!

双buffer作用:

1、跨时钟域

2、完成数据位宽转换

3、完成数据缓冲

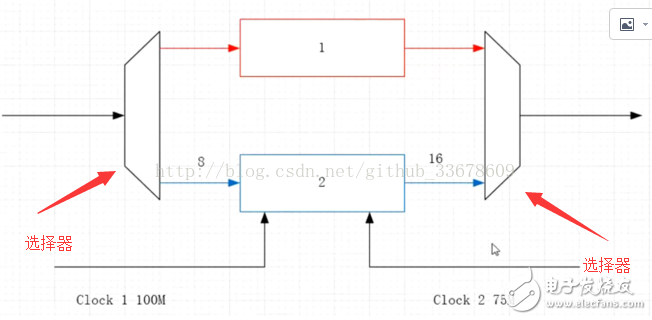

双buffer缓冲操作示意图,在操作工程中存在两个clock1 和clock2,但是输入输出的传输带宽不能相差太大,会出现数据覆盖的现象

1、如上图所示,输入端读数据比写数据速度要块,这样的话,在数据写完后让外部来读,这样在写的过程中,空闲的时间,读端,可以进行数据操作等操作(100MHz * 8bit 《 75MHz * 16bit)

2、写完一次数据就用选择器选择另外一个ram写,在下降沿时切换,读选择器类似。

3、快时钟域向慢时钟域传输信号时,需要将写入的片选信号data|_v延迟两拍

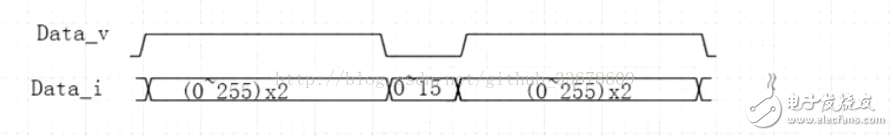

testbeach中产生的数据思路

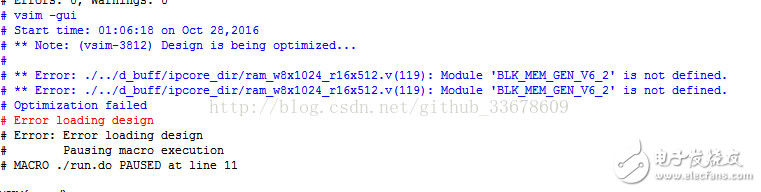

ISE产生的ipcore,不使用ISE自带的simulation仿真,直接用modulesim仿真时出现加入的ipcore找不到相关文件,如图所示

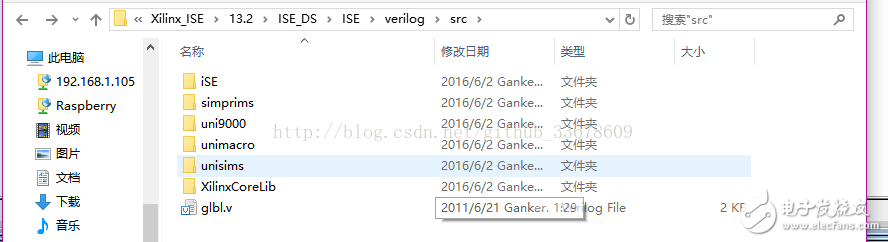

直接到该目录下搜索,然后copy出来到你的工程文件中

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1663文章

22493浏览量

638940 -

RAM

+关注

关注

8文章

1400浏览量

120967

发布评论请先 登录

相关推荐

热点推荐

如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作

Simple Dual Prot RAM,也就是伪双口RAM。一般来讲"Simple Dual Port RAM"是最常用的,因为它是两个

发表于 01-07 16:05

基于FPGA的双口RAM实现及应用

为了在高速采集时不丢失数据,在数据采集系统和CPU之间设置一个数据暂存区。介绍双口RAM的存储原理及其在数字系统中的应用。采用FPGA技术构造

发表于 02-11 11:20

•69次下载

如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该

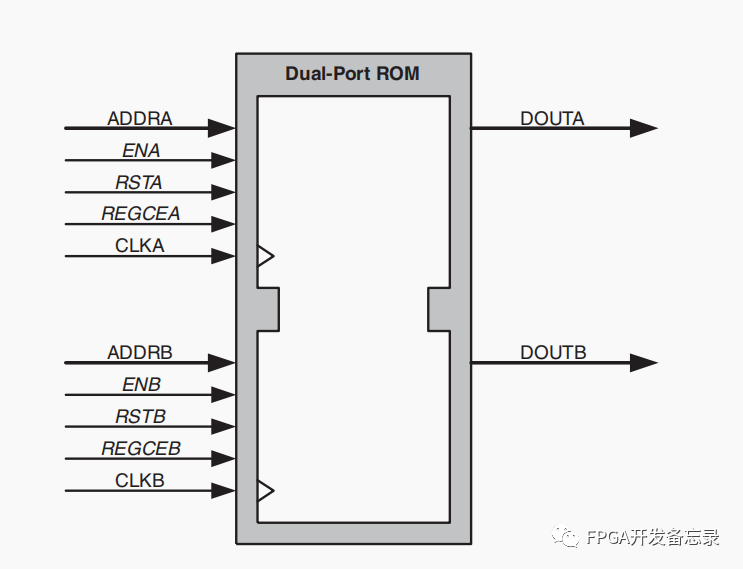

一文了解FPGA双端口RAM操作

一文了解FPGA双端口RAM操作

评论