S逐次逼近型(SAR) ADC提供高分辨率、出色的精度和低功耗特性。一旦选定一款精密SAR ADC,就必须确定获得最佳结果所需的支持电路。需要考虑的三个主要方面是:

基准电压源

数字接口

今天,小编分享的内容将重点介绍前端设计的电路要求和权衡因素。前端包括两个部分:驱动放大器和RC滤波器——

放大器调节输入信号,同时充当信号源与ADC输入端之间的低阻抗缓冲器;

RC滤波器限制到达ADC输入端的带外噪声,帮助衰减ADC输入端中开关电容的反冲影响。

为SAR ADC选择合适的放大器和RC滤波器可能很困难,特别是当应用不同于ADC数据手册的常规用途时。根据各种影响放大器和RC选择的应用因素,ADI提供了设计指南,可实现最佳解决方案。主要考虑因素包括:

输入频率

吞吐速率

输入复用

选择合适的RC

滤波器

要选择合适的RC滤波器,必须计算单通道或多路复用应用的RC带宽,然后选择R和C的值。

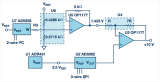

图1显示了一个典型的放大器、单极点RC滤波器和ADC。ADC输入构成驱动电路的开关电容负载。其10 MHz输入带宽意味着需要在宽带宽内保证低噪声以获得良好的信噪比(SNR)。RC网络限制输入信号的带宽,并降低放大器和上游电路馈入ADC的噪声量。不过,带宽限制过多会延长建立时间并使输入信号失真。

图1. 典型放大器、RC滤波器和ADC

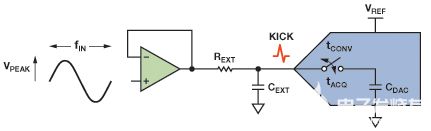

在建立ADC输入和通过优化带宽限制噪声时所需的最小RC值,可以由假设通过指数方式建立阶跃输入来计算。要计算阶跃大小,需要知道输入信号频率、幅度和ADC转换时间。转换时间,tCONV(图2)是指容性DAC从输入端断开并执行位判断以产生数字代码所需的时间。转换时间结束时,保存前一样本电荷的容性DAC切换回输入端。此阶跃变化代表输入信号在这段时间的变化量。此阶跃建立所需的时间称为"反向建立时间"。

图2. N位ADC的典型时序图

在给定输入频率下,一个正弦波信号的最大不失真变化率可通过下式计算:

如果ADC的转换速率大大超出最大输入频率,则转换期间输入电压的最大变化量为:

这是容性DAC切换回采集模式时出现的最大电压阶跃。然后,DAC电容与外部电容的并联组合会衰减此阶跃。因此,外部电容必须相对较大,达到几nF。此分析假设输入开关导通电阻的影响可忽略不计。现在需要建立的阶跃大小为:

接下来计算在ADC采集阶段,ADC输入建立至½ LSB的时间常数。假设阶跃输入以指数方式建立,则所需RC时间常数τ为:

其中,tACQ为采集时间,NTC为建立所需的时间常数数目。所需的时间常数数目可以通过计算阶跃大小VSTEP与建立误差(本例为½ LSB)之比的自然对数来获得:

因此,

将上式代入前面的公式可得:

等效RC带宽

举个栗子

借助RC带宽计算公式,选择16位ADCAD7980(如图3所示),其转换时间为710 ns,吞吐速率为1 MSPS,采用5 V基准电压。最大目标输入频率为100 kHz。计算此频率时的最大阶跃:

然后,外部电容的电荷会衰减此阶跃。使用27 pF的DAC电容并假设外部电容为2.7 nF,则衰减系数约为101。将这些值代入VSTEP计算公式:

接下来计算建立至½ LSB(16位、5 V基准电压)的时间常数数目:

采集时间为:

计算τ:

因此,带宽为3.11 MHz, REXT为 18.9 Ω.

图3. 采用16位1 MSPS ADC AD7980的RC滤波器

最小带宽、吞吐速率和输入频率之间的这种关系说明:输入频率越高,则要求RC带宽越高。同样,吞吐速率越高,则采集时间越短,从而提高RC带宽。采集时间对所需带宽的影响最大;如果采集时间加倍(降低吞吐速率),所需带宽将减半。此简化分析未包括二阶电荷反冲效应,它在低频时变成主要影响因素。输入频率非常低时(<10 kHz,包括DC),容性DAC上建立的始终是大约100 mV的电压阶跃。此数值应作为上述分析的最小电压阶跃。

多路复用输入信号很少是连续的,通常由不同通道切换产生的大阶跃组成。最差情况下,一个通道处于负满量程,而下一个通道则处于正满量程(见图4)。这种情况下,当多路复用器切换通道时,阶跃大小将是ADC的满量程,对于上例而言是5 V。

图4. 多路复用设置

在上例中使用多路复用输入时,线性响应所需的滤波器带宽将提高到3.93 MHz(此时阶跃大小为5 V,而非单通道时的1.115 V)。假设条件如下:多路复用器在转换开始后不久即切换(图5),放大器和RC正向建立时间足以使输入电容在采集开始前稳定下来。

图5. 多路复用时序

对于计算得到的RC带宽,可以利用表1进行检查。从表中可知,要使满量程阶跃建立至16位,需要11个时间常数(如表1)。对于计算的RC,滤波器的正向建立时间为11 × 40.49 ns = 445 ns,远少于转换时间710 ns。正向建立不需要全部发生在转换期间(容性DAC切换到输入端之前),但正向和反向建立时间之和不应超过所需的吞吐速率。对于低频输入,信号的变化率低得多,因此正向建立并不十分重要。

表1. 建立至N位分辨率所需的时间常数数目

计算出滤波器近似带宽后,就可以分别选择REXT和 CEXT的值。

上述计算假设 CEXT= 2.7 nF,这是数据手册所示应用电路的典型值。如果选择较大的电容,则当容性DAC切换回输入端时,对反冲的衰减幅度会更大。然而,电容越大,驱动放大器就越有可能变得不稳定,特别是给定带宽下REXT值较小时。

如果 REXT值太小,放大器相位裕量会降低,可能导致放大器输出发生响铃振荡或变得不稳定。对于串联 REXT较小的负载,应采用低输出阻抗的放大器来驱动。可以利用RC组合和放大器的波特图执行稳定性分析,以便验证相位裕量是否充足。最好选择1 nF至3 nF的电容值和合理的电阻值,以使驱动放大器保持稳定。此外务必使用低电压系数的电容,如NP0型,以保持低失真。

REXT的值必须能使失真水平保持在要求的范围以内。图6显示了驱动电路电阻对失真的影响与AD7690输入频率的函数关系。失真随着输入频率和源电阻的提高而提高。导致这种失真的原因主要是容性DAC提供的阻抗的非线性特性。

图6. 源电阻对THD的影响与输入频率的关系

低输入频率(<10 kHz)可以支持较大的串联电阻值。失真还与输入信号幅度有关;对于同一失真水平,较低的幅度可以支持较高的电阻值。计算上例中的 REXT in the example above, where τ = 51.16 ns 假设CEXT 为2.7 nF,得到电阻值为18.9 Ω。这些值接近ADI数据手册应用部分给出的常见值。

此处计算的标称RC值是有用的指南,但不是最终解决方案。选择REXT与 CEXT之间的适当平衡点,需要了解输入频率范围、放大器可以驱动多大的电容以及可接受的失真水平。为了优化RC值,必须利用实际的硬件进行试验,从而实现最佳性能。

选择合适的

放大器

在上一部分中,根据输入信号和ADC吞吐速率,计算了适合ADC输入的RC带宽。接下来必须利用此信息选择合适的ADC驱动放大器。需要考虑如下方面:

放大器大小信号带宽

建立时间

放大器噪声特性以及对系统噪声的影响

失真

失真对于电源轨的裕量要求

该数据手册通常会给出放大器的小信号带宽。但是,根据输入信号的类型,大信号带宽可能更重要,尤其是高输入频率(>100 kHz)或多路复用应用(因为电压摆幅较大),而且输入信号的正向建立更加关键。例如,ADA4841-1的小信号带宽为80 MHz(20 mV p-p信号),但大信号带宽仅3 MHz(2 V p-p信号)。上例采用AD7980,计算的RC带宽为3.11 MHz。对于较低的输入频率,ADA4841-1是很好的选择,因为其80 MHz小信号带宽对于反向建立而言绰绰有余,但在多路复用应用中则有困难,因为对于大信号摆幅,此时的RC带宽要求提高到3.93 MHz。这种情况下,更合适的放大器是ADA4897-1,它具有30 MHz的大信号带宽。一般而言,放大器的小/大信号带宽至少应比RC带宽大两三倍,具体取决于是以反向建立还是正向建立为主。如果要求放大器级提供电压增益(这会降低可用带宽),更适用这条原则,甚至可能需要带宽更宽的放大器。

看待正向建立要求的另一种方式是查看放大器的建立时间特性,它通常是指建立到额定阶跃大小某一百分比所需的时间。对于16位到18位性能,通常要求建立到0.001%,但大多数放大器仅指定不同阶跃大小的0.1%或0.01%建立时间。因此,为了确定建立特性是否支持ADC吞吐速率,需要对这些数值进行折中。ADA4841-1针对8 V阶跃给出的0.01%建立时间为1 μs。在驱动1 MSPS(1 μs周期)AD7980的多路复用应用中,它将无法使满量程阶跃的输入及时建立,但如果降低吞吐速率,例如500 kSPS可能是可行的。

RC带宽对于确定放大器的最大容许噪声量十分重要。放大器噪声一般通过低频1/f噪声(0.1 Hz至10 Hz)和高频时的宽带噪声谱密度(图7所示噪声曲线的平坦部分)来规定。

图7. ADA4084-2电压噪声与频率的关系

折合到ADC输入端的总噪声可以按照如下方法计算。首先,计算放大器宽带频谱密度在RC带宽上的噪声。

其中,en= 噪声频谱密度(V/√ Hz), N = 放大器电路噪声增益,BWRC= RC 带宽 Hz。

然后,通常通过下式计算低频1/f噪声;它通常指定为峰峰值,需要转换为均方根值。

其中,

= 1/f峰峰值噪声电压,N = 放大器电路噪声增益。

总噪声为以上两个噪声的和方根:

为将驱动器噪声对总SNR的影响降至最低,此总噪声应为ADC噪声的1⁄10左右。根据目标系统的SNR要求,可能还允许更高的噪声。例如,如果ADC的SNR为91 dB,VREF= 5 V,则总噪声应小于或等于

由此值很容易算出1/f噪声和宽带噪声谱密度的最大允许值。假设拟用的放大器具有可忽略不计的1/f噪声,以单位增益工作,并采用RC带宽为上例计算值(3.11 MHz)的滤波器,那么

因此,该放大器的宽带噪声谱密度必须小于或等于2.26 nV/√ Hz。ADA4841-1的宽带噪声谱密度为2.1 nV/√ Hz,符合这一要求。

放大器需要考虑的另一个重要特性是特定输入频率时的失真。通常,为获得最佳性能,16位ADC需要大约100 dB的总谐波失真(THD),18位ADC需要大约110 dB。图8显示对于2 V p-p输入信号,ADA4841-1的典型失真与频率的关系图。

图8. ADA4841-1的失真与频率的关系

图中显示的不是总谐波失真,而是一般最为重要的二次和三次谐波成分。

ADA4841-1的噪声非常小,失真特性优异,足以驱动18位ADC到大约30 kHz。当输入频率接近100 kHz或更高时,失真性能开始下降。为在高频时实现低失真,需要使用功耗更高、带宽更宽的放大器。较大的信号也会降低性能。对于0 V至5 V的ADC输入,失真性能信号范围将提高到5 V p-p。从图8所示的失真图可看出,这将产生不同的性能,因此放大器可能需要测试,以确保它满足要求。图9比较了多个输出电压水平的失真性能。

图9. 不同输出电压水平下失真与频率的关系

裕量,即放大器最大实际输入/输出摆幅与正负电轨之差,也可能影响THD。放大器可能具有轨到轨输入和/或输出,或者要求最高1 V甚至更大的裕量。即便是轨到轨输入/输出,如果工作信号电平接近放大器的供电轨,也将难以获得良好的失真性能。因此,最好应选择让最大输入/输出信号远离供电轨的电源电平。考虑一个0 V至5 V输入范围的ADC,采用ADA4841-1放大器驱动,需要将ADC的范围提高到最大。该放大器具有轨到轨输出,对输入有1 V的裕量要求。如果用作单位增益放大器,则至少需要1 V的输入裕量,正电源至少必须是6 V。输出为轨到轨,但仍然只能驱动到地或正供电轨的大约25 mV范围内,因而需要一个负供电轨,以便一直驱动到地。为了给失真性能留有一定的裕量,负供电轨可以是–1 V。

如果允许降低ADC输入范围,从而丧失一定的SNR,则可以消除负电源。例如,如果ADC的输入范围降为0.5 V至5 V,此10%损失将导致SNR降低大约1 dB。然而,这样就可以将负供电轨接地,从而消除用以产生负电源的电路,降低功耗和成本。

因此,选择放大器时,务必考虑输入和输出信号范围要求,以便确定所需的电源电压。本例中,额定工作电压为5 V的放大器不能满足要求;但ADA4841-1的额定电压高达12 V,所以使用较高的电源电压将能实现出色的性能,并提供充足的电源裕量。

-

滤波器

+关注

关注

161文章

7773浏览量

177904 -

adc

+关注

关注

98文章

6480浏览量

544311 -

驱动放大器

+关注

关注

0文章

45浏览量

16985

原文标题:前端放大器和RC滤波器

文章出处:【微信号:WW_CGQJS,微信公众号:传感器技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电池与充电管理:选择与权衡因素

电池与充电管理 选择与权衡因素

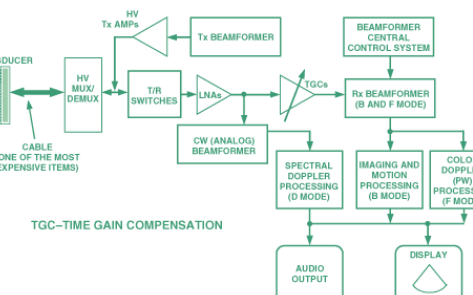

高速ADC前端设计挑战和权衡因素

选择数模转换器(DAC)时的各种权衡因素

放大器的设计要求和基本电路资料下载

用于精密SAR模数转换器的前端放大器和RC滤波器设计

前端设计的电路要求和权衡因素详解

前端设计的电路要求和权衡因素详解

![RA2快速设计指南 [4] 复位<b class='flag-5'>要求和</b>复位<b class='flag-5'>电路</b>](https://file1.elecfans.com/web2/M00/A3/21/wKgZomUDyc2AAMHWAAF8yDw8WIc920.jpg)

评论