DSP的应用

针对8核DSP TMS320C6678与外部设备进行数据通信的需求,以片上集成千兆以太网交换子系统为核心,选取芯片88E1111作为PHY设备,设计了千兆以太网通信接口的硬件电路。在嵌入式操作系统SYS/BIOS和网络开发环境NDK上,完成了以太网底层驱动和TCP/IP协议的程序设计。通过DSP与上位机进行以太网通信测试,证明了以太网接口电路硬件及软件的正确性和实用性。

随着DSP处理器在现代工业的应用越来越广泛,DSP的功能不仅只有快速运算处理,还需要与其他处理器或者设备之间进行实时数据交换,以实现资源的共享。因此,针对不同设备的需求,选择稳定、快速和高效率的接口方式在当今数字信号处理系统设计中关键的组成部分。

TI公司的8核处理器TMS320C6678(以下简称C6678)提供丰富的片上接口资源用于处理器与外设之间的通信,这些接口都可以用于DSP与外设之间的通信,但是灵活性有差异,使用SGMII接口来实现千兆以太网通信,可使得通信接口一般化,能够适用于众多的设备连接。

本文针对C6678的芯片特点以及含有的接口资源,设计实现了千兆以太网通信,主要设计了以太网接口电路、网络底层硬件驱动、TCP/IP协议的用户程序,并完成了与上位机以太网通信测试,实现了数字信号高速有效地网络传输。

1 C6678以太网交换子系统

C6678是基于KeyStone I构架的8核高性能、定点/浮点处理器,单核最高工作频率可达1.25 GHz。C6678的以太网交换子系统包括2个以太网媒体访问控制(Ethernet Media Access Controller,EMAC)、2个SGMII、1个管理数据输入输出(Management Data Input Output,MDIO)、3-Port以太网交换模块以及网络配置总线,其网络交换子系统如图1所示。

EMAC的作用是将交换子系统的内部信号转换为GMII信号传递给SGMII模块;MDIO控制物理层芯片执行对多数据流的控制输入输出。

2 PHY芯片88E1111

本文选择C6678作为主芯片,由于C6678的千兆网络交换子系统只支持SGMII接口,所以本文选择对SGMII接口的网络数据传输具有较好兼容性的物理芯片88E1111。88E1111芯片的内部结构如图2所示。

88E1111的介质接口有铜介质接口和光纤接口。铜介质接口为MDI[3:0],通过设置HWCFG_MODE[3:0]来选择运行模式。 88E1111集成的MDIO模块与EMAC的MDIO接口相连接,可将方便网络控制端读取物理芯片状态寄存器,达到实时监测的效果。

3 硬件接口设计

本文设计的任务是基于C6678片内以太网交换子系统和片外PHY芯片88E1111及其外围电路的接口设计。主要包括:C6678与88E1111芯片连接、88E1111芯片配置以及88E1111芯片与网络介质连接。

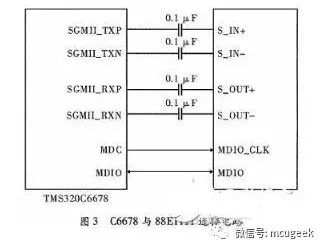

3.1 C6678与88E1111芯片连接

C6678和PHY芯片88E1111的接口电路如图3所示。88E1111工作在SGMII接口模式下,不需要TXCLK时钟输入,更有助于减少电路板上走线的数量,同时也可减少噪声的产生。

主要的接口信号包括时钟和数据信号如下:

MDIO_CLK:管理数据时钟。该时钟信号由C6678片上的MDIO模块提供,该时钟频率通过配置MDIO的控制寄存器CONTROL中的CLKDIV位来控制实现。

SGMII_TXP和SGMII_TXN:串行发送差分数据线。连接DSP内部SerDes和物理芯片的S_IN管脚,DSP的SerDes通过该管脚向物理层发送串行数据,数据中包含发送数据时钟信号。

SGMII_RXP和SGMII_RXN:串行接收差分数据线。连接DSP内部SerDes和物理芯片的S_OUT管脚,物理层芯片通过该接口将数据传送到DSP的SerDes,数据中包含数据接收时钟信号。

MDIO:管理数据I/O。可最多连接32个PHY设备到DSP的EMAC,并且可以枚举所有PHY设备,读取PHY设备状态寄存器来监测PHY的连接状态。数据帧结构符合802.3标准,包含读写指令、PHY地址、寄存器地址和数据等。

因为88E1111上集成的MDIO与C6678集成MDIO模块进行连接时,电压有所差别,前者电压为2.5 V,后者电压为1.8 V,所以在二者之间应该添加电压转换器。本文采用一片PCA9306,实现2.5 V和1.8 V之间的电平转换,其连接电路如图4所示。

3.2 88E1111芯片配置

88E1111与C6678的MDIO模块相连接,MDIO最多可识别32个物理芯片,在使用物理芯片之前需要对其进行配置,配置内容主要包括芯片的地址、模式等。配置CONFTG[6:0]管脚定义可查询文献,本文配置的硬件电路如图5所示,图5中可以不使用电阻,本文为了测试方便,加一个0 Ω的电阻。

88E1111硬件配置完成后,系统将固定为一种接口方式,按照文献的定义,物理芯片的地址为:PHY_ADDRESS=0’b00001,芯片模式为:不带时钟,自动协商的SGMII模式。

3.3 88E1111芯片与RJ45连接

88E1111和网络介质之间无法直接连接,因传输速度在千兆级,所以更加需要设计合适的网络隔离变压器来降低传输损耗、回音和串扰。本文选择千兆网口插座HR911130C,该插座内部自带变压器电路,只需在外部连接滤波网络便可实现网络信号稳定地传输。88E1111和 HR9111130C采用差分连接,在PCB布线时需要严格等长,且一般还需使用阻抗匹配网络,如图6中的R1和C1。

4 软件程序设计

TI针对网络开发发布了网络开发套件(Network Development Kit,NDK),能将多个模块的配置操作交给NDK网络框架实现,同时数据分包和解析也无需程序员过多考虑,加速了网络开发进程。NDK构建在实时操作系统SYS/BIOS之上,NDK通过OS抽象层与BIOS进行交互,同时BIOS的cfg配置文件能对NDK各模块进行可视化查看。

-

dsp

+关注

关注

554文章

8060浏览量

350875 -

以太网

+关注

关注

40文章

5469浏览量

172907 -

C6678

+关注

关注

3文章

3浏览量

13948

原文标题:基于多核DSP的以太网通信接口设计

文章出处:【微信号:mcugeek,微信公众号:MCU开发加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于C6678片内以太网交换子系统接口资源详解

C6678芯片是否有带Secure Boot的版本

C6678 .stack的问题

C6678与TVP5158互联

关于C6678的问题

C6678的应用问题

C6678设计遇到一些问题,求解答

请问如何获取C6678的MAC地址?

请教关于C6678的PCIe的问题

关于C6678仿真器

项目前期求助(C6678)

请问C6678芯片的功耗差异有多少?

6U CPCI板卡设计方案:8-基于双TMS320C6678 + XC7K420T的6U CPCI Express高速数据处理平台

C6678的芯片特点及其含有的接口资源详解

C6678的芯片特点及其含有的接口资源详解

评论