1 亚微米 BiCMOS[B] 技术的主要特点

BiCMOS[B]的 Twin-Well[1]与P-Well[2]或 N-Well[3] 的制造技术有很大的不同。主要是 CMOS 特征尺寸为亚微米级,使制造技术发生了重要的变化。

由于器件尺寸缩小,栅氧化膜的厚度也要求按比例减薄,这主要是为了防止短沟效应。薄栅氧化膜要达到其高质量的指标:低的缺陷密度,好的抗杂质扩散的势垒特性,具有低的界面态密度和固定电荷的Si/SiO2 界面,在热载流子应力和辐射条件下的稳定性以及低的热预算(温度时间乘积量)工艺。

在亚微米制造技术中,P 沟道区的注入一般需要作两次注入,其中一次用于调整阈值电压,另一次用于抑制穿通效应。抑制穿通的注入通常是高能量,较高剂量,注入峰值较深(延伸至源-漏耗尽区附近);而调节阈值电压注入一般能量较低,注入峰值位于表面附近。因此栅下的杂质分布不仅决定于衬底掺杂,而且还决定于注入杂质,因而沟道区杂质呈非均匀分布。

在亚微米技术中,为了抑制 CMOS 穿通电流和减小短沟道效应,工艺要求更浅的源漏结深,达到浅结。工艺对 PN 结有很高的要求:高的表面浓度,浅的结深,低接触薄层电阻以及很小的结漏电流。

在浅 的 N+P 结中,可用 75As+ 注入来实现。由于砷离子相当重,因而可使被注入区硅表面变为无定形,此时,只要在 900 ℃ 较低温度下退火,即可由固相外延形成再结晶,相应扩散却相当小,因此可实现 N+P 浅结。还需要 P+N 浅结。采用 49BF2+ 注入, 由于 49BF2+ 质量大,并能将结深降到单用 11B+ 时的四分之一,来制作 P+N 浅结。

在浅结欧姆接触中,Al-Si 互扩散产生的结漏电,穿通等是影响器件热稳定性,甚至造成器件失效的一个严重问题,为此采用在 Al 层和 Si 之间加一扩散阻挡层的方法,通常选用 TiN 膜,这是因为 TiN 热稳定性好。

轻掺杂漏 LDD 结构主要应用于亚微米或深亚微米 MOS 器件中,以提高源漏穿通电压和减少高电场引入的热载流子注入问题。具有代表性的结构和技术有利用 TEOS 侧墙制作对称 LDD 结构,它的形成方法就是在栅和源漏的重掺杂区之间引入一个轻掺杂区。这样,N+ 或 P+ 区注入杂质不会在栅下面发生横向扩散,但会在侧墙下面扩散。

本文提出, 为了直观显示出双极型与 CMOS 器件兼容集成的亚微米 BiCMOS[B] 结构,应用芯片结构技术[4-6],可以得到芯片剖面结构,并利用计算机和它所提供的软件,描绘出制程中芯片表面﹑内部器件以及互连的形成过程和结构的变化的示意图。

2 亚微米芯片剖面结构

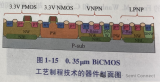

应用芯片结构技术[4-6],使用计算机和它所提供的软件,可以得到亚微米 BiCMOS[B] 芯片典型剖面结构。首先由设计人员在电路中找出各种典型元器件: NMOS, PMOS, NPN (纵向)以及 PNP(横向)。然后由制造人员对这些元器件进行剖面结构设计,选取剖面结构各层统一适当的尺寸和不同的标识,表示制程中各工艺完成后的层次,设计得到可以互相拼接得很好的各元器件结构(或在元器件结构库中选取),分别如图 1[A]﹑[B]﹑[C] 以及 [D] 等所示(不要把它们看作连接在一起)。最后把各元器件结构依一定方式排列并拼接起来,构成电路芯片剖面结构,图 1 为其示意图。

图 1 芯片剖面结构是以双极型制程及其所制得的元器件为基础,引入兼容的 CMOS 器件工艺,最终在同一硅衬底上形成 IC 中主要器件。而图 1-B的芯片剖面结构中,除了图 1-A 的四种器件外,还有其它无源器件:如位于场区上的双层 Poly 电容和 Poly 电阻等;或衬底 MOS 电容(或双极型电容)和 N-Well 电阻(或基区电阻);或采用掺杂 N+Poly 与硅表面直接相接形成浅发射区的结构来代替图中 NPN 结构,来提高电路速度;或它们之间的不同结合,就形成多种不同的复杂的 BiCMOS[B] 结构,可选用其中一种与设计电路直接相联系的结构。限有篇幅,本文仅介绍图 1-A 技术。

3 亚微米芯片工艺技术

设计电路 CMOS 采用 0.8μm/双极型为2~ 3μm 设计规则,使用1~2μm 薄外延的亚微米BiCMOS[B] 制造技术。该电路主要元器件﹑制造技术以及主要参数如表1所示。它以双极型制程及其所制得的元器件为基础,引入兼容的 CMOS 器件工艺,并对其中芯片结构和制造工艺进行改变,以制得 CMOS 器件的相容技术,最终在同一硅衬底上形成如表 1 所示的 IC 中主要元器件,并使之互连,实现所设计的电路。该电路或各层版图己变换为缩小的各层平面和剖面结构图形的 IC 芯片。如果所得到的工艺与电学参数都适合于所设计电路的要求, 则芯片功能和电气性能都能达到设计指标。

为实现亚微米 BiCMOS[B] 技术,对双极型制造工艺作如下的改变。

(1)在自对准形成 BLN+ 埋层﹑BLP+ 埋层和 P型薄层外延后,分别引入 11B+﹑31P+ 注入并推进,生成与埋层相接的 Twin-Well,同时形成双极型隔离;引入场区注入,硅局部氧化,形成 CMOS 隔离;

(2)在基区推进后,引入沟道防穿通注入和阈值调节注入,栅氧化以及 Poly 淀积并掺杂,LDD 注入,TEOS 淀积,刻蚀形成亚微米 CMOS 硅栅结构及其侧墙;

(3)75As+ 或 49BF2+ 注入,生成 N+ 或 P+ 区为双极型的 E/C 掺杂区和 Pb 基区接触同时,引入形成源漏掺杂区。上述引入这些基本工艺,使双极型芯片结构和制程都发生了明显的变化。工艺完成后,以制得 NMOS[A] 与 PMOS[B] 和纵向 NPN[C] 与横向PNP,并用亚微米 BiCMOS[B] 来表示。

表 1 中的参数: P- 型外延层厚度为 TP-EPI,深磷区(DN)结深/薄层电阻为 XjDN / RSDNN+ 结深/ 薄层电阻为 XjN+ / RSN+,P+ 结深/薄层电阻为 XjP+ / RSP+,基区结深/薄层电阻为 XjPb / RSPb,埋层结深/薄层电阻为 XjBL / RSBL,其它参数符号与通常表示相同。

根据电路电气特性指标,确定用于芯片制造的基本参数,如表 1 所示。为此,芯片制程工艺中,一方面要确保工艺参数,电学参数都达到规范值,另一方面批量生产中要确保电路具有高成品率,高性能以及高可靠性。根据电路电气特性的指标,提出对各种参数:(1)工艺参数如各种掺杂浓度及其分布﹑结深﹑栅氧化层厚度﹑基区宽度等;(2)电学参数如各种薄层电阻﹑源漏击穿电压﹑阈值电压﹑CB/CE 击穿电压﹑放大系数β等以及(3)硅衬底电阻率/外延层厚度及其电阻率等要求,从而制定出各工序具体工艺条件,以保证所要求的各种参数都达到规范值。

4 亚微米芯片工艺制程

图 1 所示的芯片结构采用确定的制造技术来实现。它是由工艺规范确定的各个基本工序﹑相互关联以及将其按一定顺序组合构成。为实现此制程,上面(1)~(3)引入这些基本工艺,不仅增加了制造工艺,技术难度增大,使芯片结构发生了明显的变化,而且改变了双极型制程,从而实现了亚微米BiCMOS[B] 制程。

为实现此制程,需要作多次氧化﹑光刻﹑杂质扩散﹑离子注入﹑薄膜淀积以及溅射金属等构成基本工序。这些工序提供了形成电路中各个元器件 NMOS,PMOS,NPN(纵向),PNP(横向)等所需要的精确控制的硅中的杂质层(BLN+,BLP+,P-EPI,DN,N-Well,P-Well,PF,NF,Pb,N+SN-,P+SP-, N+Poly等),也提供了这些电路元器件连接起来形成集成电路所需要的介质层(F-Ox,G-Ox, Poly-Ox,BPSG / LTO,TEOS等)和金属层(AlCu)。这些都必须按给定的顺序进行的制造步骤构成了制程。

应用计算机,依据芯片制造工艺中的各个工序的先后次序,把各个工序互相连接起来,可以得到芯片制程,。该制程由各工序所组成,而工序则由各工步所组成来实现。根据设计电路的电气特性要求,选择工艺规范号和工艺序号,以便得到所需要的工艺和电学参数。

应用芯片结构技术[4],可以得到图 1 芯片剖面结构,使用计算机和它所提供的软件,描绘出芯片制程中各个工序剖面结构,根据各个工序的先后次序互相连接起来,得到如图2所示的亚微米 BiCMOS[B] 制程剖面结构示意图。该图直观地显示出制程中芯片表面﹑内部元器件以及互连的形成过程和结构的变化。

(1)衬底材料 P-Si <100>,基底氧化(Pad-Ox), Si3N4 淀积(1),光刻 BLN+ 埋层, 刻蚀 Si3N4 ,腐蚀 SiO2,BLN+ 区氧化(BLN+-Ox), 121Sb+ 注入,如图 2-1 所示。

(2)注入退火,BLN+ 区推进/氧化(BLN+ -Ox),二层(SiON/Si3N4)腐蚀,BLP+ 埋层 11B+ 注入,如图 2-2 所示。

(3)注入退火,BLP+ 埋层推进, 腐蚀净 SiO2 , P- 型薄层外延(P-EPI),基底氧化(Pad-Ox),Si3N4(2)淀积,光刻 N-Well, 刻蚀 Si3N4,31P+ 注入,如图 2-3 所示。

(4)注入退火,N-Well 推进/氧化(N-Well-Ox),二层(SiON/Si3N4)腐蚀,P-Well 11B+ 注入,如图 2-4 所示。

(5)注入退火,P/N-Well 推进/氧化,光刻DN区,腐蚀 SiO2 , DN 区氧化(DN-Ox),31P+ 注入,DN 区推进/氧化,如图2-5 所示。

(6)腐蚀净 SiO2, 出现 P-Well 平面高于 N-Well,基底氧化(Pad-Ox),Poly /Si3N4(3)淀积,光刻源区,刻蚀 Si3N4 /Poly,如图 2-6 所示。

(7)光刻 P 场区,APT.(防穿通)11B+ 深注入,11B+ 浅注入,如图 2-7 所示。

(8)光刻 N 场区,75As+ 注入,如图 2-8 所示。

(9)注入退火,场区氧化(F-Ox),形成四层(SiON / Si3N4 / Poly / SiO2)结构,如图 2-9 所示。

(10)四层(SiON / Si3N4 / Poly / SiO2)腐蚀,预栅氧化(Pre-Gox), 光刻 Pb 基区,11B+ 注入,如图 2-10 所示。

(11)注入退火,Pb 基区推进,光刻 N 沟道区,49BF2+ 注入,如图 2-11 所示。

(12)光刻 P 沟道区,APT.31P+ 深注入,49BF2+ 浅注入,如图 2-12 所示。

(13)腐蚀预栅氧化层,注入退火,栅氧化(G-Ox),Poly 淀积并掺杂,光刻 Poly,刻蚀 Poly,此时 N-Well 与 Poly 之间出现防穿通区,如图 2-13 所示。

(14)Poly 氧化(Poly-Ox),光刻 NLDD 区,31P+ 注入(Poly 注入未标出),如图 2-14 所示。

(15)光刻 PLDD 区,49BF2+ 注入(Poly 注入未标出),如图 2-15 所示。

(16)注入退火,形成 SN-,SP- 区,TEOS 淀积/致密,刻蚀形成 TEOS 侧墙,源漏氧化(S /D-Ox),如图 2-16 所示。

(17)光刻 N+ 区,75As+ 注入(Poly 注入未标出),如图 2-17 所示。

(18)光刻 P+ 区,49BF2+ 注入(Poly 注入未标出),如图 2-18 所示。

(19)注入退火,形成 N+SN-,P+SP- 区(图中未标出 SN-,SP-),LTO/BPSG 淀积/致密,光刻接触孔,刻蚀 BPSG / LTO / SiO2,如图 2-19 所示。

(20)溅射 Ti/TiN, RTA N2 退火,溅射金属(Metal),光刻金属, 刻蚀 TiN / AlCu / TiN / Ti , 如图 2-20 所示。

从亚微米 BiCMOS[B] 制程和剖面结构可以看出,阱区是由向 P 型衬底生长出 P- 型外延层中扩散 N﹑ P 型杂质而制成。阱界面场区氧化表面具有台阶结构。PMOS﹑纵向 NPN﹑横向 PNP 都是在 N-Well 中制作, NMOS 是在 P-Well 中形成。该制程的主要特点如下。

(1)器件隔离是由硅局部氧化(LOCOS)和对通隔离(P-Well / BLP+)构成。

(2)形成双极型器件的基底与 PMOS 的 N-Well深度和浓度相同。

(3)PNP 的发射区/集电区和基区(Pb)接触的P+ 掺杂同时,在 N-Well 中形成源区和漏区,以制得PMOS。

(4)NPN 的发射区/集电区和基区接触的 N+掺杂同时,在 P-Well 中形成源区和漏区,以制得 NMOS。

(5)为了获得大电流下的低饱和压降,采用高浓度的集电极深磷扩散,形成与 BLN+ 埋层相接的深磷区(DN)。

CMOS 的 P-Well深度是十分重要,必须达到BLP+埋层,以便削弱 CMOS 中的“闩锁效应”,并形成双极的对通隔离。阱的深度与 NMOS 特性(UTN,体效应因子以及 BUDS 等)密切相关。因此,必须选择合适的阱深和浓度,以便达到电路电气特性的要求。

由于双极和 CMOS 技术的要求相冲突,亚微米 BiCMOS[B] 阱分布的最佳化是一个多方面的问题。因为 N-Well 提供双极 NPN 和 PMOS 管的基础,大多数临界工艺折衷涉及 N-Well 分布。但是,关键要点如隔离﹑二极管电容以及反掺杂 P-Well 中迁移率降低亦必须都要考虑,特别在 CMOS 加强电路中,NMOS 性能起支配作用。

5 结语

除去芯片表面钝化层光刻外,制程中使用了 16次掩模,各层平面结构与横向尺寸都由各次光刻所确定。制程完成后确定了芯片各层平面结构与横向尺寸和剖面结构与纵向尺寸,并精确控制了硅中的杂质浓度及其分布和结深,从而确定了电路功能和电气性能。芯片结构及其尺寸和硅中杂质浓度及其结深是制程的关键。它们不仅与双极型下列参数:

(1)埋层结深及其薄层电阻;

(2)P 型外延层电阻率及其厚度;

(3)基区宽度及其薄层电阻;

(4)发射区结深及其薄层电阻;

(5)与埋层相接的深磷区结深及其薄层电阻;

(6)器件 fT﹑β﹑BUcEo﹑以及 BUcBo 等。

而且,与 CMOS下列参数:

(1)P 型外延层电阻率;

(2)阱深度及其薄层电阻;

(3)各介质层和栅氧化层厚度;

(4)有效沟道长度;

(5)源漏结深度及其薄层电阻;

(6)器件的阈值电压,源漏击穿电压,以及跨导等有关,如表 1 所示。

此外,双极型与 CMOS 这些参数之间必须进行折衷并优化,以达到互相匹配。制程完成后,先测试晶圆 PCM(表 1 中工艺和电学参数)数据。达到规范值后,才能测试芯片电气特性。

发布评论请先 登录

相关推荐

使用指引:Gel-Pak VTX应用于100微米芯片托盘

芯片微型化挑战极限,成熟制程被反推向热潮

平顶光束剖面都用在哪些地方?

HV-CMOS工艺制程技术简介

亚微米BiCMOS[B]芯片及其剖面结构与制程技术分享

亚微米BiCMOS[B]芯片及其剖面结构与制程技术分享

评论