芯片晶粒在未来搭载愈来愈多晶体管可望成为趋势,让芯片运算能力达到人脑水平也可望有朝一日达成,对于这类新技术的发展,在芯片上以及在多层堆叠芯片之间打造先进3D结构成为一大主要驱动力,在2017年IEEE IEDM大会上也可见相关技术进展的发表及讨论,可以预期的是,数据中心以芯片为基础的电子存储器及嵌入式应用如计算机与工业存储器,朝3D技术发展将成为趋势。

根据富比士(Forbes)报导,除了存储器3D技术趋势外,每颗芯片配置多元存储器以及多层堆叠芯片的设计也将主导许多应用,此外,各类电阻式存储器及MRAM技术也将有助储存级存储器、低功耗与长效物联网(IoT),以及其它不断成长中应用的发展。

台积电在本届IEEE IEDM大会上表示,至2020年业界将可见每晶粒500亿个晶体管的芯片问世,但其复杂度仍比相当于有着约1兆晶体管的人类大脑为低,藉由NVIDIA及其它业者在开发的新兴3D x 3D超级芯片,将可内含2,000亿个晶体管,到那时才会比较接近大脑的复杂度。在芯片上及多层堆叠芯片间打造先进3D结构,成为达成新技术的主要驱力。

新兴非挥发性存储器有助进行神经运算以进行装置中的机器学习(ML),可进一步强化当前神经网络的能力。可变电阻式随机存取存储器(ReRAM)则是受神经存储器芯片青睐采用的技术,因ReRAM可作为突触元件进行操作。

本届IEEE IEDM大会可见许多报告提出改善这些存储器特性的方式,如韩国SK海力士(SK Hynix)发布一份XPoint技术的23纳米ReRAM,这款ReRAM内含砷以创造阀值切换行为;GlobalFoundries发布的报告,则讨论一款7纳米CMOS技术如何用于高性能运算及行动装置。

日本中央大学教授Ken Takeuchi则谈到如何在NAND Flash控制器中提供额外的处理能力,该控制器可辨识特定应用的重要数据,以及将此数据储存于可靠的存储器单元中。在此方法中虽然电路本身的精确度降低,深度学习(DL)的推论结果这类应用级准确度则不会下降。

这也是近似运算(approximate computing)能够被运用于提供在存储器及储存装置内部所采用较小型及功耗更佳处理器更有用功能的原因。未来的数据中心将采用由中央处理器(CPU)、DRAM、储存控制器、储存级存储器(SCMs)以及Flash存储器所组成的非聚合式混合储存技术。

针对MRAM技术,高通旗下高通技术(Qualcomm Technologies)公司出席本届IEEE IEDM大会的代表指出,MRAM准备成为统一的存储器子系统,能够改造物联网及穿戴式装置这类新兴极低功耗系统的架构,且MRAM也可改变以运算为中心的架构。例如面垂直(perpendicular) STT-MTJ MRAM具备快速读写特性,也有助当前的SRAM及DRAM可直接与处理器一同配置。

这将有助以单一MRAM存储器取代应用于许多物联网应用的SRAM及Flash架构,因而减少存储器之间的信息流以及节省功耗支出,这对搭载电池的应用来说特别重要,加上MRAM的位元单元(Bitcell)大小约只有SRAM位元单元的25~30%,因此采用MRAM也可节省晶粒空间。

由于电路简化,让MRAM应可被视为是具成本竞争力的存储器选项,特别是对嵌入式应用而言更是如此,只不过MRAM在成本上仍无法与高密度DRAM相较,因此应用驱动的客制化独立MRAM或较具竞争力,因在价格上比eMRAM为低。

-

芯片

+关注

关注

456文章

50933浏览量

424627 -

3D

+关注

关注

9文章

2894浏览量

107640 -

MRAM

+关注

关注

1文章

236浏览量

31735

原文标题:【供应链】2017年IEEE IEDM大会存储器围绕3D、MRAM及新芯片探讨

文章出处:【微信号:gh_44592200c847,微信公众号:gh_44592200c847】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

3D深度感测的原理和使用二极管激光来实现深度感测的优势

DMD芯片在3D打印中的创新应用

3D集成电路的结构和优势

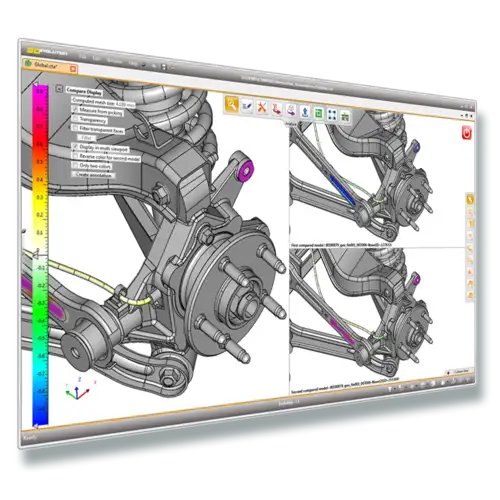

安宝特产品 安宝特3D Analyzer:智能的3D CAD高级分析工具

3D封装热设计:挑战与机遇并存

裸眼3D笔记本电脑——先进的光场裸眼3D技术

西门子推出Calibre 3DThermal软件,持续布局3D IC热分析

英伦科技裸眼3D平板有哪些方面的优势?

奥比中光携多款3D相机深度参与国内3D视觉最高规格会议

新质生产力探索| AICG浪潮下的3D打印与3D扫描技术

基于深度学习的方法在处理3D点云进行缺陷分类应用

对3D、MRAM及新芯片的深度分析和探讨

对3D、MRAM及新芯片的深度分析和探讨

评论