硅晶圆相对容易处理,并且良好的实践和自动设备已将晶圆断裂降至低水平。然而,砷化镓晶圆并不是那么坚韧,断裂是主要的晶圆良率限制因素。在砷化镓制造线上,电路的售价很高,通常会处理部分晶圆。

除了最小化断裂外,晶圆表面在整个加工过程中必须保持平坦。这在特别是使用将图案投影到晶圆表面的图案技术的生产线上是正确的。如果表面翘曲或波纹状,投影的图像将变得扭曲并改变所需的图像尺寸。这类似于在扭曲的屏幕上投影幻灯片。翘曲是由在炉管中快速加热和/或冷却晶圆引起的。

3、工艺变化

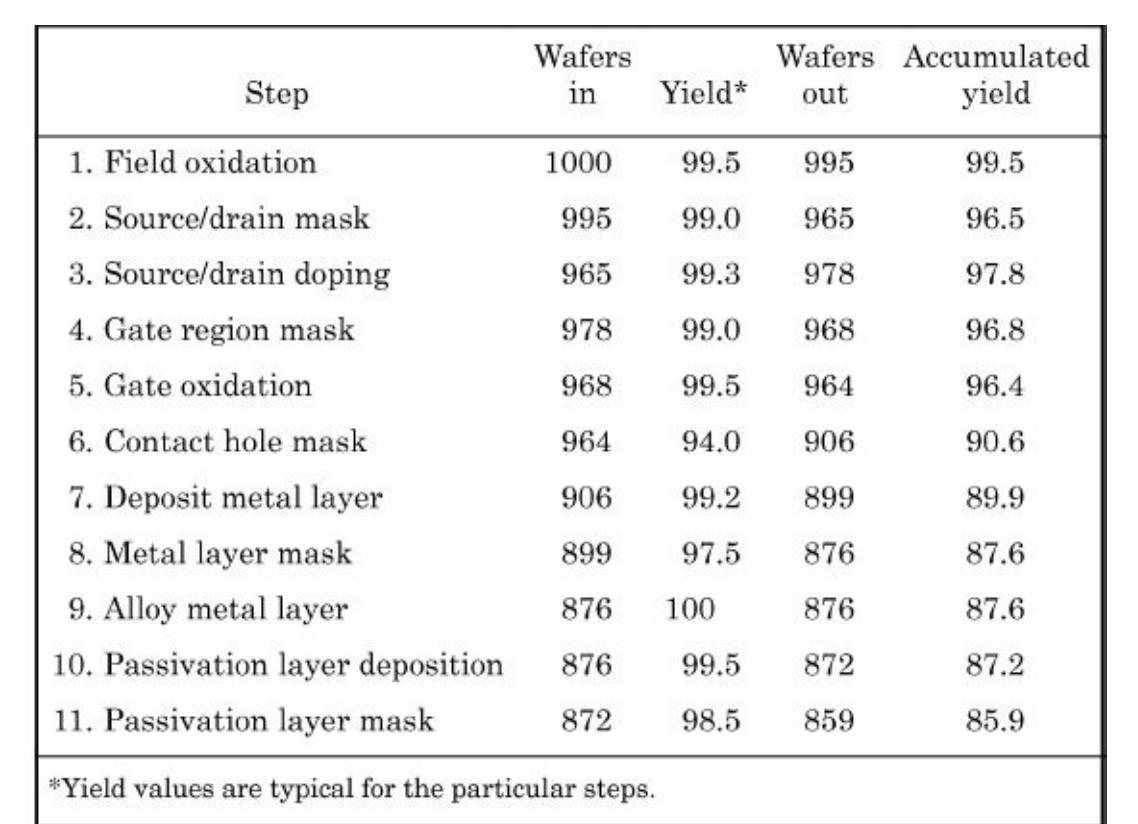

当晶圆通过制造过程时,它接受了许多掺杂、层叠和图案化工艺,每一个都必须满足难以置信的严格的物理和清洁要求。但即使是最复杂的工艺也会从晶圆到晶圆、批次到批次、日复一日地变化。当一个工艺超出其工艺限制(超出规格)时,它会导致晶圆上或晶圆上的芯片出现一些不允许的结果。

工艺工程和工艺控制程序的目标不仅是保持每个工艺在其控制规格内运行,而且还要维持工艺参数的恒定分布,如时间、温度、压力等。这些工艺参数是使用后面章节中解释的统计过程控制技术进行监控的。

在整个过程中,有许多检查和测试旨在检测不需要的变化,以及对设备参数进行频繁校准以满足工艺规格。其中一些测试由生产人员执行,有些由质量控制组织执行。然而,即使是维护和监控得最好的工艺也会表现出一些变化。工艺工程和电路设计的挑战之一是适应这些变化,并且仍然拥有一个功能设备。

4、工艺缺陷

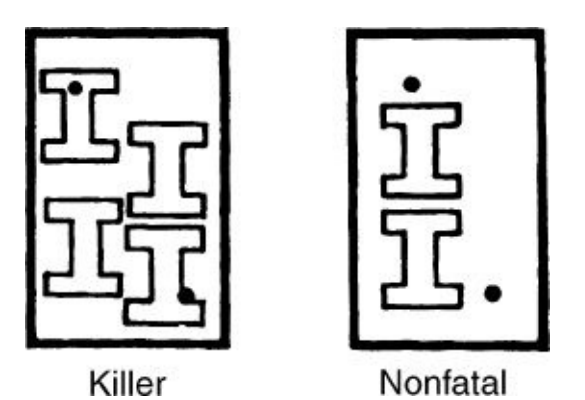

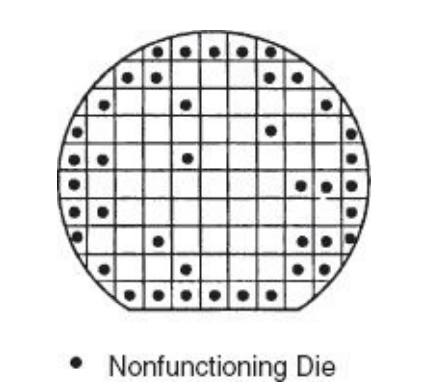

工艺缺陷被定义为晶圆表面上的污染或不规则性的孤立区域(或斑点)。这些缺陷通常被称为斑点缺陷或点缺陷。它们随机出现在晶圆表面上。有些不是致命的,有些会使电路无法操作。后者被称为致命缺陷(见下图)。不幸的是,较小的缺陷有时在制造过程中无法检测到。它们在晶圆分选中显现为被拒绝的芯片。

这些缺陷的主要来源是制造区域使用的液体、气体、室内空气、人员、工艺机器和水。颗粒和其他小污染物会附着在晶圆表面。许多这些缺陷发生在图案化过程中。回想一下,图案化过程需要使用一层薄而脆弱的光刻胶来在刻蚀步骤中保护晶圆表面。来自颗粒的任何孔洞或撕裂将在晶圆表面层中以微小的刻蚀孔结束。这些孔被称为针孔,是光刻工程师主要关注的问题。因此,晶圆经常进行污染检查,通常在每个主要步骤之后。超过既定允许密度的晶圆将被拒绝。半导体行业协会(SIA)的国际半导体技术路线图(ITRS)要求300毫米晶圆表面的缺陷密度最大为每平方厘米0.68个。

5、掩模缺陷

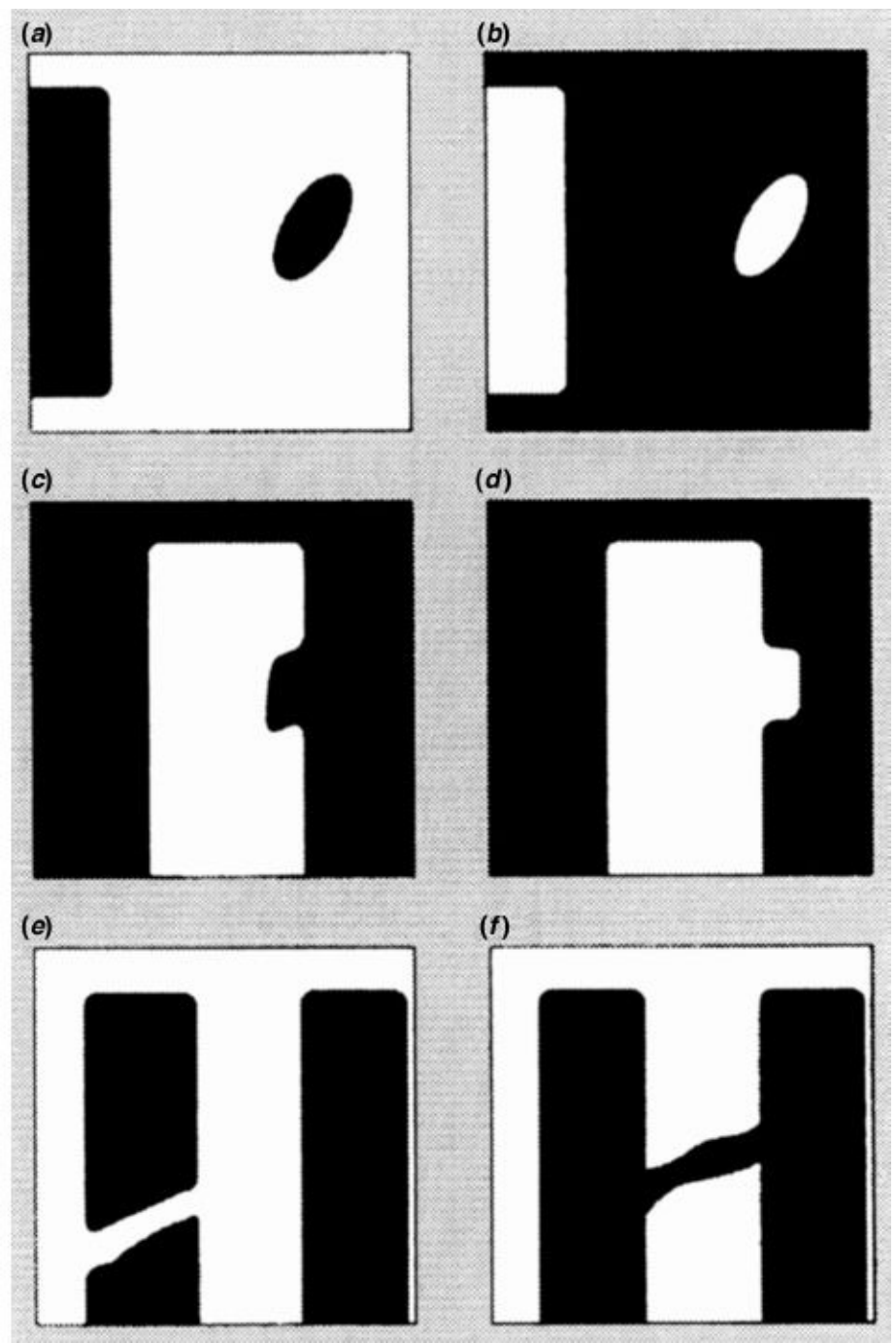

光掩模或光栅是图案化过程中转移到晶圆表面的图案的来源。掩模或光栅上的缺陷最终会成为晶圆上的缺陷或图案畸变。有三种常见的掩模或光栅引起的缺陷。首先是污染,例如掩模或光栅的透明部分上的污垢或污点。在光刻中,它们可以阻挡光线并将像图案的不透明部分一样印在晶圆上。第二是光栅石英板中的裂纹。它们也可以阻挡图案化光线和/或散射光线,导致不需要的图像和/或扭曲的图像。第三是掩模或光栅制造过程中出现的图案畸变。这些包括针孔或铬点、图案扩展或缺失部分、图案断裂或相邻图案之间的桥接(见下图)。对于具有更小特征尺寸、更高密度和更大裸片尺寸的设备或电路,控制掩模产生的缺陷更为关键。

-

芯片

+关注

关注

454文章

50677浏览量

423007 -

半导体

+关注

关注

334文章

27250浏览量

217917 -

晶圆

+关注

关注

52文章

4884浏览量

127915 -

工艺缺陷

+关注

关注

0文章

4浏览量

6032

原文标题:半导体工艺之生产力和工艺良率(三)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶圆制造良率限制因素简述(2)

晶圆制造良率限制因素简述(2)

评论