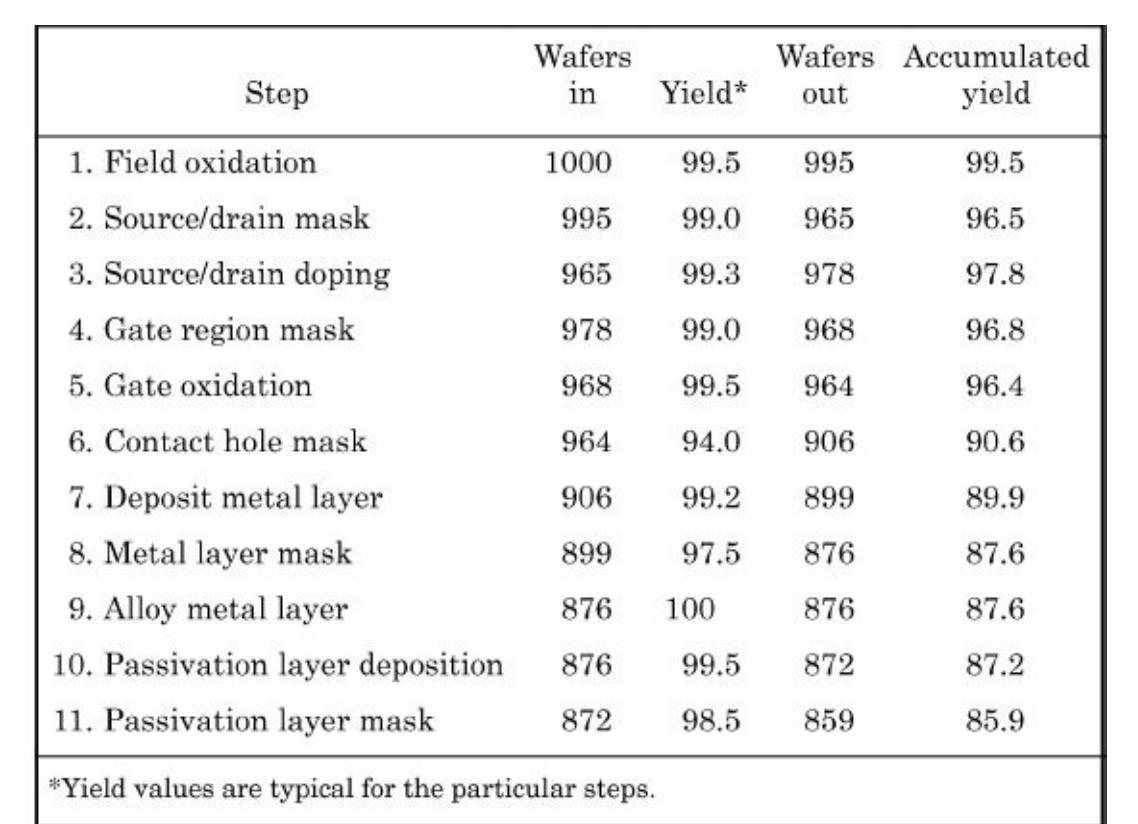

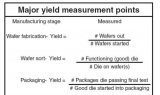

下图列出了一个11步工艺,如第5章所示。典型的站点良率列在第3列,累积良率列在第5列。对于单个产品,从站点良率计算的累积fab良率与通过将fab外的晶圆数量除以fab线开始的晶圆数量计算的良率相同。累积良率等于这个单独电路的简单累积fab良率计算。请注意,即使有非常高的单个站点良率,随着晶圆通过工艺,累积fab良率仍将持续下降。一个现代集成电路将需要300到500个单独的工艺步骤,这对维持盈利的生产率是一个巨大的挑战。成功的晶圆制造操作必须实现超过90%的累积制造良率才能保持盈利和竞争力。

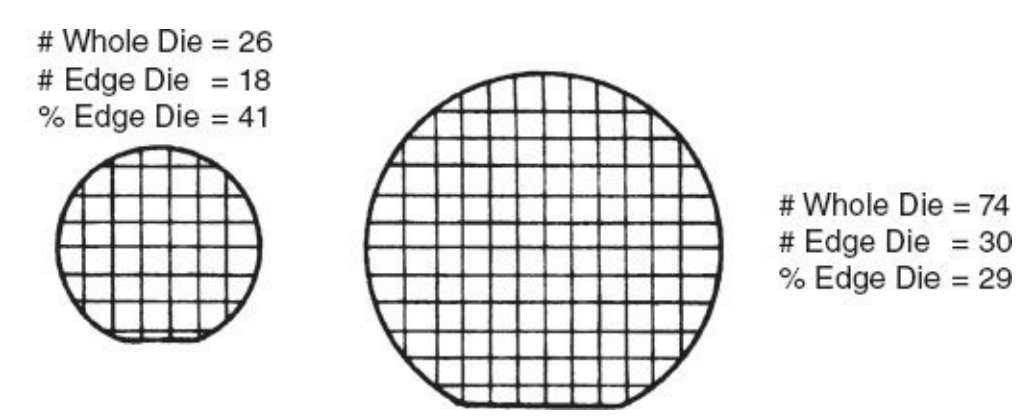

晶圆制造累积良率在50%到95%之间变化,这取决于许多因素。计算出的累积良率用于生产计划以及工程和管理,并作为衡量工艺效果的指标。

晶圆制造良率限制因素

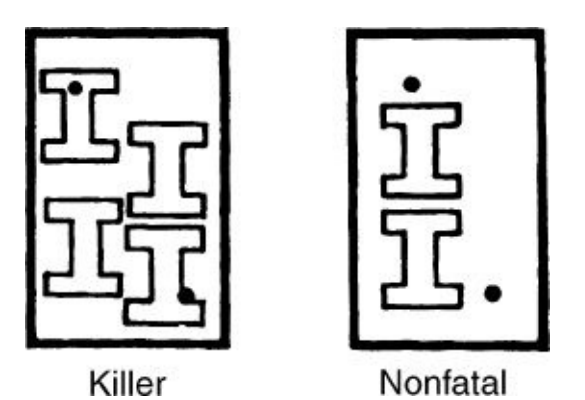

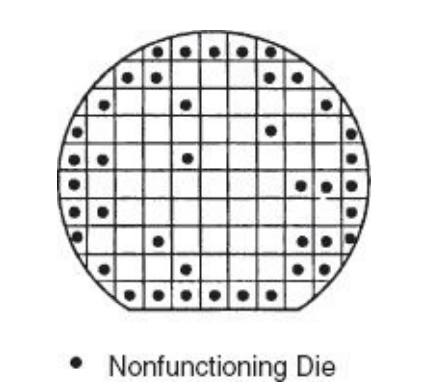

晶圆制造良率受到许多因素的限制。下面列出的五个是任何晶圆制造设施都必须控制的基本因素。这些基本因素结合设备或电路特定因素,导致给定设施生产出好芯片的整体良率。

1. 工艺步骤数量

2. 晶圆断裂和翘曲

3. 工艺变化

4. 工艺缺陷

5. 掩模缺陷

1、工艺步骤数量

在上图的计算中,请注意,每个单独的工艺操作良率必须在高90%范围内,以产生85.9%的累积fab良率。举例来说,这是一个相当简单的11步工艺。超大规模集成(ULSI)电路需要数百个主要工艺操作。对于最前沿的产品,具有数百个操作的过程是典型的。

每个操作都需要几个步骤,每个步骤又涉及许多子步骤。可以很容易地理解,由于工艺步骤的数量,对制造区域维持高累积良率的持续压力。电路越复杂,步骤数量越多,预期的累积良率就越低。

更多的工艺步骤还增加了其他四个良率限制因素在工艺过程中影响晶圆的可能性。这个因素是数字的暴政。例如,要实现50步工艺的75%累积制造良率,每个单独步骤必须达到99.4%。这种计算类型的另一个暴政是,累积fab良率永远不能超过最低单个步骤良率。如果一个工艺步骤只能达到50%的良率,整体累积良率就永远不可能高于50%。

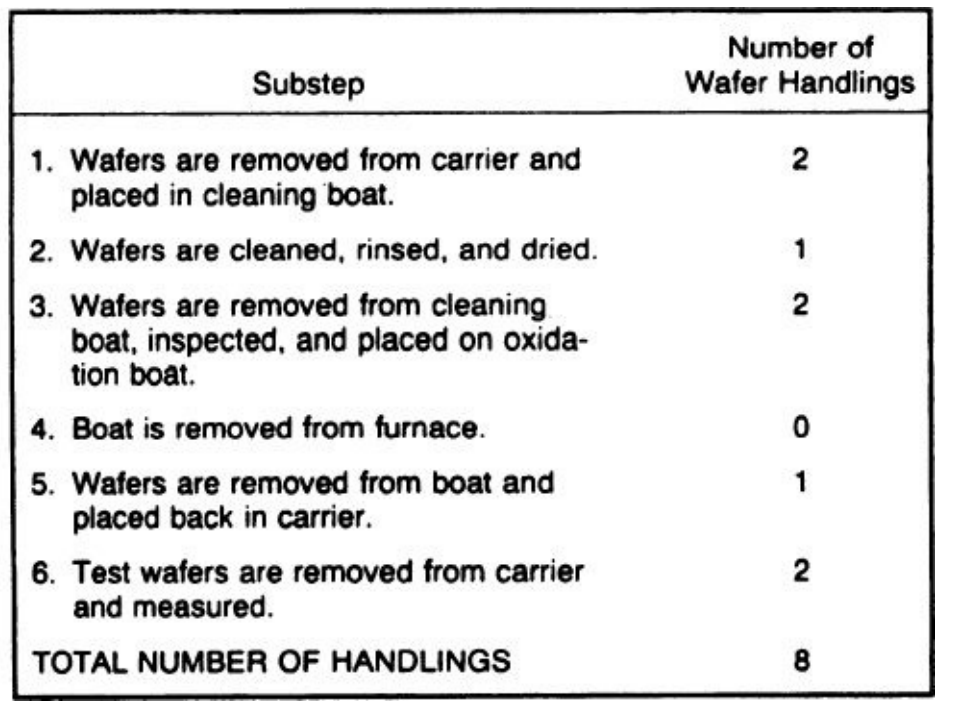

对于每个主要工艺操作,都有一些步骤和子步骤。在所展示的11步工艺中,第一个操作是氧化。一个简单的氧化过程需要几个步骤:清洁、氧化和评估。每个步骤都需要子步骤。下图列出了一个典型的氧化过程的六个子步骤。每个子步骤都代表了污染、断裂或损坏晶圆的机会。自动化和隔离技术为晶圆环境提供了更多的控制,但每次转移和新的工艺环境都为污染和缺陷提供了机会。

2、晶圆断裂和翘曲

在制造过程期间,晶圆通过手动和自动技术的组合多次被处理。每次处理都为打破相对脆弱的晶圆提供了机会。一个典型的300毫米(12英寸)直径晶圆只有大约800微米厚。需要仔细处理晶圆,并且必须维护自动处理器以最小化断裂。

热处理增加了晶圆断裂的敏感性。在晶体材料中引入了应变,这使得晶圆在后续步骤中容易断裂。自动处理机器只能容纳全直径晶圆。因此,任何断裂,无论多小,都是从工艺中拒绝晶圆的原因。

-

芯片

+关注

关注

458文章

51526浏览量

429480 -

晶圆

+关注

关注

52文章

5021浏览量

128608 -

工艺

+关注

关注

4文章

622浏览量

29004 -

晶圆制造

+关注

关注

7文章

287浏览量

24199

原文标题:半导体工艺之氧化(二)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶圆制造良率限制因素简述(1)

晶圆制造良率限制因素简述(1)

评论