在PCB(印刷电路板)设计中,降低电磁兼容性(EMC)问题是一个至关重要的环节。EMC问题主要涉及电磁干扰(EMI)和电磁敏感度(EMS)两个方面,其中EMI是指设备或系统在其正常工作过程中产生的电磁场对其他设备或系统造成的干扰,而EMS则是指设备或系统对外部电磁场的敏感程度。以下将从多个方面详细探讨在PCB设计中如何有效降低EMC问题。

一、接地设计

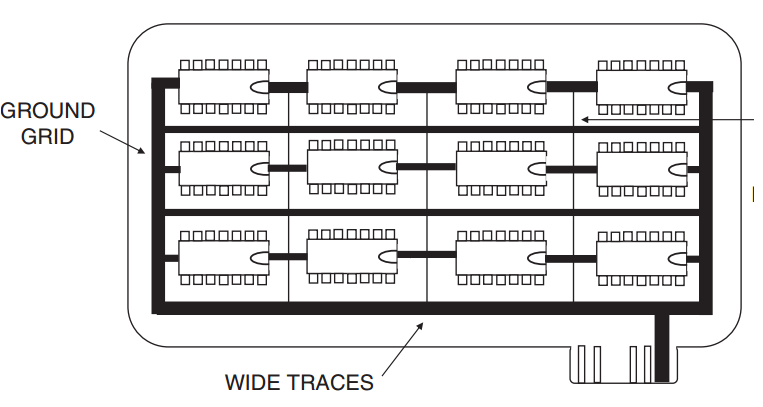

- 设计PCB接地层

- 降低EMI的一个重要途径是设计PCB接地层。应使PCB电路板总面积内的接地面积尽可能大,以减少发射、串扰和噪声。

- 将每个元器件连接到接地点或接地层时必须特别小心,以确保充分利用可靠的接地层的中和效果。

- 理想情况下,每个参考电压都有自己对应的接地层。然而,接地层过多会增加PCB的制造成本。折衷的办法是在三到五个不同的位置分别使用接地层,每一个接地层可包含多个接地部分,以控制成本并降低EMI和EMC。

- 低阻抗接地系统

- 模拟与数字电路分开接地

- 模拟电路的安培数较高或电流较大,应远离高速走线或开关信号。如果可能,应使用接地信号保护它们。

- 在多层PCB上,模拟走线的布线应在一个接地层上,而开关走线或高速走线应在另一个接地层上,以分开不同特性的信号。

二、走线设计

- 走线长度与返回路径

- 向/从信号源传输电流的走线应尽可能短,以避免源路径和返回路径长度不相等导致的接地反弹和EMI。

- 返回路径走线的长度应与发送走线的长度相同,以减少串扰和EMI。

- 并行走线处理

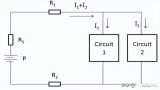

- 两个并行的高速信号会产生EMC和EMI,特别是串扰。应使电阻路径最短,并使返回电流路径也尽可能短。

- 如果使并行走线之间的宽度为走线宽度的两倍,则串扰的影响可降至最低。例如,走线宽度为5密耳时,两条并行走线之间的最小距离应为10密耳或更大。

- 避免直角走线

- 直角走线会产生辐射,增加电容和特性阻抗的变化,导致反射和EMI。因此,走线应避免90°角,而应至少以两个45°角布线到拐角处。

- 关键信号的带状线布局

- 对于关键信号,应采用带状线布局,以提供更好的电磁屏蔽和降低串扰。

三、电源与接地平面设计

- 电源与接地面相邻

- 将电源和接地面尽可能地放在相邻的层上,以减少电磁干扰。

- 平行电源和地平面对

- 使用尽可能多的平行电源和地平面对,以增强电磁屏蔽效果。

- 电源平面边缘内缩

- 电源平面边缘应内缩,以小于接地平面的尺寸,并沿边缘在接地平面之间通孔互连,以减少电磁泄漏。

四、元器件布局与布线

- 元器件分组与滤波

- PCB上的组件应根据功能进行分组,每个组件的信号走线必须保持在定义的区域内。

- 当信号需要从一个子系统连接到另一个子系统时,可以使用滤波器来减少电磁干扰。

- 高速信号与接地层邻近

- 在高速情况下,信号和时钟应尽可能短并邻近接地层,以控制串扰、噪声和辐射。

- 数字信号与电源平面的距离

- 数字信号应远离电源平面,以减少噪声和感应,从而保持信号强度。

五、去耦电容与滤波器的使用

- 去耦电容的放置

- 去耦电容可减少串扰的不良影响,应位于设备的电源引脚和接地引脚之间,以确保交流阻抗较低。

- 为了在宽频率范围内实现低阻抗,应使用多个去耦电容。电容值最小的电容器要尽可能靠近设备,以减少对走线产生电感影响。

- 滤波器的应用

- 有时可以用一个低通滤波器来消除与周围走线耦合的高频噪声。滤波器可以抑制噪声,返回稳定的电流。

- 所有外部I/O信号应进行低通滤波,使用可容忍的最长信号上升时间,以减少电磁干扰。

六、差分信号与对称设计

- 差分信号的走线设计

- 尽量减少每对差分线之间的非对称现象,以保持信号的完整性并减少电磁干扰。

- 对称布局

- 在PCB布局中,应保持对称布局,以减少电磁场的不均匀分布和降低EMI。

七、物理屏蔽与接地

- 物理屏蔽的使用

- 使用金属封装包住整个或部分系统,以防止EMI进入PCB电路。这种屏蔽像是封闭的接地导电容器,可减小天线环路尺寸并吸收EMI。

- 屏蔽层与金属机壳的接触

- 连接屏蔽电缆时,尽量保障屏蔽层和金属机壳之间的接触完整,将屏蔽作为外壳的延伸。

- 避免使用“猪尾巴”辫线用于线缆屏蔽层和金属机壳之间的连接,以减少电磁泄漏。

八、其他设计考虑

- 了解电路板的谐振频率

- 如果存在与使用时钟信号重叠的谐波,尝试改变封装的几何形状,以消除该谐波,从而减少EMI。

- 避免信号参考不同的电源平面层

- 信号应尽可能在同一电源平面层上传输,以减少不同电源平面层之间的电磁干扰。

- 合理使用磁珠

- 磁珠可用于消除表层谐振,特别是在高频应用中。它们可用于抑制高频噪声,并吸收电磁干扰。

- 跨板设计的处理

- 在PCB跨板设计时,应在连接处使用共模电感,以减少电磁干扰的传播。

- 外接线缆的处理

- 外接线缆时,在线缆上使用共模电感或者扼流圈,以减少电磁干扰的辐射和接收。

- 孔缝设计

- PCB设计不能破坏金属机壳的完整性。孔缝的设计应使其最大尺寸明显小于可能泄漏的最低频率辐射的波长,以减少电磁泄漏。

- 数量多而尺寸小的孔缝设计通常比数量少而尺寸大的孔缝设计具有更好的屏蔽效果。

九、信号完整性考量

在PCB设计中,信号完整性(Signal Integrity, SI)与EMC问题密切相关。确保信号的完整性不仅可以提高系统的性能,还能有效降低电磁干扰。

- 阻抗匹配

- 阻抗匹配是确保信号在传输线上不产生反射的关键。传输线的阻抗应与源和负载的阻抗相匹配,以减少信号的损失和反射。

- 在PCB设计中,可以通过选择合适的走线宽度、介质厚度和介电常数来实现阻抗匹配。

- 减少传输线效应

- 传输线效应,如延迟、衰减和色散,会对信号的完整性产生负面影响。在高速信号传输中,这些效应尤为明显。

- 通过缩短传输线长度、使用低损耗材料和增加传输线的宽度,可以减少这些效应的影响。

- 避免信号间的串扰

- 串扰是信号完整性问题的常见来源,它会导致信号失真和误码率增加。

- 在PCB设计中,可以通过增加走线间距、使用差分信号和屏蔽技术来减少串扰。

- 终端电阻的使用

- 在某些情况下,使用终端电阻可以帮助吸收反射波,从而改善信号的完整性。

- 终端电阻的选择应基于传输线的阻抗和信号的特性。

十、电源管理

电源管理对于降低EMC问题同样至关重要。不稳定的电源会导致电压波动和噪声,进而增加电磁干扰。

- 电源去耦

- 电源去耦是减少电源噪声的有效方法。通过在电源引脚附近放置去耦电容,可以吸收电源线上的高频噪声。

- 去耦电容的选择应基于电源噪声的频率特性和电容的阻抗特性。

- 电源滤波

- 电源滤波是另一种减少电源噪声的方法。通过在电源线上添加滤波器,可以滤除不需要的高频成分。

- 滤波器的设计应基于电源噪声的频率特性和系统的性能要求。

- 电源完整性

- 电源完整性(Power Integrity, PI)是指电源在系统中的稳定性和可靠性。确保电源完整性可以降低电磁干扰并提高系统的性能。

- 在PCB设计中,可以通过优化电源布局、使用低阻抗电源平面和增加电源去耦电容来提高电源完整性。

十一、软件层面的优化

虽然本文主要讨论的是PCB设计中的硬件层面优化,但软件层面的优化同样重要。通过软件层面的优化,可以进一步降低EMC问题。

- 时钟频率的选择

- 时钟频率是电磁干扰的主要来源之一。通过选择较低的时钟频率,可以减少电磁辐射和接收。

- 在可能的情况下,可以使用分频器或锁相环(PLL)来降低时钟频率。

- 信号编码与调制

- 使用适当的信号编码和调制技术可以减少电磁干扰。例如,差分信号编码和扩频调制都可以降低电磁辐射。

- 软件滤波

- 在软件层面添加滤波器可以进一步减少噪声和电磁干扰。例如,可以使用数字滤波器来平滑信号并去除高频噪声。

十二、测试与验证

在PCB设计完成后,进行测试与验证是确保EMC性能的关键步骤。通过测试,可以发现潜在的问题并进行修正。

- EMC测试

- 进行EMC测试是验证PCB设计是否符合相关标准和法规的必要步骤。测试包括辐射发射测试和传导发射测试等。

- 根据测试结果,可以对PCB设计进行调整和优化,以降低电磁干扰。

- 信号完整性测试

- 信号完整性测试是验证信号在PCB上传输过程中是否保持完整性的关键步骤。测试包括时域反射测试(TDR)和眼图测试等。

- 通过信号完整性测试,可以发现潜在的信号传输问题并进行修正。

- 热测试

- 热测试是验证PCB在正常工作过程中是否会产生过热问题的关键步骤。过热会导致电磁干扰增加和元件失效。

- 通过热测试,可以发现潜在的散热问题并进行修正,以确保PCB的可靠性和稳定性。

十三、总结与最佳实践

在PCB设计中降低EMC需要综合考虑多个方面,包括接地设计、走线设计、电源与接地平面设计、元器件布局与布线、去耦电容与滤波器的使用、差分信号与对称设计、物理屏蔽与接地以及其他设计考虑。通过遵循以下最佳实践,可以显著降低EMC问题:

- 最大化接地面积,使用低阻抗接地系统。

- 保持走线长度一致,避免直角走线。

- 将电源和接地面相邻放置,使用平行电源和地平面对。

- 根据功能分组元器件,使用滤波器减少电磁干扰。

- 放置去耦电容,确保交流阻抗较低。

- 尽量减少差分线之间的非对称现象。

- 使用物理屏蔽防止EMI进入PCB电路。

- 了解并避免电路板的谐振频率。

- 合理使用磁珠和共模电感抑制高频噪声。

- 在跨板设计和外接线缆时使用共模电感或扼流圈。

- 设计孔缝时确保其尺寸小于最低频率辐射的波长。

综上所述,通过综合运用这些最佳实践,可以显著提高PCB的EMC性能,降低电磁干扰和电磁敏感度,从而确保设备的可靠性和稳定性。

-

电路板

+关注

关注

140文章

5009浏览量

99274 -

emc

+关注

关注

170文章

3967浏览量

184076 -

PCB

+关注

关注

1文章

1835浏览量

13204

发布评论请先 登录

相关推荐

PCB设计中EMC/EMI的仿真

EMC之PCB设计技巧

PCB设计考虑EMC的接地技巧

PCB设计中的EMC概念

PCB设计中怎么降低EMC

PCB设计中怎么降低EMC

评论