OrCAD PSpice A/D和高级分析技术(A/A)结合了业界先进的模拟、模数混合信号以及分析工具,以提供一个完整的电路仿真和验证解决方案。

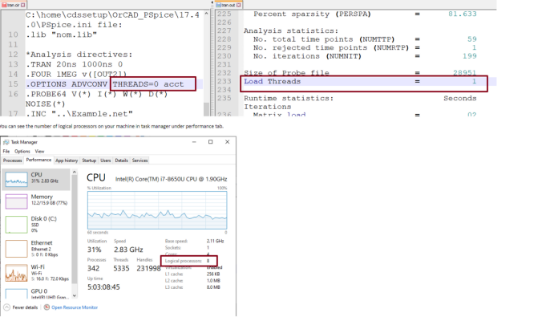

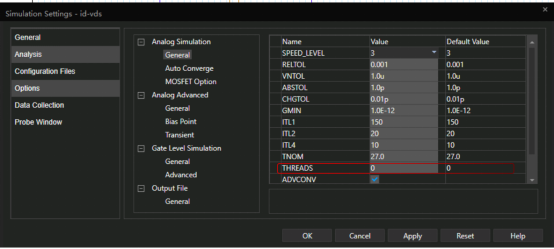

PSpice尝试使用机器资源的优化数量来提供高效性能。这由选项THREADS控制,

“THREADS=0”是默认值,这意味着线程数由PSpice确定。

PSpice根据以下因素创建默认数量的模拟线程:

器件计数:如果器件计数过低,则创建额外线程没有帮助。大约每10个器件创建1个线程。

系统上的内核数:模拟线程数不超过逻辑处理器数。

PSpice在内部为每个器件提供一个数字。例如,电阻为0.5,而BSIM mosfet可能为1.5。这是基于该器件模型的计算复杂性。核心数量取决于加权器件计数。例如,如果器件数量为200个,但都是电阻器,那么与200个MOSFET相比,pspice将使用更少的芯。

当器件计数较少时,由于额外的线程创建和调度时间,增加线程会使性能更差,而减少的器件加载时间并不能补偿额外的线程创建和调度时间。因此,它不应用于器件少的电路。

注:此选项将模拟瞬态模拟的每个时间步的计算并行化。参数扫描、蒙特卡罗和数字器件模拟的不同运行没有并行化。

如果你为线程指定了一个非零值,PSpice会接受这个值,并创建指定数量的线程。

例如:THREADS=1表示创建了单个线程。

现在,您可以在中转储线程使用情况。通过在中添加帐户来输出文件。选项行输入.cir文件,以查看正在使用的线程数。将其与计算机上可用的逻辑处理器数量进行比较。如果您认为增加线程数会有所帮助,请在设置中增加它,然后查看模拟速度是否会增加。

总结:建议将THREADS=0(默认值),并让系统确定值。当然也可以根据实际情况添加分析线程。

-

混合信号

+关注

关注

0文章

542浏览量

65933 -

仿真

+关注

关注

55文章

4535浏览量

138659 -

PSPICE

+关注

关注

18文章

228浏览量

74083 -

orcad

+关注

关注

27文章

304浏览量

120576

原文标题:【技术指南】如何提升Pspice仿真速度?

文章出处:【微信号:封装与高速技术前沿,微信公众号:封装与高速技术前沿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

请问硬件仿真的速度能达到甚至超过软件仿真的速度吗?

如何提高MPLAB X仿真速度?

请问硬件仿真的速度能达到甚至超过软件仿真的速度吗?

Cadence PSpice仿真技术的优势有哪些

Spice仿真器:仿真速度和容量的提升

放大器仿真模型可提高SPICE仿真速度

如何提升Pspice仿真速度

如何提升Pspice仿真速度

评论