随着超大规模集成电路工艺的发展,人类已经进入了超深亚微米时代。先进的工艺使得人们能够把包括处理器、存储器、模拟电路、接口逻辑甚至射频电路集成到一个大规模的芯片上,形成所谓的SoC(片上系统)。

作为SoC重要组成部分的嵌入式存储器,在SoC中所占的比重(面积)将逐渐增大。下面就随嵌入式小编一起来了解一下相关内容吧。

何为嵌入式存储器

嵌入式存储器现在已经不是一个新的概念了。相对于片外存储器,嵌入式存储器是指集成在片内与系统中各个逻辑、混合信号等IP共同组成单一芯片中的存储器。现已经成为SOC芯片的基本组成部分,几乎今天每个SOC芯片中嵌入式存储器都占有一定比重。

按照掉电后数据是否会丢失,可将嵌入式存储器分为两大类,一类是挥发性存储器,另一类则是非挥发性存储器。挥发性存储器是指掉电后数据会丢失,主要包括速度快、功耗低的SRAM和高密度的DRAM。而非挥发性存储器则刚好相反,其在实际应用中主要包括eFlash、EEPROM以及eMRAM、eRRAM、ePRAM等次世代存储器。

虽然都是存储器,但二者还是有些许不同。嵌入式存储器和分立式存储器最重要的不同之处在于嵌入式存储器往往跟应用IC自身的工艺特性条件有很大关系,比如用90nm和用45nm工艺做出来的芯片,其内部嵌入式存储器大小差别也是很大的。而分立式存储器件则主要围绕存储器器件工艺进行优化。

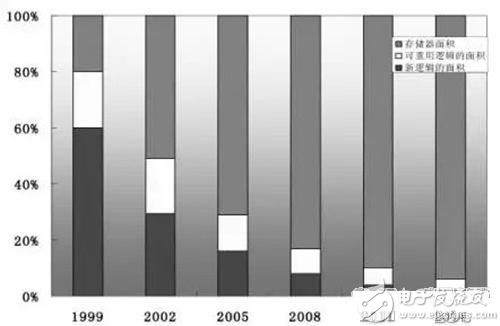

随着信息技术的发展,嵌入式存储器在SOC中的面积所占比重也在逐年增加,从图一可以看出,从1999年平均的20%上升到2007年的60-70%乃至2014年的90%的面积。可以看出,嵌入式存储器对于芯片系统性能的影响越来越大。

图一 嵌入式存储器在SOC中所占芯片面积的比重

嵌入式存储器发展历程

早在上世纪六七十年代,那时的半导体行业主要由IDM占据,每个公司从芯片设计、制造到封装都自己做。各家都是独立开发自己的工艺、IP和相关芯片。

早期人们对于系统的要求包括集成度、速度、功耗都不高,因此分立式存储器在那时占据主流位置,成为各应用厂家的首选。

后来到了上世纪八九十年代,fabless和foundry模式开始出现,基于设计的复杂性以及产品设计周期两方面考虑,开始出现第三方的独立IP供应商,如ARM公司。

随着芯片集成度的不断提升,反过来给分立存储器带来了两大挑战:1)集成度和工艺开始允许片内集成更多的存储器;2)存储器的速度发展远远落后于MPU的速度,MPU速度以每年60%在成长,而存储器只有10%。二者速度之间增长的差异,如图二所示。

图二 MPU于DRAM随时代变迁而发展的关系图

同时片内存储器具有灵活简单的接口、更低延迟和更宽总线,更为重要的是还能节省系统的空间大小,使得它日益受到集成电路设计师的青睐。在这一时期嵌入式存储器主要以SRAM和DRAM两种形式呈现。

到了九十年代中期,Intel做了一项重大创新,将片外高速缓冲器(Cache)集成到了片内。这直接导致当时一大批分立的片外高速缓冲存储器厂商倒闭,成为嵌入式存储器代替分立式存储器的标志性事件。

到了今天一颗手机处理器超过90%的面积由各种嵌入式SRAM如寄存器堆,一二级缓存甚至三级缓存组成,嵌入式SRAM也成为晶圆代工厂的工艺技术衡量指标。由于SRAM由六个晶体管组成,而DRAM只有一个晶体管加一个电容组成,具有面积优势,当时很多厂商其实都在思考将DRAM嵌入到系统的可能性。

九十年代,当时IBM,Toshiba等大公司都在尝试开发嵌入式DRAM。但开发并不顺利,开发的难点在于DRAM工艺与常规逻辑工艺差异很大,工艺的整合难度相当大。虽然到今天,随着工艺的进步,使得一些公司像TSMC也在重新审视eDRAM的可行性,并有部分成果,但是主流的设计还是没有将eDRAM纳入必备选项。

后来随着消费类电子大幅成长,不断扩大的存储需求刺激着嵌入式闪存(eFlash)不断发展。从早期,设计人员将程序简单固化在ROM中,到后来的OTP,EEPROM乃至现在很火的高密度eFlash内存。嵌入式内存能够有效存储代码和数据,而且掉电后还不丢失,对很多应用都有重要意义。

然而走到今天,现有存储技术暴露的一些缺陷,比如SRAM、DRAM的问题在于其易失性,断电后信息会丢失且易受电磁辐射干扰,这一缺陷极大限制了其在国防航空航天等一系列关键高科技领域的应用。而FLASH、EEPROM的写入速度慢,且写入算法比较复杂,无法满足实时处理系统中高速、高可靠性写入的要求,且功耗较高,无法满足嵌入式应用的低功耗要求。

新型存储器跃跃欲试

对于现有信息存储产品的性能有了更高要求,迫切需要在存储材料和技术方面取得突破。在这些需求的驱动下,相继出现了一些新型非易失存储器,如铁电存储器(FRAM)、相变存储器(PRAM)、磁存储器(MRAM)、阻变存储器(RRAM)。虽然说这些是新型存储器,但从某个角度看,这些存储器已经存在有一段日子了。

(1)铁电存储器(FRAM)

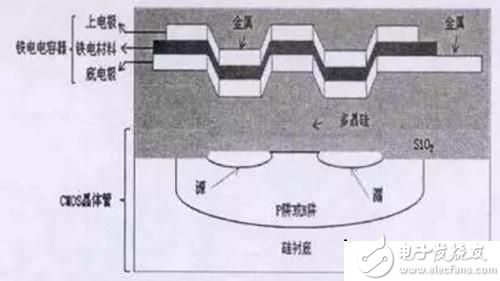

铁电存储器是一种掉电后信息不丢失的非易失存储器,具有高速、高密度、低功耗和抗辐射等优点。其核心基础是铁电晶体材料,采用铁电效应作为其电荷存储机制,同时拥有随机存取存储器(RAM)和非易失性存储产品的特性。其结构图如下图所示。FRAM的工作原理是利用金属-铁电-半导体场效应晶体管结构,铁电薄膜用来替代MOS管中的栅极氧化硅层,铁电薄膜保持着两个稳定的极化状态,分别表示“1”和“0”。

图三 FRAM结构剖面图

(2)磁性存储器(MRAM)

MRAM是利用材料的磁场随磁场的作用而改变的原理所制成。利用磁存储单元磁性隧道结(MTJ)的隧穿磁电阻效应来进行存储。

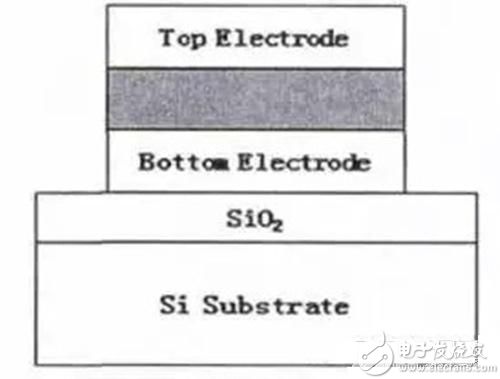

如下图四所示,MTJ有三层,最上层为自由层,中间是隧道结,下面是固定层。自由层的磁场极化方向是可以改变的,而固定层的磁场方向固定不变。当自由层与固定层的磁场平行时,存储单元呈现低阻态;当磁场方向相反时,存储单元呈现高阻态。MRAM通过检测存储单元电阻的高低,来判断所存数据是0还是1。

图四 MJT结构示意图

(3)相变存储器(PRAM)

PRAM的存储原理是利用某些薄膜合金的结构结构相变存储0和1的信息。通常这些合金具有两种稳定状态:具有低电阻的多晶状态和具有高电阻的无定形状态。PRAM应用硫系玻璃材料,利用硫族材料的电致相变特性,其在晶体和非晶体状态呈现不同的电阻特性。当被加热时呈晶体状,为1状态;当冷却为非晶体时,为0状态。通过改变流过该晶体的电流就可以实现这两种状态的转换。

(4)阻变式存储器(RRAM)

RRAM的原理是通过特定的薄膜材料的电阻值在不同电压下呈现的电阻值不同来区分0和1的值。RRAM的存储单元具有简单的金属/阻变存储层/金属(MIM)三明治结构如图六所示。

图五 RRAM器件结构图

哪种存储会是未来的选择?

FRAM的读写速度主要取决于铁电材料的极化反转特性,根据目前理论极化反转速度可达到皮秒量级。

MRAM利用磁性存储数据,容量成本低,具有低功耗、高速存取、无限次读写、抗辐射能力强等优点,在军事、航空航天、移动通讯等领域的应用有很大优势。

PRAM被认为是FLASH和DRAM的替代者,读写速度是普通闪存的30倍,同时其擦写寿命也是闪存的10倍。PRAM的最大优点是高效能和低耗电。

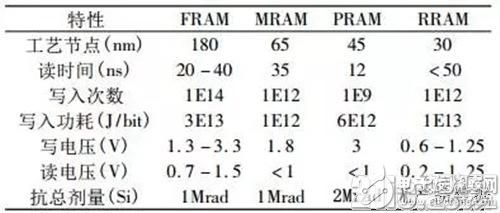

RRAM具有与CMOS工艺兼容性好、低功耗、易于随先进工艺微缩等优点受到广泛关注。总结这几种新式存储器优缺点如下表所示。

表一 几种存储器性能对比

新型存储器挑战

FRAM目前作为新型存储器的主要问题是铁电薄膜材料。未来发展需要解决的主要难题:一是采用3D结构缩小单元面积提高集成度;二是提高铁电薄膜特性。

RRAM还是一项前沿的研究课题,目前还主要停留在实验室阶段。未来材料的寻找仍然是RRAM面临的主要问题。

而台积电未来选择先生产的MRAM和PRAM也会遇到挑战。MRAM的主要问题在于其高昂的制造成本。其次MRAM依靠磁性存储材料,磁场会对周围的芯片产生怎样的影响需要仔细考虑。

而PRAM的最大问题是成本和容量。目前PRAM的单位容量成本还是比NAND高不少。发热对于PRAM而言是个大问题,由于PRAM需要加热电阻式材料发生相变,随着工艺越来月先进,单元变得越来越精细,对于加热元件的控制要求也将越来越高,那发热带来的影响也将加大。发热和耗电可能会制约PRAM的进一步发展。

嵌入式存储器未来

嵌入式存储器具有大容量集成的优势,是SOC的重要组成部分,具有重要的创新性和实用性。何种嵌入式存储器将取得最终的成功,取决于多方面的因素:能否与标准CMOS工艺兼容,在不断增加复杂性的工艺步骤的基础上,实现大容量的片上集成,从而提高其性价比;能否随着工艺的发展缩小尺寸,解决超深亚微米工艺的延续性和扩展性问题,这是所有采用电容结构存储信息的存储器面对的共同挑战;能否满足片上其他高速逻辑的带宽需要,构成带宽均衡、稳定简洁的集成系统;准确的市场定位,保持量产。

总而言之每项技术的发展都有其机会与挑战。而无惧挑战勇于创新的企业最终将赢得市场。

-

soc

+关注

关注

38文章

4218浏览量

219271 -

fram

+关注

关注

2文章

283浏览量

79494 -

嵌入式存储器

+关注

关注

0文章

24浏览量

12436 -

MRAM

+关注

关注

1文章

236浏览量

31809

发布评论请先 登录

相关推荐

如何实现嵌入式ASIC和SoC的存储器设计?

嵌入式系统的组成部分是什么

使用新SRAM工艺实现嵌入式ASIC和SoC的存储器设计

嵌入式存储器内建自修复技术

电容是电路的基本组成部分之一,其主要品牌有哪些

讲讲多层PCB设计的重要组成部分之一过孔资料下载

关于SoC组成部分之一的嵌入式存储器,这些技术原理您都知道吗?

关于SoC组成部分之一的嵌入式存储器,这些技术原理您都知道吗?

评论