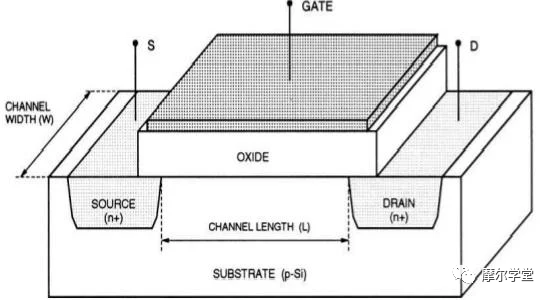

MOS管(金属氧化物半导体场效应晶体管)的泄漏电流是指在MOS管关断状态下,从源极或漏极到衬底之间仍然存在的微弱电流。这些泄漏电流可能对电路的性能和稳定性产生不利影响,因此需要深入了解其类型和产生原因。

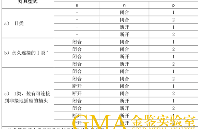

一、MOS管泄漏电流的类型

MOS管的泄漏电流主要包括以下几种类型:

- 栅极泄漏电流(I_g)

栅极泄漏电流是指通过栅极氧化层隧穿进入衬底的电流。当栅极上施加高电场时,电子可能通过Fowler-Nordheim隧道效应穿过栅极氧化层进入衬底,形成栅极泄漏电流。栅极氧化层的厚度和栅极电压的大小是影响栅极泄漏电流的主要因素。随着晶体管尺寸的不断缩小和电源电压的降低,栅极氧化层的厚度也在不断减小,导致栅极泄漏电流呈指数级增加。

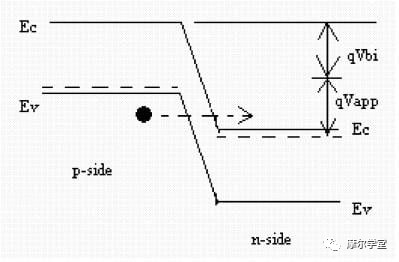

- 反向偏置pn结漏电流(I_rev)

MOS管的源极和漏极与衬底之间形成了pn结。当这些pn结处于反向偏置状态时,会产生反向偏置pn结漏电流。这种漏电流主要由耗尽区边缘的扩散和漂移电流以及耗尽区中产生的电子-空穴对组成。在一些重掺杂的pn区,还可能存在带间隧穿(BTBT)现象贡献的泄漏电流。反向偏置pn结漏电流的大小取决于掺杂浓度、结面积以及电场强度等因素。

- 亚阈值漏电流(I_sub)

亚阈值漏电流是指在栅源电压低于阈值电压(V_th)时,MOS管仍然存在的微弱电流。当栅源电压低于阈值电压时,器件不会立即关闭,而是进入“亚阈值区”。在亚阈值区,沟道中的电荷积累较少,但仍然存在少数载流子的扩散电流,导致亚阈值漏电流的产生。亚阈值漏电流与阈值电压成反比,随着温度的升高而增加。

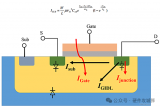

- 栅极感应漏极降低(GIDL)漏电流

GIDL漏电流是指栅极与漏极重叠区域下的强电场导致的漏极到阱的电流。当栅极与漏极之间的电场强度过高时,会导致深度耗尽区以及漏极和阱交界处耗尽层变薄,从而有效形成漏极到阱的电流。GIDL漏电流与栅极和漏极之间的电压差(V_GD)有关,通常NMOS的GIDL漏电流会比PMOS的大两个数量级。

- 热载流子注入漏电流

在MOS管工作过程中,载流子在通道中的散射和碰撞会产生热能,使部分载流子获得足够的能量越过势垒,形成热载流子注入漏电流。热载流子注入漏电流主要发生在衬底-氧化物界面附近的高电场区域。这种现象对电子的影响比对空穴的影响更大,因为电子具有较小的有效质量和较小的势垒高度。

二、MOS管泄漏电流的产生原因

MOS管泄漏电流的产生原因多种多样,主要包括以下几个方面:

- 栅极氧化层质量

栅极氧化层是MOS管的关键组成部分,其质量直接影响栅极泄漏电流的大小。栅极氧化层中存在缺陷、杂质或损伤时,会导致电子隧穿概率增加,从而增大栅极泄漏电流。因此,提高栅极氧化层的质量和完整性是降低栅极泄漏电流的关键。

- 掺杂浓度和结面积

反向偏置pn结漏电流的大小与掺杂浓度和结面积密切相关。重掺杂的pn结中,带间隧穿(BTBT)效应在反向偏置漏电流中占主导地位。此外,结面积的增加也会使反向偏置漏电流增大。因此,合理控制掺杂浓度和结面积是降低反向偏置pn结漏电流的有效方法。

- 阈值电压

亚阈值漏电流与阈值电压成反比,因此阈值电压的大小直接影响亚阈值漏电流的大小。随着CMOS技术的不断发展,现代CMOS器件中的阈值电压相对较低,导致亚阈值漏电流成为主要的泄漏电流分量之一。为了降低亚阈值漏电流,可以采取提高阈值电压、优化器件结构等方法。

- 电场强度

栅极与漏极之间的电场强度是影响GIDL漏电流的主要因素之一。当电场强度过高时,会导致深度耗尽区和漏极到阱的电流产生。因此,合理控制栅极与漏极之间的电压差以及优化器件结构是降低GIDL漏电流的有效方法。

- 温度效应

温度是影响MOS管泄漏电流的重要因素之一。温度升高会使杂质活化、表面态密度增加,进一步增加漏电流。此外,温度升高还会导致载流子的热激活和增加电子-空穴对的生成速率,从而促使漏电流增加。因此,合理控制工作温度是降低MOS管泄漏电流的有效手段之一。

- 制造工艺

MOS管的制造工艺对其泄漏电流也有重要影响。例如,制造过程中引入的缺陷、杂质或损伤都可能导致泄漏电流的增加。因此,提高制造工艺的质量控制、减少杂质与缺陷以及增强绝缘层的性能是降低MOS管泄漏电流的关键措施之一。

三、降低MOS管泄漏电流的策略与技术

为了降低MOS管的泄漏电流,业界已经开发并实施了多种策略和技术。以下是一些关键的策略和技术,旨在提高MOS管的性能和稳定性:

- 采用先进的栅极氧化层技术

栅极氧化层的质量对泄漏电流有着至关重要的影响。为了提高栅极氧化层的质量,可以采用先进的氧化工艺,如原子层沉积(ALD)或化学气相沉积(CVD)技术,来精确控制氧化层的厚度和均匀性。此外,使用高k介电材料(如HfO2、Al2O3等)替代传统的SiO2作为栅极氧化层,可以在保持相同电场强度的同时,增加氧化层的物理厚度,从而降低隧穿电流。

- 优化掺杂工艺

合理的掺杂浓度和分布对于控制泄漏电流至关重要。通过精确控制掺杂过程,可以减少杂质和缺陷的产生,从而降低由这些缺陷引起的泄漏电流。此外,采用梯度掺杂或变掺杂技术,可以在沟道中形成更平滑的势能分布,有助于减少亚阈值漏电流。

- 创新器件结构

通过创新器件结构,如三维鳍式场效应晶体管(FinFET)或纳米线FET,可以更有效地控制沟道中的载流子分布,从而降低泄漏电流。这些新型器件结构具有更小的沟道宽度和更高的栅极控制能力,使得在相同栅极电压下,沟道中的载流子浓度更低,从而减少了泄漏电流。

- 采用多栅极结构

多栅极结构,如双栅极或环绕栅极(GAA)FET,通过增加栅极与沟道的接触面积,提高了栅极对沟道载流子的控制能力。这种结构有助于降低亚阈值漏电流和栅极泄漏电流,同时提高了器件的开关速度和性能。

- 应用先进的封装技术

先进的封装技术,如三维集成(3D IC)和系统级封装(SiP),可以实现更紧密的器件连接和更小的封装尺寸。这些技术有助于降低由于封装过程中的热应力和机械应力引起的泄漏电流。此外,通过优化封装材料和工艺,还可以减少封装过程中的缺陷和污染,从而降低泄漏电流。

- 实施温度管理策略

温度是影响泄漏电流的重要因素之一。因此,实施有效的温度管理策略对于降低泄漏电流至关重要。这包括使用散热片、风扇或液冷等散热技术来降低器件的工作温度,以及采用热敏电阻或热电偶等温度传感器来监测和控制温度。此外,通过优化电路设计和材料选择,也可以降低器件在工作过程中产生的热量。

- 引入智能控制算法

随着人工智能和机器学习技术的不断发展,智能控制算法在半导体器件设计和制造中的应用越来越广泛。通过引入智能控制算法,可以根据实时数据和反馈来动态调整工艺参数和设备设置,从而优化器件的性能和降低泄漏电流。例如,使用机器学习算法来预测和优化掺杂浓度和分布,或使用神经网络来实时监测和控制温度。

四、未来展望

随着半导体技术的不断发展和创新,MOS管的泄漏电流控制技术也将不断演进和升级。未来,我们可以期待以下几个方面的进展:

- 新材料的应用 :随着新型半导体材料(如二维材料、拓扑绝缘体等)和新型栅极氧化层材料(如二维高k介电材料等)的研发和应用,有望为降低MOS管的泄漏电流提供新的解决方案。

- 更先进的制造工艺 :随着原子层沉积、电子束光刻等先进制造工艺的不断成熟和应用,将能够更精确地控制器件的尺寸和结构,从而降低泄漏电流并提高器件的性能。

- 智能化和自动化技术的融合 :随着智能化和自动化技术的不断发展,将能够更高效地监测和控制MOS管的制造过程,从而进一步提高器件的质量和稳定性,降低泄漏电流。

- 环保和可持续发展 :在未来的MOS管设计和制造中,将更加注重环保和可持续发展。例如,通过使用无毒或低毒的制造材料,以及采用节能和高效的制造工艺来降低对环境的影响。

五、结论

MOS管的泄漏电流是影响其性能和稳定性的重要因素之一。了解泄漏电流的类型和产生原因对于优化MOS管的设计和制造具有重要意义。通过提高栅极氧化层质量、合理控制掺杂浓度和结面积、优化器件结构、合理控制电场强度和温度以及提高制造工艺的质量控制等措施,可以有效地降低MOS管的泄漏电流。未来,随着CMOS技术的不断发展和创新,相信会有更多先进的泄漏电流控制技术涌现出来,为MOS管的设计和应用提供更加可靠和高效的解决方案。

-

MOS管

+关注

关注

108文章

2419浏览量

66875 -

晶体管

+关注

关注

77文章

9694浏览量

138231 -

泄漏电流

+关注

关注

0文章

22浏览量

6945

发布评论请先 登录

相关推荐

探究MOS晶体管中各种类型的泄漏电流的原因

MOS管的漏电流

基于TMS320F2812泄漏电流测试系统的设计

影响测量泄漏电流的因素及排除方法

浅析MOS 晶体管的核心概念

电容器漏电流产生原因有哪些

什么是泄漏电流试验?

MOS管泄漏电流的类型和产生原因

MOS管泄漏电流的类型和产生原因

评论