今天我们要介绍的时序基本概念是Timing arc,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分时序信息都以Timing arc呈现。如果两个pin之间在timing上存在因果关系,我们就把这种时序关系称为Timing arc,主要分为定义时序延迟,和定义时序检查两种。为啥叫它时序弧?因为时序图中经常用一条弧形线段来表示它。如下图所示:cell的timing arc定义在lib中,net之间没有timing arc, 它的delay则有RC参数计算而出。

时序延迟的Timing arc:有以下几种

Combinational Timing Arc

Edge Timing Arc

Preset and Clear Timing Arc

Three State Enable & Disable Timing Arc

时序检查的Timing arc:有以下几种

Setup Timing Arc

Hold Timing Arc

Recovery Timing Arc

Removal Timing Arc

Width Timing Arc

首先看Combinational Timing Arc,Combinational Timing Arc 是最基本的Timing Arc。Timing Arc 如果不特别指明的话,就是属于此类。如下图所示,定义了从特定输入到特定输出(A到Z)的延迟时间。Combinational Timing Arc 的Sense有三种,分别是inverting(或 negative unate),non-inverting(或 positive unate)以及non-unate。当Timing Arc 相关之特定输出(下图Z)信号变化方向和特定输入(下图A)信号变化方向相反(如输入由0变1,输出由1变0),则此Timing Arc 为inverting sense。反之,输出输入信号变化方向一致的话,则此Timing Arc 为non-inverting sense。当特定输出无法由特定输入单独决定时,此Timing Arc 为non-unate。

其它的Timing Arc 说明如下。

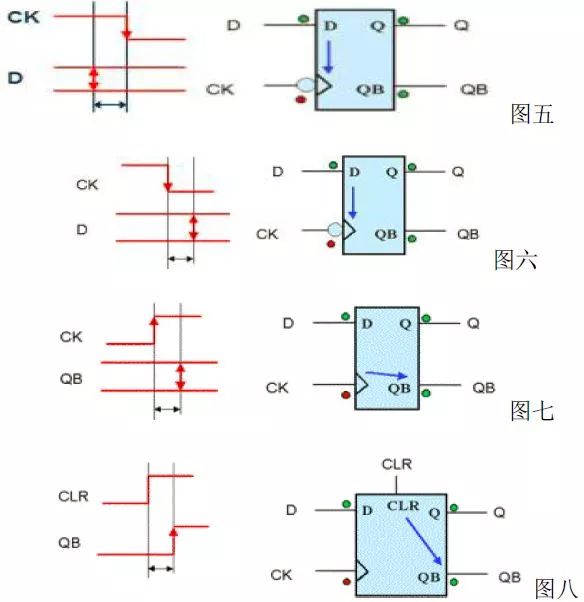

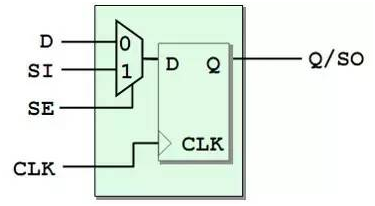

Setup Timing Arc:定义时序组件(Sequential Cell,如Flip-Flop、Latch 等)所需的Setup Time,依据Clock上升或下降分为2类(图五)。Hold Timing Arc:定义时序组件所需的 Hold Time,依据Clock 上升或下降分为2类(图六)。Edge Timing Arc:定义时序组件Clock Active Edge 到数据输出的延迟时间,依据Clock上升或下降分为2类(图七)。Preset and Clear Timing Arc:定义时序组件清除信号(Preset或Clear发生后,数据被清除的速度,依据清除信号上升或下降及是Preset或Clear分为4类(图八)。这个Timing Arc 通常会被取消掉,因为它会造成信号路径产生回路,这对STA而言是不允许的。Recovery Timing Arc:定义时序组件Clock Active Edge 之前,清除信号不准启动的时间,依据Clock上升或下降分为2类(图九)。Removal Timing Arc:定义序向组件Clock Active Edge 之后,清除信号不准启动的时间,依据Clock上升或下降分为2类(图十)。Three State Enable & Disable Timing Arc:定义 Tri-State 组件致能信号(Enable)到输出的延迟时间,依据Enable或Disable分为2类。(图十一)Width Timing Arc:定义信号需维持稳定的最短时间,依据信号维持在0或1的位准分为2类。(图十二)

-

时序

+关注

关注

5文章

411浏览量

38999 -

时序弧

+关注

关注

0文章

1浏览量

1454

原文标题:时序分析基本概念介绍——Timing Arc

文章出处:【微信号:IC_Physical_Design,微信公众号:数字后端IC芯片设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【时序约束资料包】培训课程Timing VIVADO

时序分析和时序约束的基本概念详细说明

FPGA设计中时序分析的基本概念

介绍时序分析基本概念MMMC

时序分析基本概念介绍—花一样的“模式”

详细介绍时序基本概念Timing arc

详细介绍时序基本概念Timing arc

评论