随着人工智能(AI)的不断发展,它已经从早期的人工特征工程进化到现在可以从海量数据中学习,机器视觉、语音识别以及自然语言处理等领域都取得了重大突破。CNN(Convolutional Neural Network,卷积神经网络)在人工智能领域受到越来越多的青睐,它是深度学习技术中极具代表性的网络结构之一,尤其在图像处理领域取得了很大的成功。随着网络变得越来越大、越来越复杂,我们需要大量的计算资源来对其进行训练,因此人们纷纷将注意力转向FPGA(Field Programmable Gate Array,现场可编程门阵列)器件,FPGA不仅具有软件的可编程性和灵活性,同时又有ASIC高吞吐和低延迟的特性,而且由于具有丰富的I/O接口,FPGA还非常适合用作协议和接口转换的芯片。

近日KORTIQ公司推出了一款Xilinx FPGA的CNN加速器IP——AIScale,它能够利用实现训练好的CNN网络,比如行业标准的ResNet、AlexNet、Tiny Yolo和VGG-16等,并将它们进行压缩输出二进制描述文件,可以部署到Xilinx全系列可编程逻辑器件上。Zynq SoC和Zynq UltraScale+ MPSoC器件PS可以提供数据给AIScale CNN加速器(PL),经过分类处理将输出数据给PS。压缩后的CNN网络占用资源相对小很多,可以部署在片上存储器中,可以更快更灵活的切换CNN网络。

图1:AIScale在计算机视觉应用案例示意图

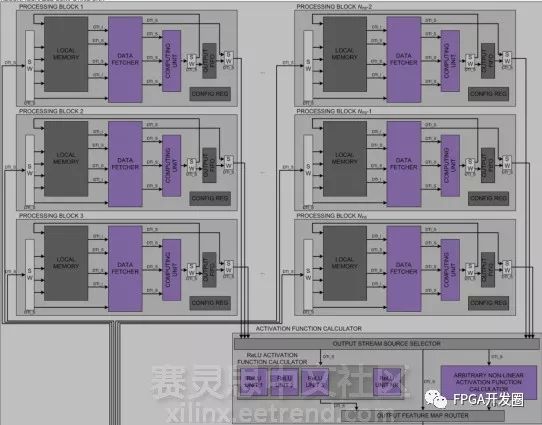

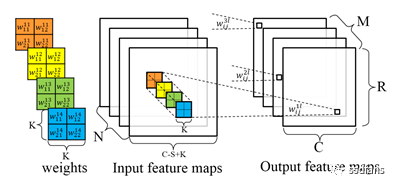

AIScale加速器的核心是AIScale RCC(Re-configurable Compute Core),用户根据需求可以灵活自定义AIScale RCC模块的数量,AIScale RCC支持卷积预处理、池化/采样、加权和全连接层等处理。资源更丰富的Zynq SoC和UltraScale+ MPSoC可以集成更多的AIScale RCC模块,这会给AIScale加速器带来更大的性能提升。当然也可以根据成本、系统功耗、性能需求集成一定的AIScale RCC模块,选择合适的Xilinx FPGA器件。

图2:多个 AIScale RCC模块级联连接

KORTIQ公司目前专注于嵌入式和计算机视觉领域,设计工业4.0和物联网(IoT)等,未来将会为AIScale CNN加速器提供更多更先进的特性,比如图像分类、物体识别和追踪、人脸和语音识别、自然语言处理等,将先进的人工智能网络应用到自动化生产、控制等场景中,提高相关行业的生产力为用户带来更好的服务。

-

FPGA

+关注

关注

1630文章

21796浏览量

605771 -

Xilinx

+关注

关注

71文章

2171浏览量

122066 -

IP

+关注

关注

5文章

1716浏览量

149916 -

cnn

+关注

关注

3文章

353浏览量

22317

原文标题:介绍一款基于FPGA的CNN硬件加速器IP

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数据中心加速器就看GRVI Phalanx FPGA加速器

机器学习实战:GNN加速器的FPGA解决方案

一款低端14 MHz加速器Spitfire 500

使用AMD-Xilinx FPGA设计一个AI加速器通道

高级语言(HLL)标准扩展大大简化基于FPGA加速器的应用程序的开发

基于FPGA的通用CNN加速设计

优化基于FPGA的深度卷积神经网络的加速器设计

基于Xilinx 28nmFPGA的Dragen加速器板卡用于基因组分析算法的加速的解析

一款Xilinx FPGA的CNN加速器IP—AIScale

基于Xilinx FPGA的Memcached硬件加速器的介绍

Kortiq小巧高效的CNN加速器,支持所有类型

Achronix和BittWare推出采用FPGA芯片的加速卡

如何采用带专用CNN加速器的AI微控制器实现CNN的硬件转换

基于FPGA的深度学习CNN加速器设计方案

KORTIQ公司推出了一款Xilinx FPGA的CNN加速器IP——AIScale

KORTIQ公司推出了一款Xilinx FPGA的CNN加速器IP——AIScale

评论