原创 :圆圆De圆 半导体全解

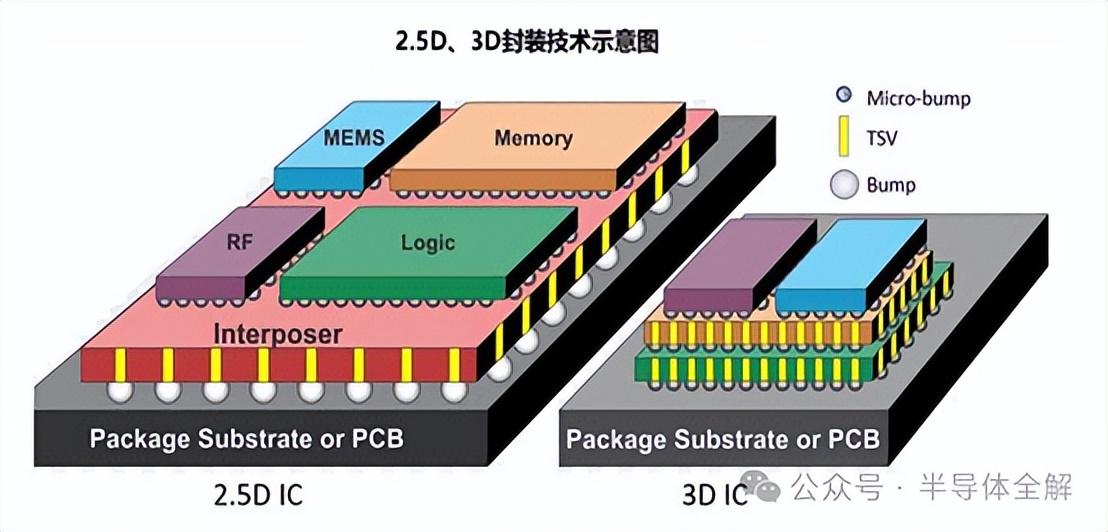

封装技术是半导体工业最为主要的工艺之一,按照封装的外形,可将封装分为插孔式封装、表面贴片式封装、BGA 封装、芯片尺寸封装(CSP),单芯片模块封装(SCM,印制电路板(PCB)上的布线与集成路(IC)板焊盘之间的缝隙匹配),多芯片模块封装(MCM, 可集成异质芯片),晶圆级封装(WLP,包括扇出型晶圆级封装(FOWLP)、微型表面贴装元器件(microSMD)等),三维封装(微凸块互连封装、TSV 互连封装等),系统封装(SIP),芯片系统(SOC)。

3D封装的形式主要分为填埋型(将器件填埋于多层布线内或填埋在基板内部)、有源基板型(硅圆片集成:先把元器件和晶圆基板集成化,形成有源基板;接着布置多层互连线,并在顶层装配其它芯片或元器件)和叠层型(硅片与硅片堆叠、芯片与硅片堆叠和芯片与芯片堆叠)三类。

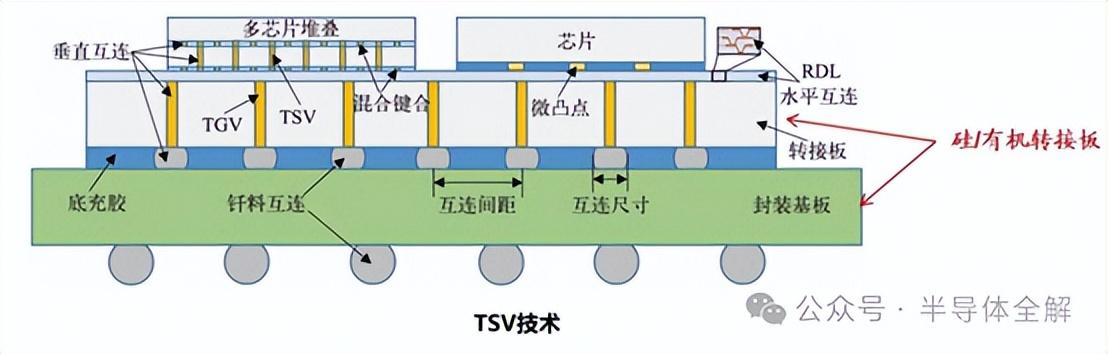

3D互连的方式包括引线键合(wire bonding,WB)、倒装芯片(flip chip, FC)、硅通孔(through silicon via, TSV)、薄膜导线(film conductor)等。TSV实现了芯片间的垂直互连,由于垂直互连线的距离最短、强度较高,更易实现小型化、高密度、高性能、多功能化异质结构的封装,与此同时还可互连异种材质的芯片;目前采用TSV工艺微电子制造技术有两种:三维电路封装(3D IC integration)和三维硅封装(3D Si integration)。两种形式的不同在于:(1) 三维电路封装需要把芯片电极制备成为凸点,凸点间进行互连(通过粘结、熔合、焊接等手段键合),而三维硅封装是芯片与芯片的直接互连(氧化物之间的键合以及Cu-Cu键合)。(2) 三维电路集成技术可以通过晶圆片之间键合实现(三维电路封装、三维硅封装),芯片-芯片键合和芯片-晶圆片键合仅能采用三维电路封装。(3) 三维电路封装工艺集成的芯片之间存在空隙,需填充介质材料以调整系统的热导率、热膨胀系数保证系统的机械、电性能的稳定性;三维硅封装工艺集成的芯片之间没有空隙,且芯片的功耗、体积、重量较小,电性能优良。

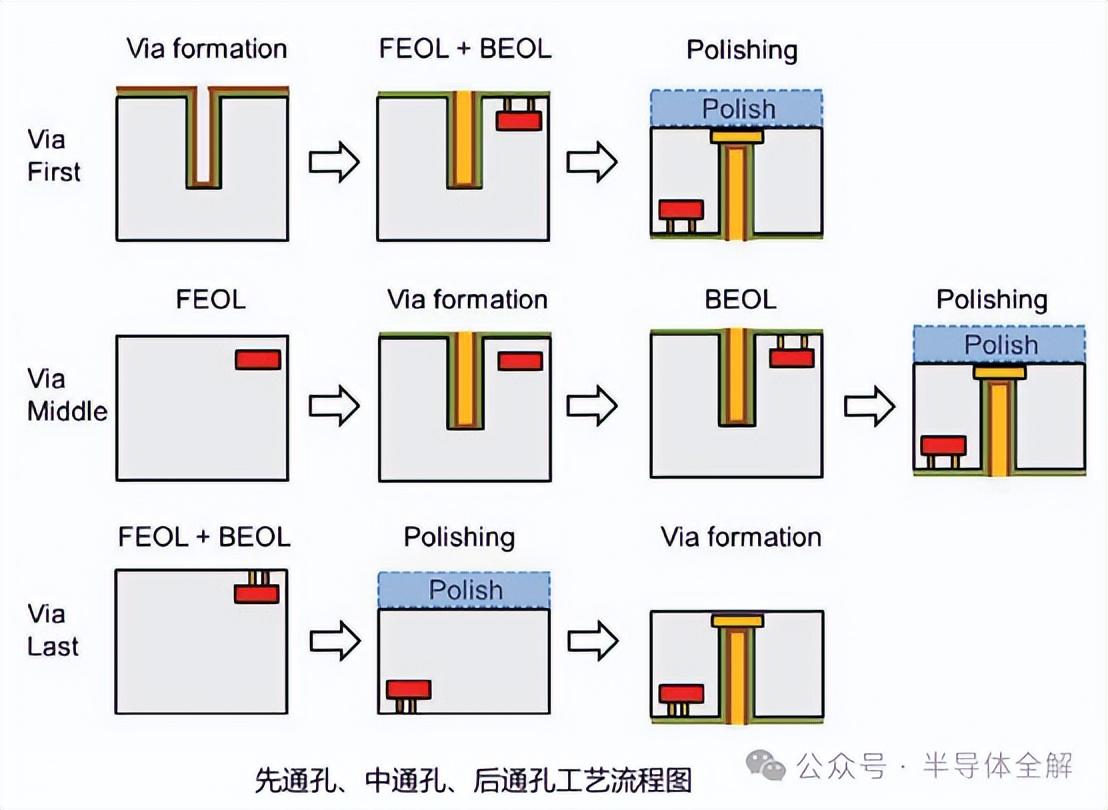

TSV工艺能够构建穿过衬底的垂直信号通路,并连接衬底顶部及底部的RDL形成三维的导体通路,因此TSV工艺是构建三维无源器件结构的重要基石之一。根据与前道工序(front end of line,FEOL)及后道工序(back end of line,BEOL)之间的先后顺序,TSV工艺可分为三种主流的制造流程,分别是先通孔(ViaFirst),中通孔(Via Middle)及后通孔(Via Last)工艺流程,如图所示。

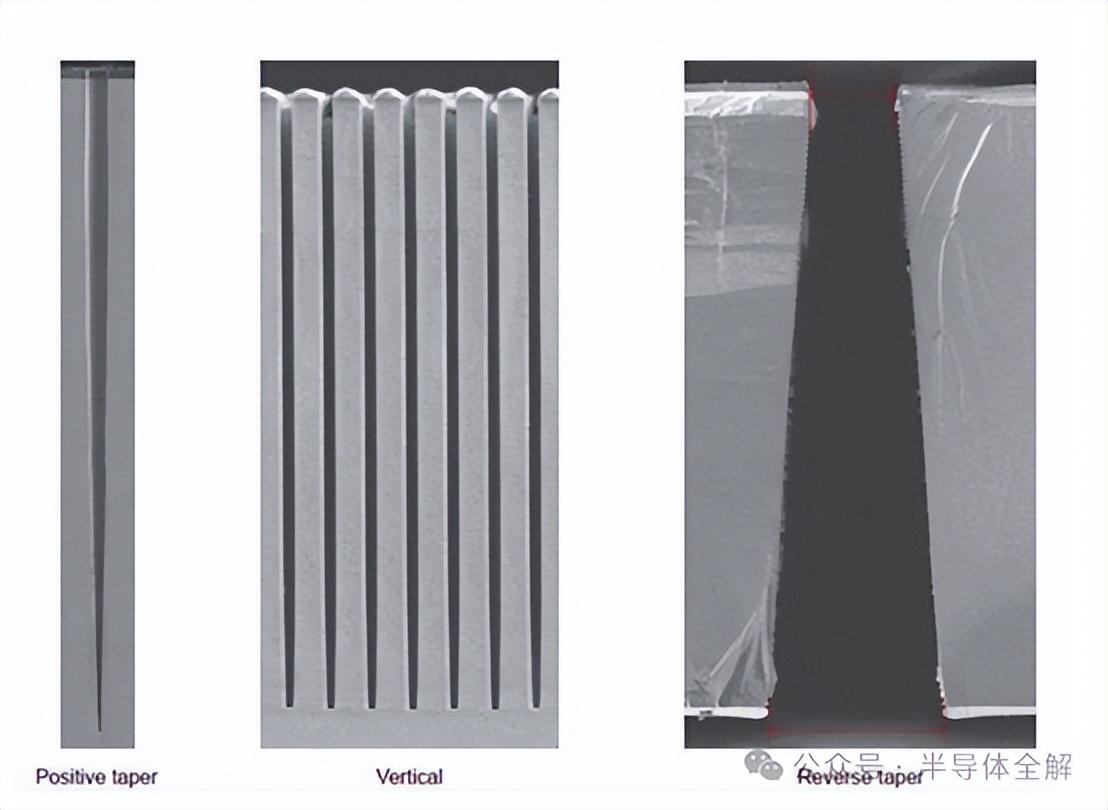

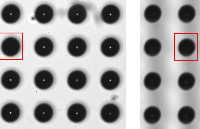

一、通孔刻蚀工艺通孔刻蚀工艺是制造TSV结构的关键,选择合适的刻蚀工艺能有效提升TSV的机械强度与电学特性,并进一步关系到TSV三维器件的整体可靠性。目前主流的TSV通孔刻蚀工艺主要有四种:分别是深反应离子刻蚀法(DeepReactive Ion Etching, DRIE)、湿法刻蚀法、光辅助电化学刻蚀法(photo-assisted electrochemical etching, PAECE)与激光钻孔法。(1) 深反应离子刻蚀法(DeepReactive Ion Etching, DRIE)深反应离子刻蚀也即DRIE工艺是最为常用的TSV刻蚀工艺,其主要被用于实现高深宽比的TSV通孔结构。传统的等离子体刻蚀工艺一般仅能实现数微米的刻蚀深度,且刻蚀速率低,缺乏刻蚀掩模选择性。Bosch公司在此基础上进行了相应的工艺改进,通过采用SF6作为反应气体并在刻蚀过程中释放C4F8气体来作为侧壁的钝化保护,经改进后的DRIE工艺适于刻蚀高深宽比通孔,因此按其发明者名称也被称为Bosch 工艺。下图为通过DRIE工艺刻蚀形成的高深宽比通孔的照片。

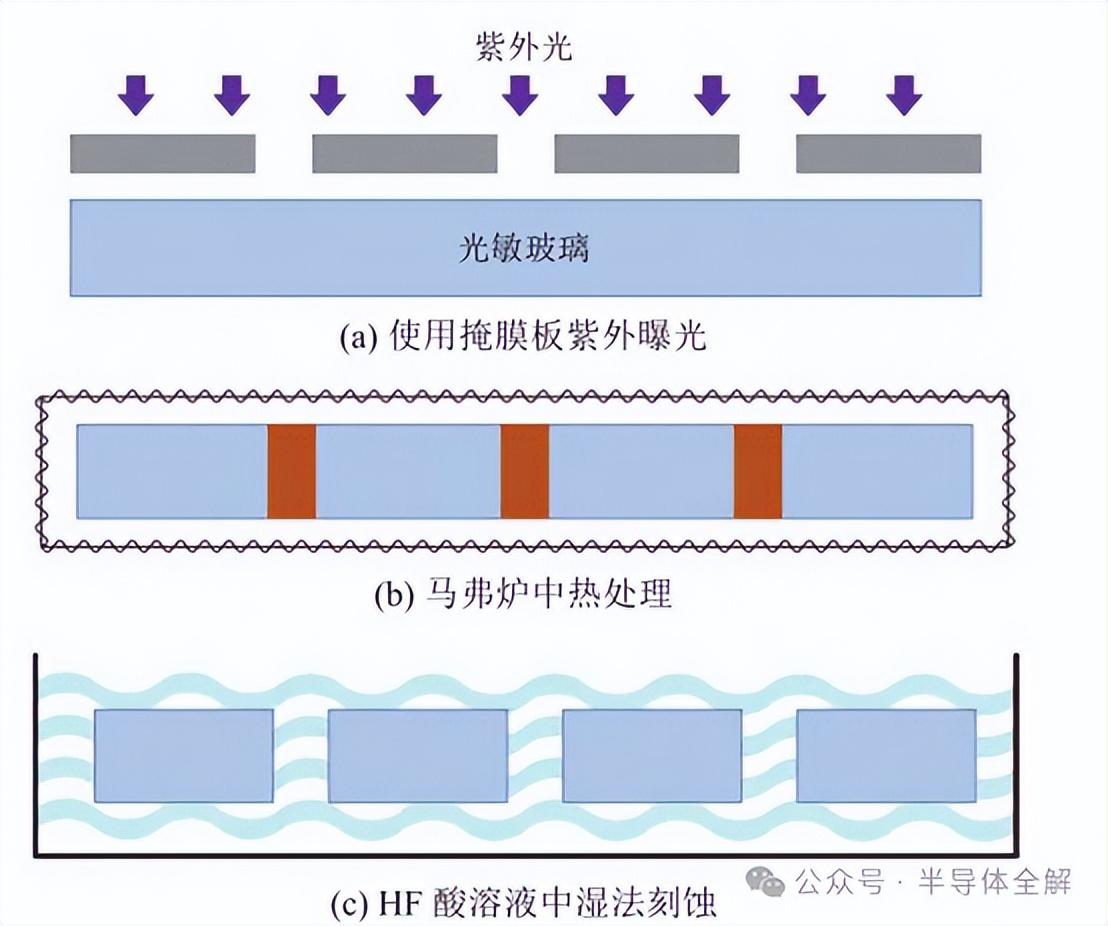

DRIE工艺虽然因其良好的可控性被广泛应用于TSV工艺流程中,但其缺点是侧壁平整度较差,同时会形成扇贝形状的褶皱缺陷,且该缺陷在刻蚀高深宽比通孔时更为显著。(2)湿法刻蚀湿法刻蚀采用掩模版与化学腐蚀结合的方式实现通孔的刻蚀。最常选用的腐蚀溶液是KOH,其能腐蚀硅衬底上不受掩模版保护的位置,进而形成所需的通孔结构。湿法刻蚀是最早被研发出的通孔刻蚀工艺,由于其工艺步骤与所需设备均较为简单,使其适用于低成本下TSV的大批量生产。但其化学腐蚀的机制,决定了该方法所形成的通孔会受到硅片的晶向影响,使刻蚀出的通孔非垂直而是呈现明显的顶部宽底部窄的现象,这一缺陷限制了湿法刻蚀在TSV制造中的应用。(3)光辅助电化学刻蚀法(photo-assisted electrochemical etching, PAECE)光辅助电化学刻蚀法PAECE,其基本原理是利用紫外光照射加速电子-空穴对的产生,以此加速电化学刻蚀过程。与广泛使用的DRIE工艺相比,PAECE工艺更适用于刻蚀大于100:1的超大深宽比通孔结构,但其缺点是刻蚀深度的可控性弱于DRIE,其技术可能需要进一步的研究与工艺改进。

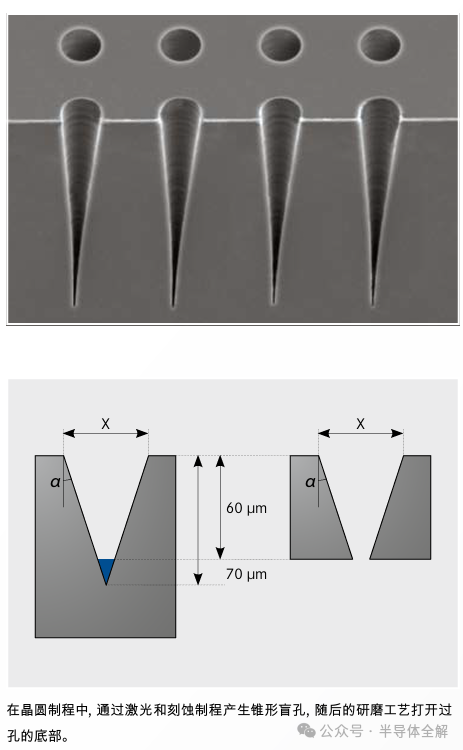

(4)激光钻孔与前述三种方法不同,激光钻孔法是纯粹的物理方法,主要通过高能激光照射使指定区域的衬底材料熔化并蒸发,以物理方式实现TSV的通孔构建。利用激光钻孔法形成的通孔深宽比高,且侧壁基本垂直,但由于激光钻孔实质上是采用了局部加热的方式来形成通孔,TSV的孔壁会受到热损伤的负面影响而降低可靠性。

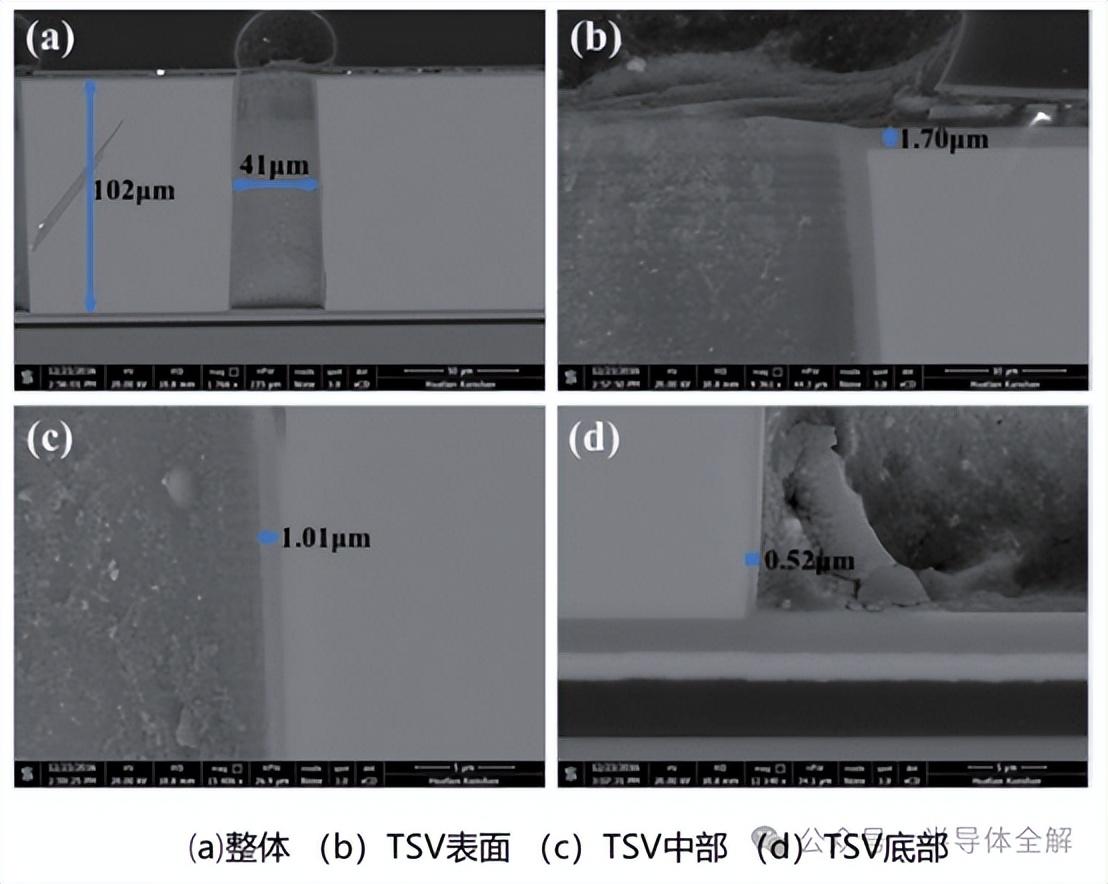

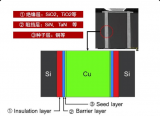

二、衬垫层淀积工艺制造TSV另一项关键关键技术是衬垫层淀积工艺。衬垫层淀积工艺在通孔刻蚀后执行,淀积的衬垫层一般为SiO2等氧化物,衬垫层位于TSV的内部导体与衬底之间,主要起到隔离直流电流泄露的作用。除淀积氧化物外,还需为了下一工序的导体填充淀积阻挡层与种子层。所制造的衬垫层需满足以下两点基本要求:第一,绝缘层所具有的击穿电压应满足TSV的实际工作需求;第二,所淀积的各层一致性强,且相互间具有良好的附着力。下图为采用等离子增强型化学气相淀积法(Plasma Enhanced Chemical Vapor Deposition, PECVD)淀积衬垫层的照片。

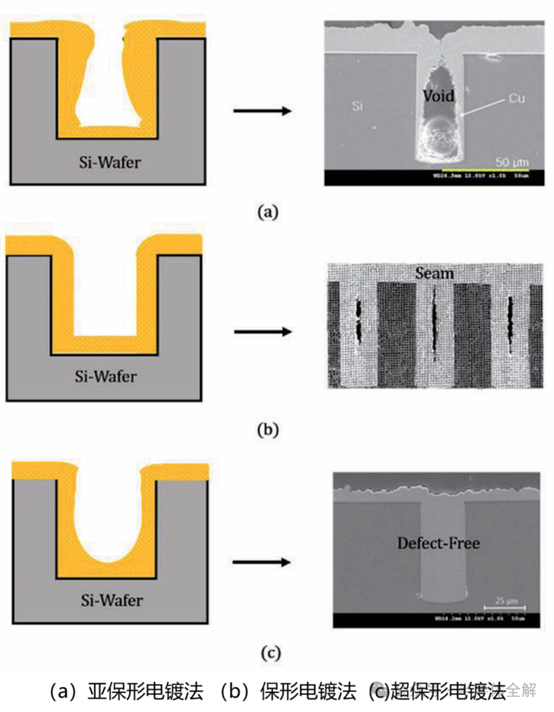

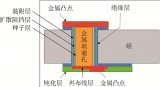

对于选择的TSV制造流程不同,沉积工艺也需相应调整。对于前通孔工艺流程,可采用高温沉积工艺以提高氧化层的质量。典型的高温沉积可采用基于四乙基正硅酸盐(TEOS)结合热氧化工艺的方式来形成高度一致的高质量SiO2绝缘层。而对于中通孔及后通孔工艺流程,由于淀积时BEOL工序已完成,需采用低温方法以保证与BEOL材料的兼容性。在该种条件下,淀积温度应被限定在450°内,包括采用PECVD 淀积SiO2或SiNx作为绝缘层。另一种常用方式是采用原子层沉积技术(Atomic Layer Deposition, ALD)来沉积Al2O3以获得更为致密的绝缘层。三、金属填充工艺TSV的填充工艺紧接着衬垫层淀积工艺之后进行,是决定TSV质量的另一项关键技术。可填充的材料依据采用的工艺不同,包括掺杂多晶硅、钨、碳纳米管等,但最主流的仍是电镀铜,这是因为其工艺成熟,且电导率与热导率均相对较高。按其在通孔内电镀速率的分布差异,可将其主要分为亚保形(subconformal)、保形(conformal)、超保形(superconformal)与自底向上(Bottom-up)电镀法等,如图所示。

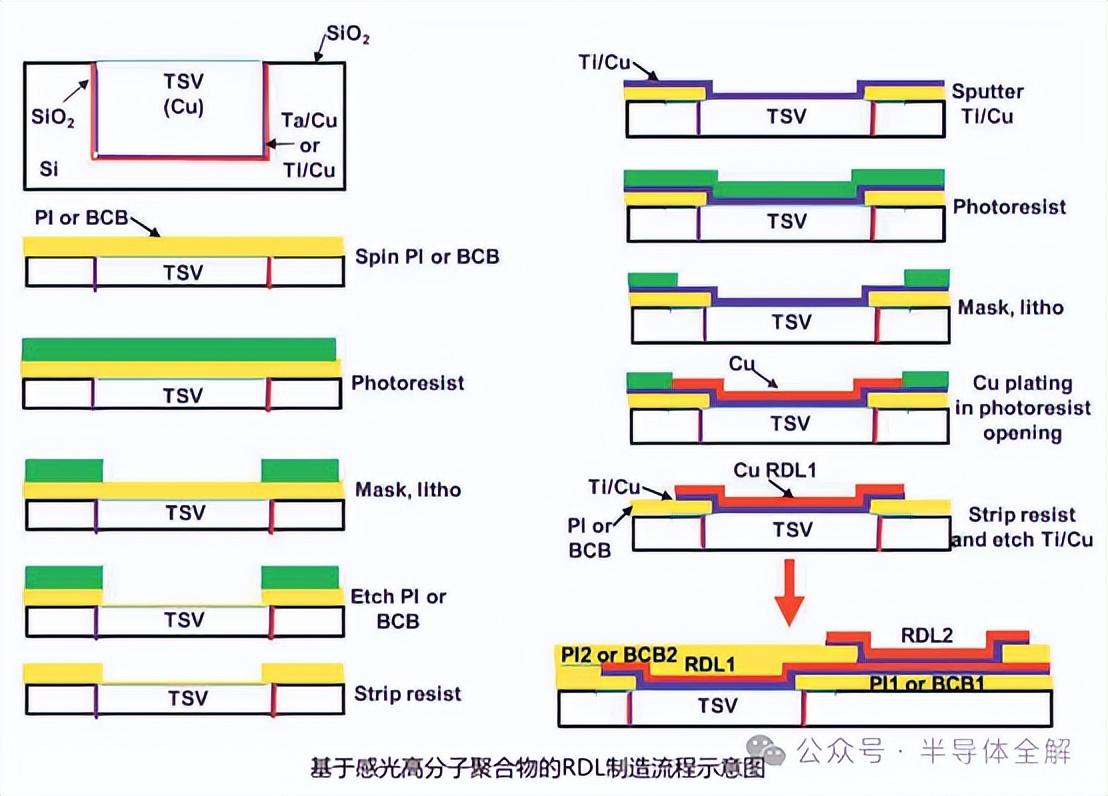

亚保形电镀法主要应用于TSV研究早期,如图(a)所示,由于电解所提供的Cu离子集中于顶部,而下方补充不足,进而造成通孔顶部的电镀速率要高于顶部以下,因此通孔在被完全填充前顶部会提前闭合,进而在内部形成较大的空洞。保形电镀法的示意图与照片如图(b)所示,通过确保Cu离子的均匀补充而使得通孔内各位置的电镀速率基本一致,因此其内部仅会留下一条接缝,空洞体积远小于亚保形电镀法,因而被广泛应用。而为了进一步实现无空洞的填充效果,超保形电镀法被提出以优化保形电镀法,如图(c)所示,通过控制Cu离子供应使得底部的填充速率略高于其它位置,从而优化填充速率由下至上的阶梯度来完全消除保形电镀法所留下的接缝,以实现完全无空洞的金属铜填充。自底向上电镀法可被认为是超保形法中的一种特殊情况,此时除底部外的电镀速率均被抑制为零,仅从底部逐渐向上电镀至顶部,该方法除具有保形电镀法的无空洞优势外,还能有效的减少整体电镀用时,因而在近年来得到了广泛的研究。四、RDL工艺技术RDL工艺是三维封装工艺中一项必不可少的基础技术,可通过该工艺在衬底的正反两面制造金属互连,以实现端口的重新分配或封装间互连的目的,因此RDL工艺被广泛应用于扇入-扇出或2.5D/3D封装体系内。在构建三维器件的过程中,RDL工艺通常被应用于互连TSV以实现多种多样的三维器件结构。目前主流的RDL工艺主要有两种,第一种基于感光高分子聚合物,并结合电镀铜与刻蚀工艺实现;另一种则采用Cu大马士革工艺结合PECVD与化学机械抛光(ChemicalMechanical Polishing, CMP)工艺实现。下面将分别介绍这两种RDL的主流工艺路径。

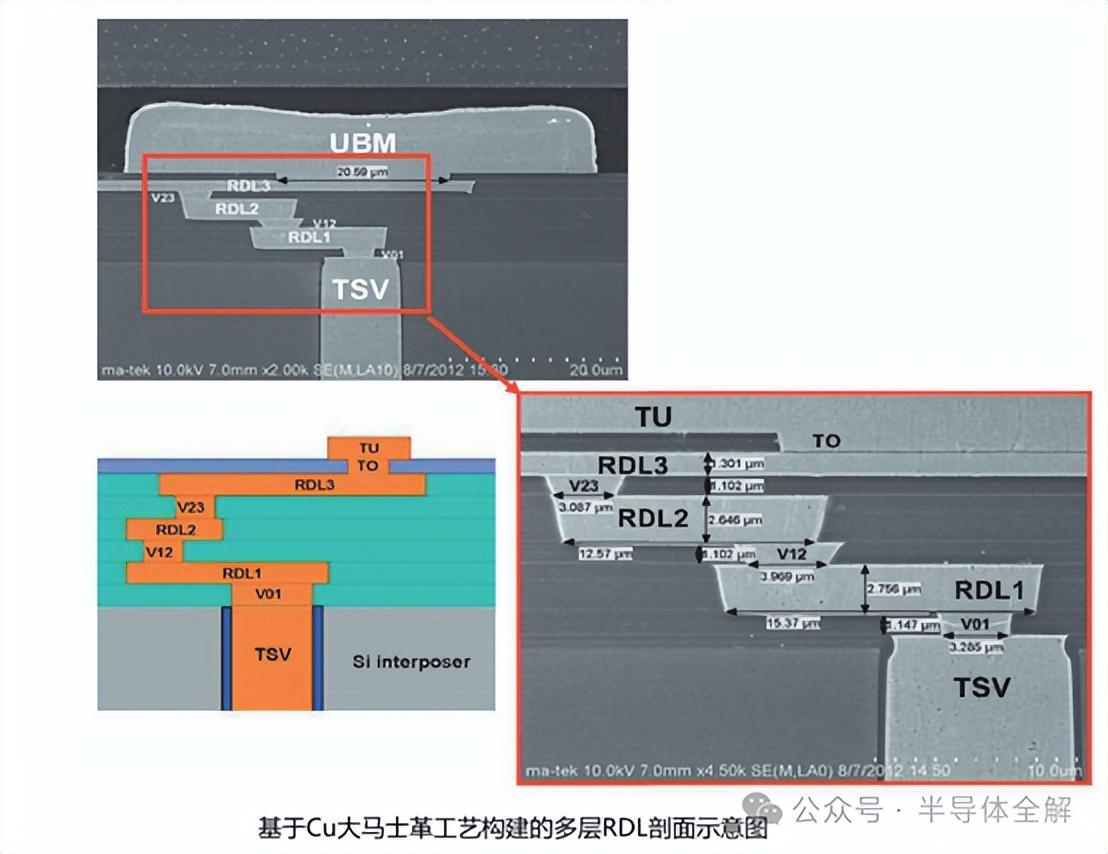

基于感光高分子聚合物的RDL工艺如上图所示。首先,通过旋转在晶圆表面涂覆一层PI或BCB胶,加热固化后使用光刻工艺在所需位置进行开孔,之后进行刻蚀。接着,在去除光刻胶后通过物理气相沉积工艺(Physical Vapor Deposition,PVD)在晶圆上溅射Ti与Cu,分别作为阻挡层与种子层。下一步,结合光刻与电镀Cu工艺在暴露出的Ti/Cu层上制造第一层RDL,然后去除掉光刻胶并刻蚀掉多余的Ti与 Cu。重复上述步骤即可形成多层的RDL结构。该方法目前在工业界中运用更为广泛。另一种制造RDL的方法则主要基于Cu大马士革工艺,并结合了PECVD与CMP工艺。该方法与基于感光高分子聚合物的RDL工艺的思路不同之处在于:在制造每一层的第一步时,先采用PECVD淀积SiO2或Si3N4作为绝缘层,之后利用光刻与反应离子刻蚀在绝缘层上形成窗口,并分别溅射Ti/Cu的阻挡/种子层与导体铜,之后采用CMP工艺将导体层减薄至所需厚度,即形成了一层RDL或通孔层。下图为基于Cu大马士革工艺构建的多层RDL剖面示意图与照片,可以观察到TSV首先与通孔层V01连接,之后从下至上按RDL1、通孔层V12、RDL2的顺序依次叠加。每一层RDL或通孔层均按照上述方法被依次制造。由于该RDL流程需要采用CMP工艺, 导致其制造成本高于基于感光高分子聚合物的RDL工艺流程,因此其应用广泛度相对较低。

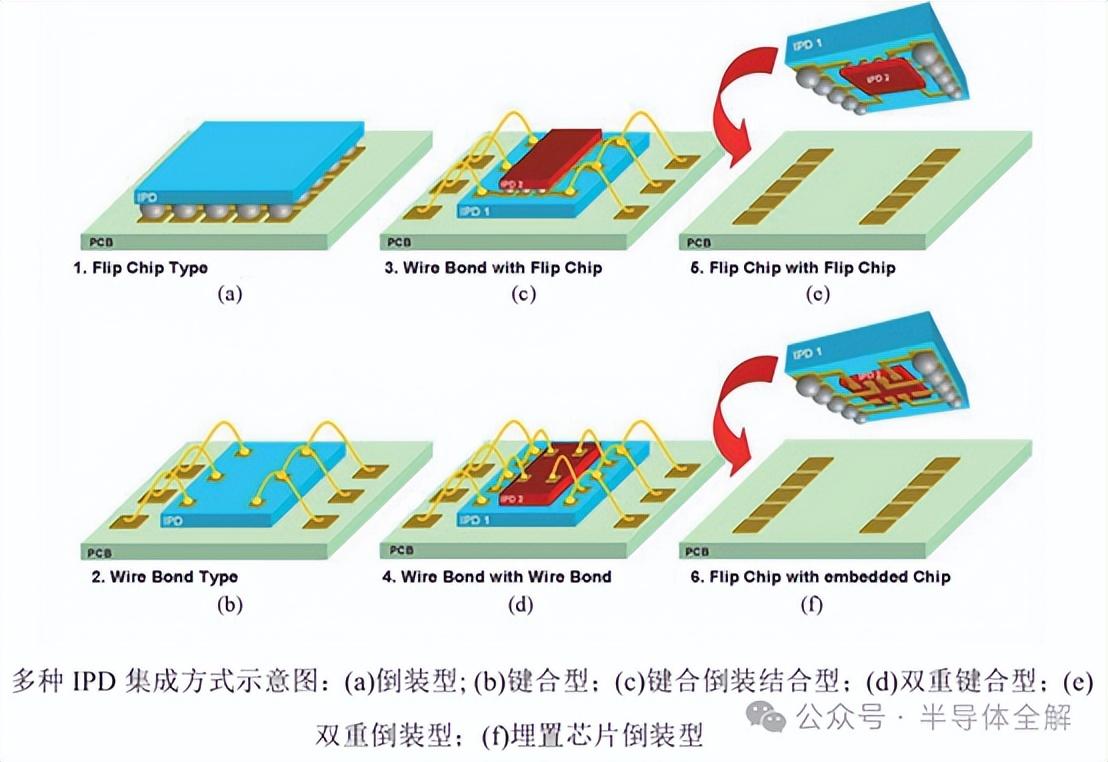

五、IPD 工艺技术对于三维器件的制造,除了直接片上集成于MMIC之外,IPD工艺提供了另一种更为灵活的技术路径。集成无源器件也即IPD工艺,是通过将包括片上型电感器、电容器、电阻器、巴伦转换器等无源器件的任意组合集成于单独的衬底上,以形成可按设计需求灵活调用的转接板形式的无源器件库。由于在IPD工艺中,无源器件被制造并直接集成于转接板上,因此其工艺流程相较IC片上集成更为简单,成本较低,并可作为无源器件库被提前量产。对于TSV三维无源器件制造而言,IPD更是能有效抵消包括TSV与RDL在内的三维封装工艺的成本负担。除成本优势外,IPD的另一优点是灵活度较高。IPD的灵活性之一体现在集成方式较为多样,如下图所示。除了如图(a)所示通过倒装焊工艺或图(b)所示通过键合工艺将IPD直接集成于封装基板的两种基础方式外,还可如图(c)-(e)所示在一层IPD上集成另一层IPD,以实现更为广泛的无源器件组合。同时,可如图(f)所示,进一步将IPD作为转接板,在上方直接埋置集成芯片,以直接构建高密度的封装系统。

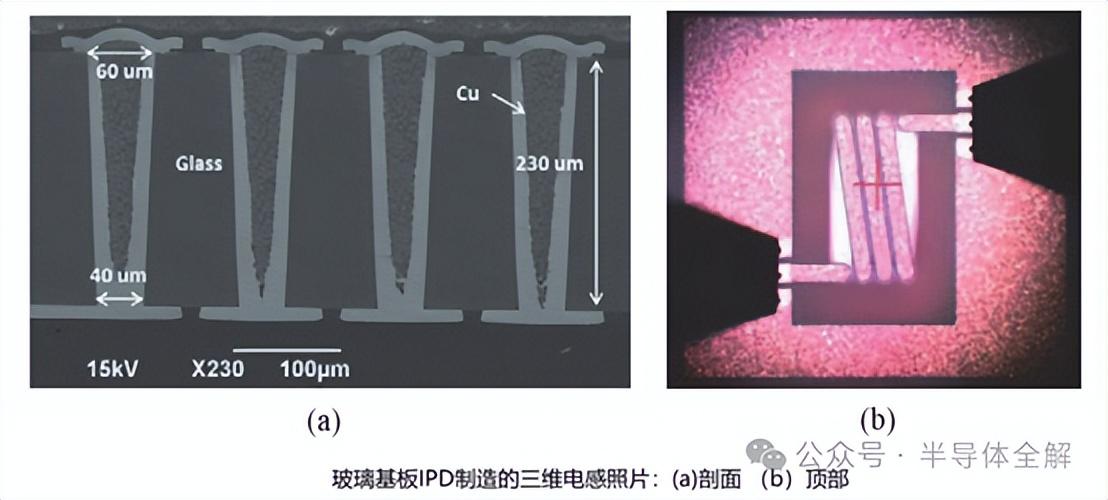

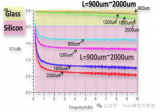

当采用IPD构建三维无源器件时,同样可采用TSV工艺与RDL工艺,其工艺流程与前述的片上集成加工方式基本一致,不再重复赘述;区别是由于集成的对象由芯片改为了转接板,因此无需额外考虑采用的三维封装工艺对有源区与互连层的影响。这进一步引申出了IPD的另一项关键灵活性:可根据无源器件设计需求灵活地选择多种多样的衬底材料。IPD可选用的衬底材料不仅是Si、GaN等常用半导体衬底材料,还包括Al2O3陶瓷、低温/高温共烧陶瓷、玻璃基板等,该特点有效扩展了IPD所集成无源器件的设计灵活度。例如,IPD集成的三维无源电感器结构,可采用玻璃基板来有效提高电感器的性能。与TSV这一概念相对的,在玻璃基板上制造的通孔也被称为玻璃通孔(throughglassvia,TGV)。基于IPD与TGV工艺制造的三维电感器照片如下图所示,由于玻璃衬底的电阻率远高于Si等常规半导体材料,因此TGV三维电感器具有更优异的绝缘特性,在高频下衬底寄生效应所造成的插入损耗要远小于常规TSV三维电感器。

另一方面,还可在玻璃衬底IPD上通过薄膜淀积工艺制造金属-绝缘体-金属(Metal-Insulator-Metal, MIM)电容器,和TGV三维电感器互连以形成三维无源滤波器结构。因此,IPD工艺用于开发新型三维无源器件具有广阔的应用潜力。

参考文献:

(1)孙云娜 硅通孔互连_TSV_封装体的热机械特性研究[D].

(2)熊伟 基于硅通孔的三维微波无源器件设计研究[D].

(3)广发证券 半导体设备行业系列研究:玻璃基板从零到一,TGV为关键工艺[C].

(4)东方财富证券 电子设备行业专题研究:Chiplet与先进封装共塑后摩尔时代半导体产业链新格局[C].

(5)LPKF Vitrion® 5000[C].

【近期会议】

10月30-31日,由宽禁带半导体国家工程研究中心主办的“化合物半导体先进技术及应用大会”将首次与大家在江苏·常州相见,邀您齐聚常州新城希尔顿酒店,解耦产业链市场布局!

11月28-29日,“第二届半导体先进封测产业技术创新大会”将再次与各位相见于厦门,秉承“延续去年,创新今年”的思想,仍将由云天半导体与厦门大学联合主办,雅时国际商讯承办,邀您齐聚厦门·海沧融信华邑酒店共探行业发展!

审核编辑 黄宇

-

半导体

+关注

关注

339文章

31438浏览量

267423 -

TSV

+关注

关注

4文章

139浏览量

82815 -

硅通孔

+关注

关注

2文章

31浏览量

12154 -

3D封装

+关注

关注

9文章

150浏览量

28397

发布评论请先 登录

一文了解硅通孔(TSV)及玻璃通孔(TGV)技术

一文了解硅通孔(TSV)及玻璃通孔(TGV)技术

评论