随着电子组件功能提升,各种电子产品不断朝向高速化方向发展,然而高性能化、多功能化、可携带化的结果,各式各样的EMC(Electro Magnetic Compatibility)问题,却成为设计者挥之不去的梦魇。目前EMI(ElectroMagnetic Interference)噪讯对策,大多仰赖设计者长年累积的经验,或是利用仿真分析软件针对框体结构、电子组件,配合国内外要求条件与规范进行分析,换句话说电子产品到了最后评鉴测试阶段,才发现、对策EMI问题,事后反复的检讨、再试作与对策组件的追加,经常变成设计开发时程漫无节制延长,测试费用膨胀的主要原因。

EMI主要发生源之一亦即印刷电路板(PrintedCircuit Board,以下简称为PCB)的设计,自古以来一直受到设计者高度重视,尤其是PCB Layout阶段,若能够将EMI问题列入考虑,通常都可以有效事先抑制噪讯的发生,有鉴于此本文要探讨如何在PCB的Layout阶段,充分应用改善技巧抑制EMI噪讯的强度。

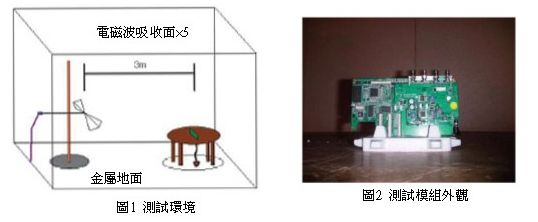

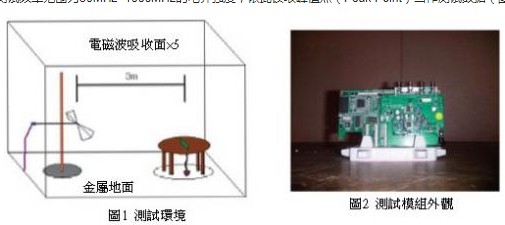

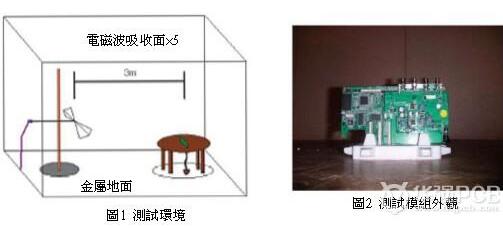

测试条件 如图1所示测试场地为室内3m半电波暗室,预定测试频率范围为30MHz~1000MHz的电界强度,依此读取峰值点(Peak Point)当作测试数据(图2)。

图3是被测基板A的外观,该基板为影像处理系统用电路主机板,动作频率为27MHz与54MHz,电路基板内建CPU、Sub CPU、FRASH,以及SDRAM×5、影像数据/数字转换处理单元、影像输出入单元,此外被测基板符合「VCCI规范等级B」的要求,测试上使用相同的电源基板(Board)与变压器(Adapter)。

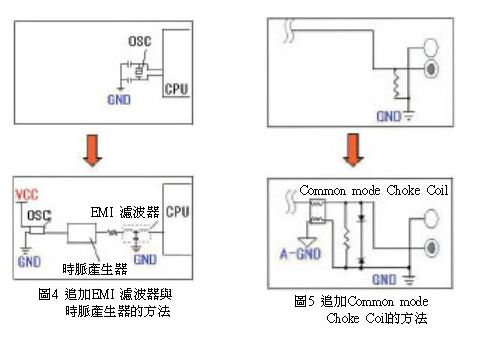

影像输出入单元追加设置Commonmode Choke Coil(DLWxxx系列)(图5)

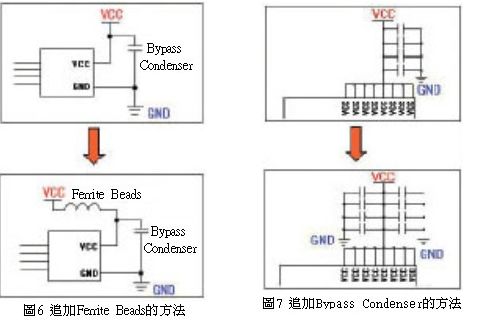

各IC电源输入线的Bypass Condenser与电源之间,追加设置Ferrite Beads(图6)。

追加设置BypassCondenser,使各IC的所有电源脚架,全部从基板电源层(Plane)通过Bypass Condenser提供电源(图7)。

各种EMI噪讯对策a.EMI噪讯对策用电容

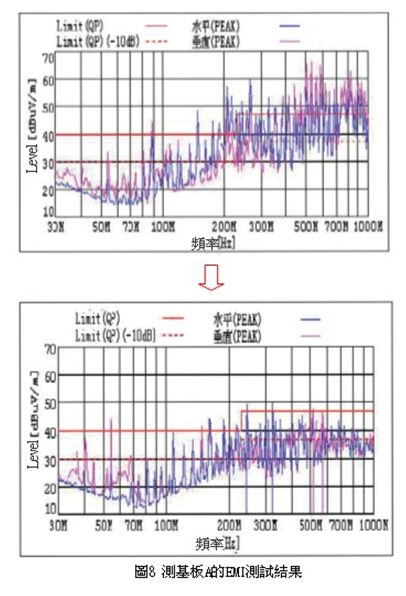

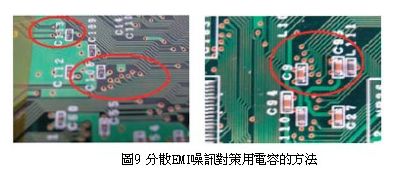

接着进行EMI测试获得图8的测试结果,根据测试结果再进行噪讯抑制设计作业,在此同时将设计变更的被测基板A的设计数据读入EMI噪讯抑制支持工具,并针对支持工具指出的主要部位,例如频率线、Bus导线Via周围,分散设置EMI噪讯对策用电容(图9),主要原因是信号导线的return路径如果太长或是非连续状态时,EMI噪讯有增大之虞,为了缩短Return路径,因此设置连接电源与接地的电容。

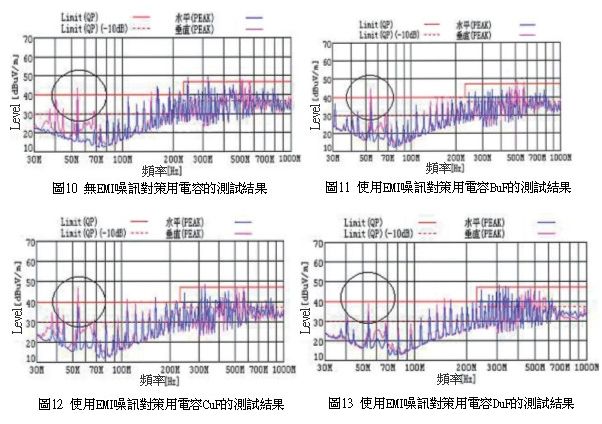

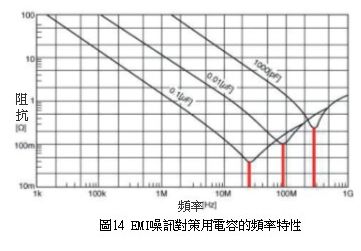

图10~图13是改变上述电容容量时的EMI噪讯测试结果,根据测试结果显示,依照图14的频率范围设置的大容量EMI噪讯对策用电容DuF,可以抑制低频噪讯Level。虽然设置电容增加PCB的容量负载,不过为了要抑制噪讯,设置在各部位的电容频率特性,却可以发挥预期的EMI噪讯抑制效果。

实际应用时只要在频率导线、Bus导线等高频导线图案(Pattern)附近、形成CPU、Return路径的内层面(Plane)的分断附近、形成噪讯出入口的基板侧面附近分散设置EMI噪讯对策用电容,就可以消除该部位周边的噪讯。 对各式各样基板外形、组件封装、导线的PCB而言,只要以一定间隔设置EMI噪讯对策用电容,同样可以获得分散性的噪讯抑制效果。

实际应用时只要在频率导线、Bus导线等高频导线图案(Pattern)附近、形成CPU、Return路径的内层面(Plane)的分断附近、形成噪讯出入口的基板侧面附近分散设置EMI噪讯对策用电容,就可以消除该部位周边的噪讯。 对各式各样基板外形、组件封装、导线的PCB而言,只要以一定间隔设置EMI噪讯对策用电容,同样可以获得分散性的噪讯抑制效果。

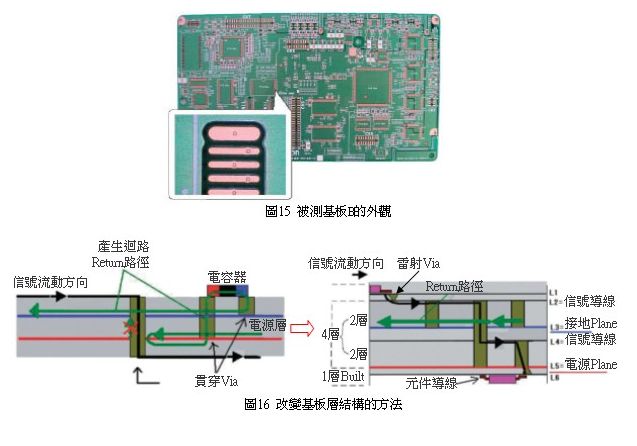

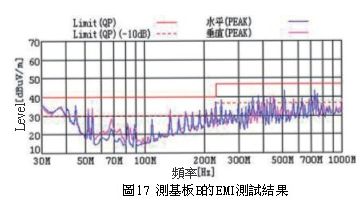

改变被测基板结构主要理由是一般4层基板的Return路径,通常都设有可以通行电源Plane或是最短距离接地,因此在贯穿部位经常造成Return路径迂回问题,如果信号导线包覆接地Plane,如此一来大部份的Return路径会流入接地Plane,进而解决Return路径迂回的困扰,被测基板B就是根据上述构想制成,因此Return路径在PCB整体减少30%,同时缩减信号图案与Return路径构成的电流Loop距离,进而达成EMI噪讯抑制的目的。图16是被测基板B的各层结构图。 图17是被测基板B的EMI噪讯测试结果,根据测试结果显示包含利用外层接地Plane的遮蔽(Field)结构,与回避Return路径迂回的设计确实具有抑制EMI噪讯的效果,不过实际上各式各样的电路基板要作如此的层结构变更,势必面临制作成本暴增的困扰,尤其是所有信号导线都将Return路径列入设计考虑的话,几乎无法作业,因此Layout阶段尽量避免高频信号导线透过Via作布线,同时必需在该信号导线邻近的层设置接地Plane,藉此防止Return路径迂回或是分断,接地Plane之间以复数Via连接,Return路径利用复数Via作理想性的归返。

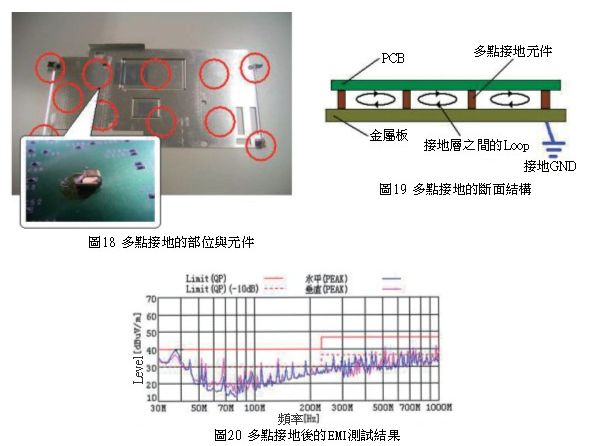

c.设置多点Grand接地 Return电流流动时PCB内的接地Plane会产生电位差,该电位差往往是EMI噪讯的发生原因之一,而且可能会通过PCB形成所谓的二次噪讯,因此将接地Plane与金属板作多点连接(图18、图19),使PCB的侧面与中心位置得电位差均匀化,同时降低接地Plane本身的阻抗(Impedance)并抑制电压下降

图20是多点接地后的EMI测试结果,由图可知低频领域EMI噪讯强度略为上升,不过200MHz以上时EMI噪讯受到抑制,这意味着多点接地的有效性获得证实。

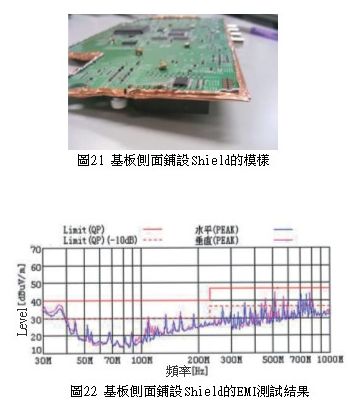

d.铺设Shield 图21是在基板侧面铺设Shield的实际外观,具体方法是在基板侧面粘贴导电胶带,试图藉此抑制基板内层信号线、Via与电源Plane的噪讯,接着再与外层接地Plane连接,测试基板侧面的EMI噪讯遮蔽效果,图22是基板侧面铺设Shield的EMI测试结果,根据测试结果显示200MHz以下时EMI噪讯强度有下降趋势,甚至符合规范的Level,证实基板侧面铺设Shield确实可以抑制EMI噪讯。

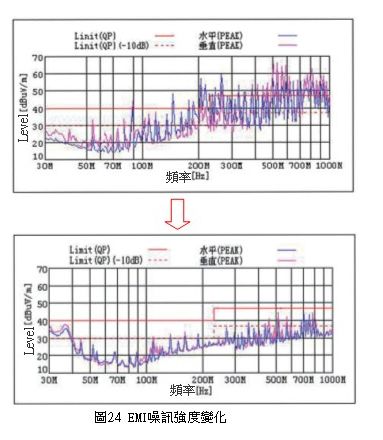

实际制作PCB时在基板侧面铺设Shield,同样会面临成本上升的质疑,类似图23在基板侧面附近设置接地Plane与连续性贯穿Via的新结构,除了可是解决成本问题之外,还可以有效抑制基板侧面的EMI噪讯强度;图24是结合以上各种EMI噪讯对策的PCB测试结果。

结语综合以上介绍的EMI噪讯对策,分别如下所示:

设置EMI噪讯对策用电容

回避Return路径迂回的基板层结构设计

设置多点Grand接地

基板侧面包覆Shield

实际上PCB得EMI噪讯对策会随着组件封装、导线、基板外形、层结构,与筐体限制出现极大差异,因此本文主要是探讨如何在PCBLayout阶段,充分应用EMI噪讯对策手法,根据一连串的对策中找出最符合制作成本,同时又可以满足规范要求的方法。

-

pcb

+关注

关注

4329文章

23195浏览量

400809 -

Layout

+关注

关注

14文章

408浏览量

62065 -

EMI噪讯

+关注

关注

0文章

2浏览量

6452

原文标题:【干货】印刷电路板的EMI噪讯对策技巧

文章出处:【微信号:PCBTech,微信公众号:EDA设计智汇馆】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

pcb layout必须要了解EMI的三要素

教你如何在PCB阶段就避免六成的EMI

PCB板产生EMI的原理以及如何抑制

请问如何改善开关电源电路的EMI特性?

防止EMI噪讯的技巧

浅谈如何应对印刷电路板的EMI噪讯

PMP30930.1-EMI 优化型降压 PCB layout 设计

如何在PCB的Layout阶段,充分应用改善技巧抑制EMI噪讯的强度

如何在PCB的Layout阶段,充分应用改善技巧抑制EMI噪讯的强度

评论