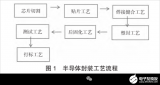

工艺原理

CSP(Chip Scale Package,芯片级封装)技术是一种先进的封装技术,其焊端通常设计为直径0.25mm的焊球。这种设计不仅减小了封装尺寸,还提高了集成度。在焊接过程中,焊膏首先融化,随后焊球融化,这种顺序融化机制有助于避免焊球间的桥连问题,但可能因印刷过程中的少印而导致球窝、开焊等缺陷。因此,对于0.4mm间距的CSP,确保印刷过程中获得足够的焊膏量是关键。

基准工艺

为了优化CSP的焊接效果,基准工艺设定如下:

模板厚度:0.08mm。这一厚度选择旨在平衡焊膏的填充性和溢出控制,确保焊膏能够均匀且适量地覆盖焊盘。

模板开口直径:ф0.25mm,与焊球直径相匹配,以确保焊膏能够准确、完整地填充到焊球下方的区域。

模板类型:推荐使用FG模板。FG模板(Fine Grain模板)以其精细的网孔结构和优异的脱模性能,有助于实现高精度的焊膏印刷。

接受条件

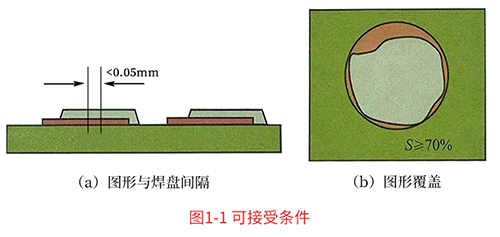

可接受条件:

焊膏图形中心位置:焊膏图形中心偏离焊盘中心应小于0.05mm,以确保焊膏的准确位置,避免焊接不良。

焊膏量:焊膏量覆盖率超出焊盘75%~125%的范围(通过SPI检测)。这一范围确保了焊膏的充足性,同时避免了过量焊膏可能导致的短路问题。

焊膏覆盖面积:焊膏覆盖面积应大于或等于模板开口面积的70%,以确保焊膏能够充分覆盖焊盘,提高焊接的可靠性和稳定性。

印刷质量:

无漏印现象,且挤印引发的焊膏与焊盘最小间隔应大于或等于0.5mm²,以避免短路风险。

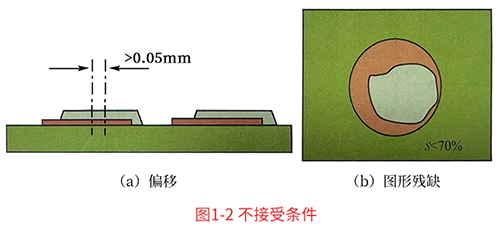

不接受条件

焊膏图形中心位置偏移:图形中心偏离焊盘中心大于0.05mm,这可能导致焊接不良,产生锡珠,影响封装质量。

焊膏量异常:焊膏量覆盖率超出焊盘75%~125%的范围,无论是过多还是过少,都可能对焊接质量产生不利影响。

焊膏覆盖面积不足:图形覆盖面积小于模板开口面积的70%,这可能导致焊盘部分区域无焊膏覆盖,进而影响焊接的可靠性。

印刷缺陷:出现焊膏漏印、严重挤印与拉尖等缺陷,这些都会直接影响焊接的质量和稳定性,因此不被接受。

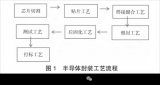

总的来说,CSP封装工艺的成功实施需要严格控制焊膏的印刷过程,确保焊膏的准确位置、适量填充和良好覆盖,以满足严格的焊接质量要求。

审核编辑 黄宇

-

封装

+关注

关注

126文章

7862浏览量

142873 -

CSP

+关注

关注

0文章

124浏览量

28073 -

焊盘

+关注

关注

6文章

551浏览量

38133

发布评论请先 登录

相关推荐

功率模块封装工艺

功率模块封装工艺有哪些

瑞沃微:一文详解CSP(Chip Scale Package)芯片级封装工艺

mos封装工艺是什么,MOS管封装类型

半导体封装工艺面临的挑战

半导体封装工艺的研究分析

浅谈芯片倒装Flip Chip封装工艺

什么是COB封装工艺?COB封装工艺的优势 COB封装工艺流程有哪些?

详解芯片尺寸封装(CSP)类型

CSP(Chip Scale Package)封装工艺详解

CSP(Chip Scale Package)封装工艺详解

评论