摘要

先进封装技术持续朝着连接密集化、堆叠多样化和功能系统化的方向发展,探索了扇出型封装、2.5D/3D、系统级封 装等多种封装工艺。晶圆微凸点技术已被广泛应用于各种先进封装工艺技术中,是最重要的基础技术之一。本文介绍了微凸点 制备的主要技术并进行优劣势比较,同时详述了锡球凸点和铜柱凸点两种不同的微凸点结构,为微凸点技术的更深入研究提供 参考。最后,本文整理了微凸点技术在先进封装中的应用,并展望了未来的发展趋势。

0 引 言

自 1965 年摩尔定律提出后的半个多世纪以来,半 导体集成电路一直遵循着摩尔定律发展。2022 年, 三星和台积电先后宣布 3 nm 制程工艺实现量产,工艺 制程的节点逐步接近原子尺寸级别。通过缩小晶体管 尺寸来提高芯片集成度和性能的方式,成本和技术难 度会大幅增加,先进封装逐步成为延续摩尔定律的主 要方式。先进封装的目的是提升功能密度,缩短互联 长度,提升系统性能,降低整体功耗。先进封装主要 有扇出型封装(fan-out,FO)、2.5D/3D、系统级封装 (system-in-package,SIP)等封装形式。晶圆微凸点作 为先进封装中的关键基础技术之一,其主要作用是电 信号互连及机械支撑。目前绝大部分的先进封装均需 要用到晶圆微凸点技术,而凸点的制备则是微凸点技 术最为关键的环节。本文将综述晶圆微凸点的主要制 备技术、结构及其在先进封装中的应用研究进展,并 结合未来市场发展趋势,展望微凸点技术的发展方向。

1 晶圆微凸点制备方法及应用

晶圆微凸点最早由 IBM 公司于 1970 年发明,随 着工业技术的发展,为了满足特定的市场需求,凸点 的种类也越来越多。按凸点材料种类可分为金(Au) 凸点、铜/镍/金(Cu/Ni/Au)凸点、铜柱(copper pillar) 凸点、锡/铅(Sn/Pb)凸点和锡/银/铜(Sn/Ag/Cu)凸 点等。按凸点结构和形状可分为蘑菇形、直状、圆柱 形、球形、迭层、周边形、微型和面阵凸点等。根据 应用的领域和场景的差异,凸点形状不一样,其中应 用最广的是圆柱形、球形和面阵凸点。凸点制备方法 有蒸发溅射法、电镀法、化学镀法、机械打球法、焊 膏印刷法和植球法等。本文将重点介绍应用比较广泛 的机械打球法、焊膏印刷法、植球法和电镀法。不同 制备方法有着不同的应用领域,也表现出不同的优劣 势。表 1 为晶圆微凸点不同制备方法的优劣势对比。

1.1 机械打球法

机械打球法制作的凸点叫钉头凸点(stud bump bond,SBB),是使用金丝球焊机利用热压超声键合工艺 制作凸点的一种技术,常用来制备金钉头凸点。SBB 工艺的基本原理如图 1 所示。

首先通过电火花放电的方法在金丝尾端成球,然后在加热、加压和超声的共同作用下,将 Au 球焊接到芯片的电极上,接着劈刀提起,线夹保持打开,送出一段尾丝,最后线夹关闭,劈刀向上运动,通过拉伸颈缩作用切断金丝,完成整个凸点的制作过程。制备 的钉头凸点如图 2 所示。机械打球法可以直接在离散芯片的金属铝电极上制作钉头凸点,不需要在电极区 制作出凸点下金属层(under bump metal,UBM),工艺简单,成本低。

头凸点一般为金凸点。金凸点因其电导率较高,且抗 电迁移能力强,被应用于显示驱动芯片、CMOS (complementary metal oxide semiconductor)图像传感 器、指纹传感器、射频识别芯片领域。崔洪波等采用AuPd 1%丝在微波 GaAs 芯片上使用美国 Westbond 公司的 7700E-79 型半自动金丝球焊机制作出直径 80 μm 的钉头金凸点,完成了超声焊接,为凸点芯片倒 装焊接以及电性能研究打下了良好基础。何中伟采 用直径 31.8 μm 的金丝,通过自动球焊机制作出直径为 (115±4)μm 的钉头金凸点,经 F&K5600 型键合拉 力/剪切力测试仪测量,最小抗剪切力为 0.658 1 N,能 够达到 GJB548A、华东光电集成器件所规范、美国 Palomar 公司规范、中国台湾 Chipbond 公司标准剪切 力要求。

近年来,关于钉头金凸点的研究也在持续进 行,从 1 层钉头金凸点到 2 层金凸点,从金球位置测试,到金球推力、直径、厚度、高度、合金率测 试等方面展开深入研究,推进钉头金凸点更好地应 用于电子封装领域。但当器件的电极(I/O)数较多 时,成本将会大幅上升。Zama等尝试使用 Cu 代替 Au 制作钉头凸点,抗剪切力等性能没有明显 下降,但由于 Cu 容易氧化和腐蚀,未能大规模使 用。因此,当器件引脚数较多时,通常采用其他方 式制作凸点。

1.2 焊膏印刷法

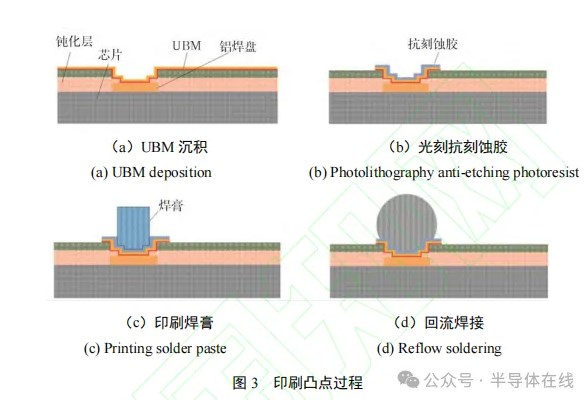

焊膏印刷法是一种引自于印制电路板(printed circuit board,PCB)行业的在晶圆上漏印制作凸点的工 艺,主要步骤包括:画图制版、制作焊膏漏印版、对 中焊膏漏印版、印刷焊膏、焊接、清洗和检测。此 方法是在凸点下金属层表面特定区域印刷焊料,最后 通过热回流形成所需凸点。焊膏印刷法的工艺流程 如图 3 所示。

焊膏印刷法因其可以直接采用表面贴装技术 (surface sounted technology,SMT)生产工艺中的焊膏 印刷设备,设备资金投入较小,成本较低,被广 泛应用于 200~400 m 的焊盘间距的凸点制备。但 对于小间距焊盘,由于模板印刷不能均匀分配焊料 体积,为保证凸点高度和球径,印刷的焊膏较多, 通过常规的焊膏印刷、回流焊接后,焊料球之间容易 互联,且无法修复,其应用受到限制。另外,由于焊 膏中存在有机添加剂,在后续高温回流过程中有机添 加剂会挥发,从而产生空洞。随着电子技术的不断 发展,晶圆凸点节距和直径也变得越来越小,因模板 网板孔太小、容易发生堵塞而导致焊料凸点均匀性较 差,致使产生产品可靠性风险。对于消费电子而言, 凸点直径集中在 150 μm 以下,节距集中在 200 μm 以 下,焊膏印刷技术已经不再适用,需要开发其他更精 密的凸点制作技术。

1.3 植球法

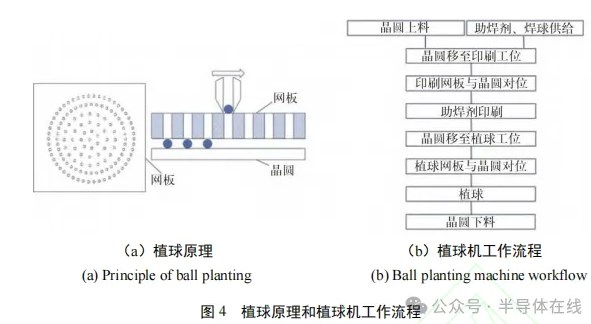

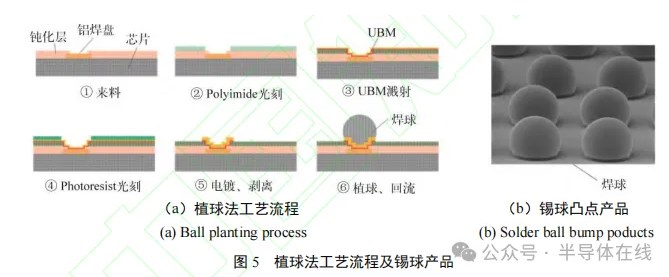

植球法是专门针对焊料凸点制造开发的,与 SMT 技术的兼容性较好。植球法采用晶圆级植球机, 通过定位相机对已经做好电路再分布的晶圆进行精 准定位,使用钢网印刷的方式将助焊剂和锡球转印 至对应的焊盘位置,再通过氮气氛围高温回流完 成锡球与焊盘的焊接,从而完成整个工艺过程。植 球机由上料系统、下料系统、印刷系统和植球检查系统组成,其中最主要的是印刷系统。印刷系统 分为助焊剂印刷和印刷植球两部分,均采用刮刀在 与晶圆图案花形一致的网板上反复运动,将助焊剂均 匀涂覆到UBM表面,再将锡球扫入网板筛孔中,利 用助焊剂的粘附性将锡球植入晶圆上。刘劲松等采用国内自主研制的晶圆级微球植球机 WMB-1100 完 成在12英寸晶圆上植入250 μm 的锡球,植球精度 小于 1/2 球径。植球原理及植球机工作流程如图 4 所示,Lin 等在 300 mm 晶圆上采用植球法完成了 直径为 70 m、间距为 130 m 的 SnCu0.7 微型球(单 颗芯粒 2 000 个 I/O)植入,良品率超过 99.99%, 无锡球遗漏和桥接。

植球法一般采用 Sn/Pb 球和 Sn/Ag/Cu 球。随着植球 技术的发展,国外有日本爱立发( Athlete )、 AIMECHATEC、德国 Pac Tech,国内有上海微松工业自 动化有限公司、上海世禹精密机械有限公司等目前已实 现 60 μm 直径锡球植球工艺量产,植球精度小于 1/3 球 径,良率可控制在 99.997%以上。植球法制作晶圆凸点 会涉及到光刻、湿法去胶、湿法刻蚀等工艺,工艺流程 如图 5(a)所示,锡球凸点产品如图 5(b)所示。

植球法因其工艺稳定、产能大,良品率高,适用于 晶圆凸点的大规模生产,被广泛应用于图像传感器、 电源管理芯片、高速器件和光电器件等领域,但其需要 先在焊盘上制作 UBM 和印刷助焊剂,工艺较机械打球 法和焊膏印刷法而言更加复杂,成本更高。且对于 60 μm 直径以下的凸点,植球法受限于植球技术和网板制造技 术的发展,容易发生多球、少球、球偏移等问题,良品 率大幅降低,因此对于小直径凸点,植球法不再适用。

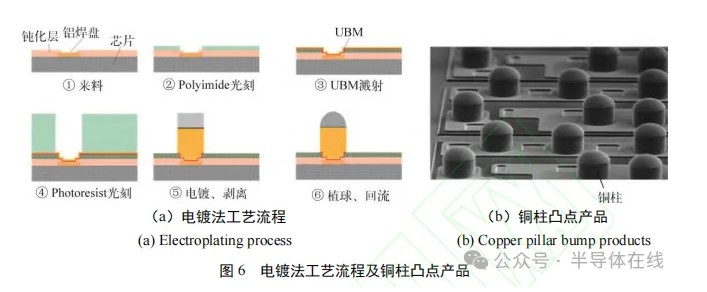

1.4 电镀法

电镀凸点是采用电化学沉积技术在晶圆表面的物 理气相沉积(physical vapor deposition,PVD)种子层 上(通常是 Ti/Cu 薄膜)沉积金属的工艺方法。电镀 法精度高,对于细间距、高密度的凸点制备具有明显 优势。就凸点电镀方式而言,根据晶圆放置方向,电 镀设备分为垂直镀和水平镀。电镀工艺主要分为预润湿、电化学沉积和清洗3个步骤。预润湿是将纯水 均匀喷覆到金属种子层上,可提高电镀液在种子层上分布的均匀性,减少气泡、无镀层、镀覆不均匀等失效问题;电化学沉积是利用金属的氧化还原特性,使电镀液中的金属离子均匀沉积到金属种子层表面,用于制备金属线、金属柱等;清洗是为了去除镀件上残留的电镀液,避免发生电化学腐蚀、镀液污染等问题。电镀工艺流程及电镀的铜柱凸点产品如图 6 所示。

电镀方法在小直径、小节距凸点制备方面性能表 现良好。陈聪等通过电镀方法在Si基板上制备了直径为60μm、高度为54 μm 的 Cu-Ni-AuSn 铜柱凸点, 芯粒内凸点高度均匀性小于 2%;Oi 等使用 i-THOP 设计规格的基板,通过电镀方法制备了直径为 25 μm,间距为 40 μm 的铜柱凸点,实现了高密度凸点芯片倒 装封装工艺。Yoon 等采用电镀方法制备了间距为 40 μm、高度为 20 μm 的 Cu/SnAg 组分的凸点,经倒装 后其可靠性测试满足 JEDEC(joint electron device engineering council)标准。采用电镀方法制备出的晶圆 凸点高度均匀性好,一般可控制在 5%以内,且工艺可 控。除此之外,电镀技术已经能够实现小于 10 μm 直 径的晶圆凸点制造,且工艺相对成熟,被广泛应用 于图像处理器、存储器芯片、ASIC(application- specific integrated circuit)、FPGA(field programmable gate array)、电源管理芯片、射频前端芯片、基带芯片、功率放大器等产品中。

2 晶圆微凸点结构

先进封装中,晶圆凸点往往是通过 UBM 连接到晶 圆表面的,制作凸点之前通常需要先进行 UBM 制备作 为凸点“承载体”。因此,业内常说的晶圆凸点结构一 般是包含 UBM 层和凸点。

2.1 UBM 层

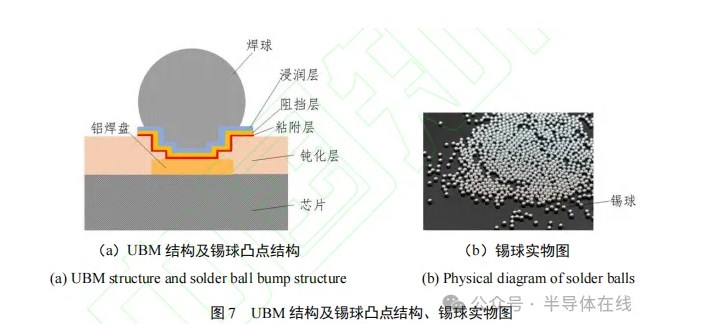

芯片电极的材料通常是铝或铝合金。若铝和铜柱 或者锡凸点直接互连,易生长形成晶粒粗大的金属间 化合物(inter metallic compound,IMC),影响互连可 靠性,为保证凸点与电极之间的结合力满足器件要求, UBM 层需要提供粘附、阻挡扩散、提供润湿的作用, 如图 7(a)所示。由于任何一种单质金属都不能同时 具备这 3 种功能,因此 UBM 层通常情况采用多层金属 薄膜结构。粘附层要求与铝的接触电阻小,热膨胀系 数接近,且需要与铝层及晶圆钝化层粘附性好,该层 金属常常选用 Ti、Ti-W、Cr 和 Ni 等。阻挡扩散层主 要作用是防止凸点材料与 Al 电极之间发生相互扩散, 从而影响器件性能,该层金属通常选用 Ni、Ti、Cu、 Pd 和 Pt 等。润湿层要求与凸点材料形成良好浸润效果, 在凸点回流焊接过程中不容易或者不会生成不利的 IMC 层,该层金属通常采用 Au、Cu 等。产品应用领 域不同,对应的 UBM 层结构也不同,经过长期的实际 应用与研究优化,逐步形成了一些相对固定的 UBM 薄 膜层结构,如 Ti-W/Cu、Ti-W/Au/Cu、Cr/Cr-Cu/Cu、 Ti/Cu 和 Ti/Ni/Au 等。UBM 层材料选择必须基于所要 求的凸点金属化体系、芯片金属化结构、芯片工作条 件、可靠性要求、电流传输要求和工艺流程要求(如 多次回流焊)等。UBM 层的制作方法有溅射镀膜和化 学镀,目前大多数的 UBM 层结构采用溅射镀膜制作。

2.2 凸点

凸点的结构有多种,其中锡球凸点(solder ball bump)和铜柱凸点(copper pillar bump)较为常见。对于锡球凸点制作工艺,通过高温回流使得锡球与焊盘 连接,但是锡球凸点在回流过程中容易发生坍塌现象, 导致与相邻的锡球凸点桥接而造成短路。当芯片外引 端节点距离低于 130 μm 时,锡球凸点便不再适用。铜柱凸点以铜柱为支撑,在其顶部加上少许锡银焊料, 可以在实现相同凸点高度的同时,减少了焊料的使用。铜柱凸点的节距一般在 60~140 μm 之间,铜柱凸点代替锡球凸点,可以实现更小间距的芯片互连,可应用 于更高引线数量的先进封装。

1)锡球凸点

锡球凸点常用于倒装芯片焊接互连,焊料大多是 含铅焊料(如 SnPb 等),锡球凸点结构如图 7(b)所 示。自中国颁布了禁止使用铅及其化合物的法令以来, 在非军领域,Sn 基无铅焊料成为最主要的互连材料。Sn 基焊料适当添加银、锌、铜、铋等金属元素形成合 金来改善焊料性能,得到满足器件所需的机械、电气 和热性能,常见的有 Sn-Ag-Cu、Sn-Cu、Sn-Ag、 Sn-Zn 和 Sn-Bi 焊料。Sn-Ag-Cu(SAC)因其具备良好的焊料硬度、抗拉强度、屈服强度、剪切强度、冲击 强度和蠕变强度,逐步成为电子钎焊最多的无铅焊料 合金体系,当前应用最多的是欧盟的 Sn3.8Ag0.7Cu,日 本的 Sn3.0Ag0.5Cu(SAC305)、Sn3.5Ag0.7Cu 等焊料, 这些焊料都属于高银体系(Ag 含量大于 1%),性能更加 优异。Sabbar 等研究了 Ag 含量对 SAC 焊点的机械性 能的影响,结果显示,随着 Ag 组分的含量增加,回流 后生成的 Ag3Sn化合物就越多,对焊点的抗剪切能力提升作用明显。然而高银含量导致成本高昂,因此行业内需开发低银体系以节约成本。据研究,低银焊料相比于 高银焊料,具有更低的成本和一致的润湿性能。低银 焊料的微观结构中不存在 Ag3Sn IMC,表明低成本低银焊料具有良好的可焊性和可靠性,但随着银含量的降低, 焊料的力学性能下降,熔点会上升。

添加金属元素 Bi、Ni、Al 等能提升低银焊料的力 学性能。Lin 等研究了 Bi 和 Ni 对 SAC 焊料力学性 能的影响,结果显示,SAC 纳米硬度为 10.62 GPa,而 加入了 Bi 和 Ni 的 SAC-Bi 和 SAC-Ni 焊料,其纳米硬 度达到了 16.88 GPa 和 20.48 GPa,相较于 SAC 有大幅 提升。Ren 等在 SAC305 焊料中加入 0.5%~10%的 In 粉,研究表明,随着 In 含量的增加,焊料的硬度显 著升高。Sun 等研究了纳米 Al 对 SAC105 焊料剪切 性能的影响,纳米 Al 加入后其剪切力为 66.4 N,优于 未添加的 SAC105(剪切力为 54.2 N),表明纳米 Al 的 加入能提高焊点剪切力。添加 Bi、Ni 和 Zn 等可降低 低 银 焊 料 的 熔 点 。Liu 等发现在 Sn0.7Ag0.5Cu (SAC0705)钎料中添加 Bi 和 Ni 元素能显著降低焊料 熔点。研究表明,质量分数 3%的 Zn 加入 SAC103 焊料后,熔点从 227.7 ℃降至 220.8 ℃。经过大量研 究和改进,目前研究最多、应用范围最广是 Sn1.0Ag0.5Cu (SAC105)和 Sn0.3Ag0.7Cu(SAC0307)这两种焊料, 被认为是第二代无铅焊料。

2)铜柱凸点

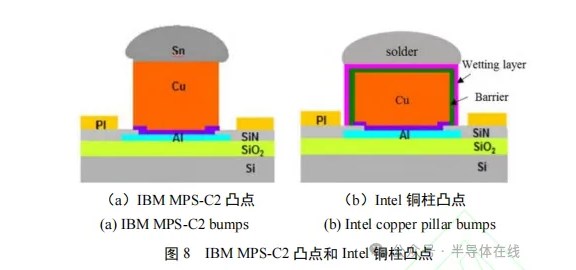

铜柱凸点由铜柱和焊料帽组成,铜柱提供机械支 撑和电气连接,焊料帽将芯片与基板通过焊接进行互 连。IBM 公司发明了一种两层结构的 Cu-Sn 凸点 (MPS-C2),凸点结构如图 8(a)所示。在焊接互 连过程中,锡帽与铜柱界面会生成金属间化合物 (IMC),IMC 层晶粒不均匀会导致很高的脆性,造成 器件长期服役过程中可靠性和寿命受到影响。研究表 明,当其他条件保持不变时,Sn/Ag凸点因形成了Ag3Sn 微粒的稳定结构,比 Sn/Cu 凸点拥有更优异的电迁移特性,Sn/Ag 焊料也逐渐取代了纯 Sn 焊料。

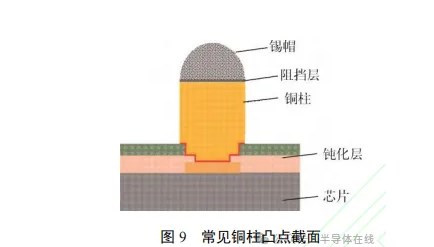

随着先进封装技术的发展,铜柱凸点节距已到达 20 μm 以下。Liu 等对 10 μm、5 μm 和 1 μm Sn/Cu 凸点 IMC 生长过程进行研究。结果表明,当凸点直径 从 10 μm 减小至 1 μm 时,IMC 生长速度会持续增加, 这种现象也被称为“IMC 尺寸效应”。IMC 持续增加会 发生空洞等失效情况。为解决这种缺陷,通常在铜柱 和锡银层中间加入金属镍层作为阻挡层以抑制凸点界 面的 IMC 生长,镍层厚度通常控制在 2~5 μm 范围之 间。Bertheau 等分别研究了直径为 25 μm 和 80 μm 的 Cu/Sn 和 Cu/Ni/Sn 两种凸点在不同环境中的微观结 构演变过程。结果表明,Cu/Ni/Sn 凸点比 Cu/Sn 凸点 具有更慢的 IMC 粗化速率,说明镍层对于铜锡金属具 有阻挡扩散的作用。Intel 公司发明了一种间距为 175 μm、直径为 105 μm 的新型铜柱凸点。该凸点通 过在铜柱外表面覆盖一层阻挡薄膜和润湿薄膜,使其具备优异的润湿性和抗电迁移性能,凸点结构如图 8 (b)所示。现如今,常见的铜柱凸点结构如图 9 所示, 为铜柱+阻挡层+锡帽结构,锡帽常常是 SnAg 合金,阻 挡层一般为金属 Ni。

3 微凸点在先进封装中的应用及发展趋势

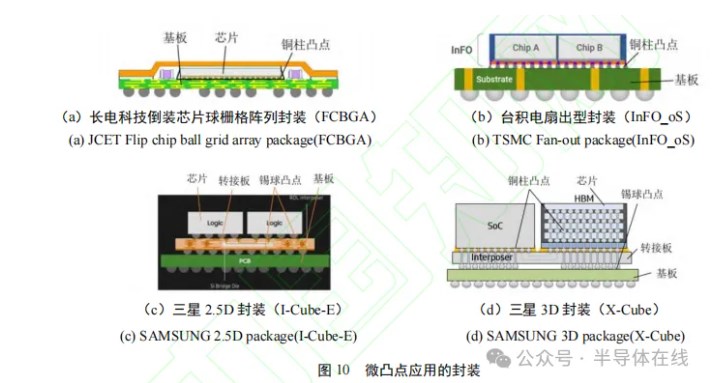

晶圆微凸点广泛应用于倒装芯片球栅格阵列封装 (flip chip ball grid array,FCBGA)、扇出型封装和 2.5D/3D 封装等各类先进封装中,已实现再布线层 (redistribution layer,RDL)线宽/线距 5 μm 的大规模量 产。倒装芯片技术是目前市场占比最多的封装技术, 被应用于军工、无源滤波器、存储器等领域。晶圆微 凸点除应用于常规线宽/线距 5 μm 的产品中,还应用于 如华天、长电、台积电、三星、Intel 等公司密度更高 的扇出型、2.5D 及 3D 封装中。华天科技嵌入式硅基扇 出封装、长电科技多维扇出封装等封装技术,采用 高密度再布线技术,线宽/线距为 2 μm;台积电 InFO ( integrated fan-out on substrate ) 技 术平 台 孵 化 的 InFO_PoP、InFO_oS 和 InFO_LSI 3 种扇出型封装,其 中 InFO_oS 线宽/线距为 2 μm。高密度扇出型技术应用 于射频、无线芯片、处理器、基带芯片等封装领域。Intel 公司嵌入式多硅片互连桥型 2.5D 封装,通过硅桥来实 现高带宽和短距离的数据通信,线宽/线距为 1 μm;三星提供的 2.5D 封装有 I-CUBE-E、I-CUBE-S 和 H-CUBE,台积电有 CoWoS_L、CoWoS_R 和 CoWoS_S, 其中 CoWoS_R 的 RDL 间距仅为 4 μm,线宽/线距为 2 μm。2.5D 封装广泛应用于图像处理、智能穿戴设备 领域。Intel 公司的 Foveros3D 封装已能够实现多个 不同制程的芯片互连,台积电的 SoIC_WoW 3D 封装 已能够实现 10 000/mm2 I/O 高密度封装,三星的 X-CUBE 已 实 现 超 薄 转 接 板 的 工 艺 稳 定 性 (100 μm),X-CUBE 封装线宽/线距已在 2 μm 以下。3D 封装广泛应用在智能芯片、5G 领域。

图 10 为晶圆微凸点在各类先进封装中的应用,列 举了具有代表性的封装示意图。其中图 10(a)为国内 封测领军企业长电科技的 FCBGA 结构示意图,芯片与 基板间采用铜柱凸点进行互连,节距为 130 μm,直径为 80 μm;图 10(b)为 InFO_oS,是由多个芯片扇出型工 艺的集成,芯片与基板之间采用铜柱凸点进行互连,相 对于倒装芯片,大大提升了功能密度;图 10(c)为三星 的 I-CUBE-E 2.5D 封装,采用了无硅通孔(through-silicon via,TSV)结构,以布线中介层作为转接板,芯片底部 与转接板上部、转接板底部与基板上部通过锡球凸点进 行互连;图 10(d)为三星 X-Cube 3D 封装结构,HBM (high bandwidth memory)芯片是带有 TSV 的双面凸点 结构(一般为铜柱凸点),采用两面成型自动焊完成芯 片间互连,这种立体堆叠互连结构大幅度缩短了信号 传输距离,提升数据传输速度,降低功耗。

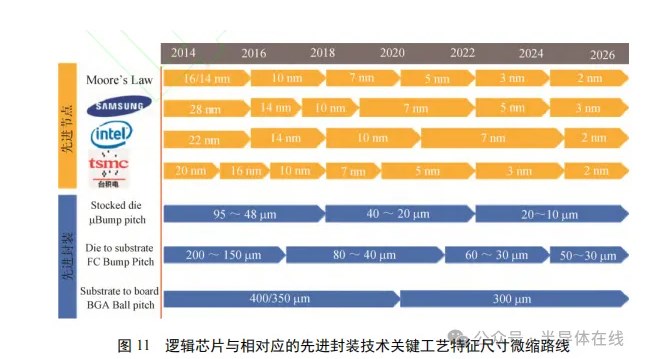

图 11 为逻辑芯片与相对应的先进封装技术关键工 艺特征尺寸微缩路线图。图中显示,自 2018 年以来, 先进封装晶圆微凸点间距已经下降到 50 μm 以下, 40~50 μm节距的晶圆微凸点应用于2.5D/3D堆叠的半 导体产品中的互连可靠性及可行性已经得到验证,并实现批量生产。然而,随着人工智能和 5G 技术的不断 发展,封装产品为获取更高的带宽以达到更高的数据 传输速率,要求微凸点节距和直径不断缩小,导致互 连可靠性问题频发。器件往往同时要求高的凸点高度和小的直径,长期服役过程中,IMC 不断增长会消耗焊 料,由于焊料体积的收缩,会导致焊接部位产生空隙, 影响焊点的完整性,进而影响互连可靠性。当凸点间距 减小至 20 μm 以下时,在热压键合时,若产生细微的 倾斜,则会使焊料变形挤出而发生桥连短路。另外, 因尺寸效应,在小直径的凸点中,IMC 占据了凸点大 部分的体积,表面扩散和柯肯达尔孔洞等问题急剧增 加,微凸点进一步缩减互连节距遇到了前所未有的瓶颈。随着索尼获得 Ziptronix 公司混合键合技术授 权,推出了混合键合技术高性能图像传感器。半导 体业界逐步意识到,混合键合将会成为突破凸点微型 化瓶颈的有效途径。此后,Intel、台积电、三星和华为 等领先机构陆续对混合键合技术展开了深入的研究。Intel公司的Foveros和台积电集成片上系统都应用了混 合键合的三维集成产品。Cu-Cu 键合是目前相对较为成 熟的混合键合方案,即在无焊料的铜柱之间直接完成 互连,能够有效避免桥接问题,具备优良的电、热、 机械性能,Cu-Cu 键合技术在超小间距(小于 10 μm) 的芯片互连中表现出了巨大的优势。

4 结 论

在先进封装工艺技术中,凸点的制备方法主要有 机械打球法、焊膏印刷法、植球法和电镀法。机械打 球法受制于金凸点成本和效率问题,目前仅用于 I/O 数 量不多、对抗电迁移可靠性要求高的产品;焊膏印刷 法因其工艺限制性不适用于低于 200 μm 的细间距凸点 制作;植球法适用于 60 μm 以上凸点制备;电镀法可 满足 10 μm 以下凸点制备。凸点结构主要有锡球凸点 和铜柱凸点两大类,锡球凸点应用最广泛的是 SAC 焊 料体系,受制于成本,低银的 SAC 体系 SAC105 和 SAC0307 未来可能成为主流;铜柱凸点通常为铜柱+阻 挡层+锡帽结构。晶圆微凸点广泛应用于倒装封装、扇出 型封装和 2.5D/3D 封装中,但随着凸点互连节距不断缩 小,可靠性问题频发。未来晶圆微凸点将朝着更小节距、 更小直径方向不断发展,同时无焊料的铜柱凸点的 Cu-Cu 键合互连方式逐步在小节距领域占据主导地位。

转载:半导体在线

-

晶圆

+关注

关注

52文章

4917浏览量

128016 -

封装技术

+关注

关注

12文章

549浏览量

67991 -

封装工艺

+关注

关注

3文章

57浏览量

7973 -

先进封装

+关注

关注

2文章

405浏览量

246

原文标题:晶圆微凸点技术在先进封装中的应用研究进展

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

长电科技全新12英寸晶圆凸点产线在韩国先进FC封装工厂建成并投入大规模量产

开启新摩尔定律时代 IDM及晶圆代工厂商承担先进封装技术先驱角色

什么是先进封装?先进封装技术包括哪些技术

晶圆微凸点技术在先进封装中的应用

晶圆微凸点技术在先进封装中的应用

评论