答案是:Digital Discovery

口袋式高速逻辑分析仪

当新入手一款Zynq开发板后,一般新手在串口输出一个hello world,实现功能就可以了。而对于一些对于Zynq有一定了解的老手而言,往往则会去尝试了解板上硬件的特性和时序,探究hello world输出背后整个系统是如何运作的。

事实上,对于一款新的Zynq板卡来说,在启动序列中QSPI传输的速度不是一个明显的规范,本文教程就将教你如何使用Digital Discovery口袋式高速逻辑分析仪来快速分析启动序列并确定时序。

01

硬件清单

-

Digital Discovery口袋式高速逻辑分析仪

-

带有flash的Zynq开发板(本文中使用Digilent Zybo作为被测对象)

-

SOIC测试夹(若有最佳)

-

杜邦线

注:事实上,除了Digital Discovery之外,当然你也可以用经典的Digilent Analog Discovery 2来操作,后者同样带有逻辑分析仪功能。这里更为推荐使用Digital Discovery,有两个原因:一是由于QSPI时钟频率很高,超过100MHz,因此所选的仪器需要具有足够的采样率。二是Digital Discovery具有512 MB的DDR,可以完成大规模数据存储的要求。

02

连接Digital Discovery

连接关系如下:

|

QSPI 信号 |

QSPI/测试夹引脚 |

DigitalDiscovery引脚 |

|

cs |

7 |

DIO0 |

|

clk |

16 |

DIO1 |

|

d0 |

15 |

DIO2 |

|

d1 |

8 |

DIO3 |

|

d2 |

9 |

DIO4 |

|

d3 |

1 |

DIO5 |

|

gnd |

10 |

Gnd |

在使用如上图所示的杜邦线进行连接时,要注意保证信号完整性,避免串扰。在某些时候,需要将某个信号和地线进行缠绕,如图中的蓝色cs信号就使用了接了地的黑线进行了缠绕。

03

QSPI脚本

为了将QSPI的信号转换成数据,在逻辑分析仪的WaveForm软件中增添了一个“定制”通道,并使用js语言编写了一个“解释器”。代码如下:

// rgData: input, raw digital sample array// rgValue: output, decoded data array// rgFlag: output, decoded flag arrayvar c = rgData.length // c = number of raw samplesvar pClock = false; // previous cock signal levelvar iStart = 0; // used to keep track on word start indexvar cByte = 0; // byte count per transmissionvar cBits = 0; // bit countervar bValue = 0; // value variablevar fCmd = true;for(var i = 0; i < c; i++){ // for each sample var s = rgData[i]; // current sample var fSelect = 1&(s>>0); // pin0 is the select signal var fClock = 1&(s>>1); // pin1 is the clock signal var fData = 1&(s>>2); // pin2 is the data signal var fData4 = 0xF&(s>>2); // DIN 2-5 DQ 0-3 if(fSelect != 0){ // select active low // while select inactive reset our counters/variables iStart = i+1; // select might become active with next sample cByte = 0; cBits = 0; bValue = 0; pClock = false; fCmd = true; continue; } if(pClock == 0 && fClock != 0){ // sample on clock rising edge bValue <<= 4; // serial data bit, MSBit first bValue |= fData4; cBits++; if(cBits==2){ // when got the 8th bit of the word store it cByte++; // store rgValue/Flag from word start index to current sample position for(var j = iStart; j < i; j++){ // Flag change will be visible on plot even when data remains constant. // This is useful in case we get more consecutive equal values. rgFlag[j] = cByte; rgValue[j] = bValue; } iStart = i+1; // next word might start after this sample cBits = 0; // reset bit count for the next byte bValue = 0; // reset value variable } } pClock = fClock; // previous clock level}

除了使用定制的“解释器”外,我们还可以使用标准的SPI来分析那些没有通过QSPI发送到指令,例如第一条读取指令。

04

触发与采样

虽然QSPI的最高时钟频率是100MHz,但在启动过程中的最高频率仅为25MHz。此外,整个启动过程大概需要700ms。因此对于同时满足大量样本和高速采样率,这也正是选择Digital Discovery的原因——200MHz的采样速度可以在1.3s内采样268M的样本数据。

采样本身是十分浪费资源的,这个过程需要使用16GB的电脑内存,并且需要很长的时间来完成数据的处理。

触发设置在CS信号的下降沿。

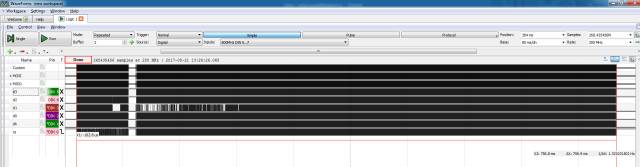

下图是Waveforms中整个QSPI的传输过程。注意图中采样信号的短暂中断,从这个时候起时钟频率由5.4MHz变为了25MHz。

05

启动传输

想要明白所传输的数据含义需要阅读两个文档,一是Zynq技术参考手册(www.xilinx.com/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf),另一个是flash memory的数据手册(www.cypress.com/file/177966/download)。

Zynq与flash之间使用SPI协议进行通信,Zynq发送通过D0向flash发送指令。所发送的第一条指令是0x03 0x00 0x00 0x20,含义是SPI读,读起始地址是0x20。Flash通过D1接收0x66 0x55 0x99 0xaa。Flash读指令的含义在flash memeory的第85页做了解释。

(点击可查看大图)

在Zynq技术参考手册的第170到179页解释了所回复指令的含义,简单说这组字节告诉了Zynq内存是支持QSPI的。还需要注意到,此时的SPI时钟是5.405MHz,是一个比较低的速度。

从这点上看,确定了Zynq的内存支持QSPI,并且所有的交互都将在这4条数据线上完成。例如,下一条指令是0x6b,跟在一个3个字节的地址的后面。0x6b表示一个quad读指令,在8个时钟周期后的QSPI解释器上看到响应,这是虚拟字节。

(点击可查看大图)

在本例中,地址是0x1d,读取7个字节。这些字节来自地址0x1d、0x1e、0x1f,它是中断表的一部分,然后从地址0x20开始读取4个字节,这是在第一个SPI读取时读取的相同字节。

Znqy将继续读取字节,地址逐渐增加,直到0x45,这是bootROM Header的结尾。

但是,由于我们无法访问BootROM的代码,其余的引导序列就不那么透明了。在某个时候,FSBL(第一阶段引导加载程序)将开始运行,最有可能的是当SPI时钟频率变化到25 MHz的时候,如下所示,也就是在引导过程开始后的84毫秒。

(点击可查看大图)

然后,FSBL将读取引导映像文件并分析它包含的不同分区,包括配置Zynq PL部分的bit文件,在ARM中运行的elf文件。

关于引导镜像和启动过程可以阅读这一用户手册(www.xilinx.com/support/documentation/user_guides/ug821-zynq-7000-swdev.pdf)。

-

FPGA

+关注

关注

1629文章

21729浏览量

603016 -

赛灵思

+关注

关注

32文章

1794浏览量

131246 -

Zynq板卡

+关注

关注

0文章

1浏览量

2064

原文标题:如何以开挂的方式来查看Zynq启动顺序?

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文搞懂软核的固化、启动和MultiBoot实现

冷机启动板卡时,LMX2572锁定时间在2分钟以上,为什么?

如果设计一款桌面款的机器玩具,最吸引人的外观与功能要有哪些?

51单片机(一款国产8位高性能Flash的接近感应单片机XD08M3232体验感)

如何在服务器上调试本地FPGA板卡

人工智能模型公司Anthropic近日推出了一款Claude移动端App

如何挑选一款性价比高的家用路由器

如何设计一款四轮智能小车

对于一款新的Zynq板卡来说,如何开挂启动程序

对于一款新的Zynq板卡来说,如何开挂启动程序

评论