原则:有硬件I2C、SPI时尽量用硬件操作,省去IO模拟繁琐的时序调试。但在内部资源不够时就要用IO模拟总线了。

关于短延时:

模拟时序时是否需要延时要看MCU与device的相对速度。比如I2C如果400K的速率和MCU动辄几十M的速率不再一个量级,肯定要通过延时调整时序;但对于SPI因为其速度很高,甚至有的比单片机的速度还高,这时就没必要延时了。

关于IO模拟的收发函数是否要合并成一个:

对于SPI因为是全双工,所以可以分开,当然也可以合并成一个(发送时不需要返回值,而接收时此时参数是要发送的数据,返回值是要读的值)

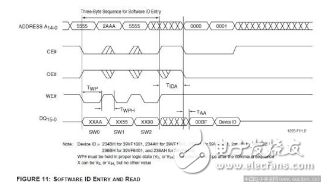

关于在什么跳变沿操作:

比如芯片手册中说到在上升沿采样/锁定(也就是在搞定平之后值必须稳定),那么单个位bit的收发都应该在0->1之间进行操作。

关于时钟极性和时钟相位:

CPOL时钟极性只是说明了空闲时总线的电平状态:CPOL=1表明空闲时时钟是搞定平;否则是低电平。

CPOA时钟相位说明了在第几个跳变沿进行采样,CPOA=0表明在第一个沿进行采样,否则在第二个沿。

-

IO

+关注

关注

0文章

448浏览量

39189 -

时钟

+关注

关注

11文章

1735浏览量

131543 -

SPI

+关注

关注

17文章

1707浏览量

91704

原文标题:关于IO模拟时序(SPI)的注意事项

文章出处:【微信号:mcugeek,微信公众号:MCU开发加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA设计中的时序分析及异步设计注意事项

通用IO结构注意事项是什么

低功耗配置IO的注意事项是什么

胆机使用的注意事项

PIC18Fxx单片机IO设置注意事项!

ADS8528、ADS8548和ADS8568时序注意事项

深度解析IO模拟时序(SPI)的注意事项

深度解析IO模拟时序(SPI)的注意事项

评论