探究当今产业背景和科技潮流中半导体产业所面临的挑战与变革时,不难发现,一个至关重要的转折点已经发生——人工智能(AI)的崛起正以前所未有的力量,对电子设计自动化(EDA)乃至整个半导体产业带来颠覆性的变革。

半导体驱动的产品和系统需求在急剧增长,与此同时,业界始终在追求更小型、更高效、更快速的技术,这些都促使IC工艺与封装技术加速革新,芯片设计复杂度呈指数级增长,进而对传统的设计方法和工具提出了严峻考验。与此同时,全球供应链的复杂性、市场需求的快速变化、半导体工程师人才缺口等,无不在挑战着全球半导体产业的脉动节奏。

正是在这样的背景下,AI凭借其强大的数据处理能力、自我学习能力和优化算法,逐步渗透到EDA和半导体产业的各个环节,从设计优化、制程优化到快速验证等环节,AI不仅能够提高开发效率和精准度,甚至还在生产流程自动化、质量控制等方面展现出巨大潜力。通过赋能EDA领域,AI将为芯片设计带来革命性变化,全面推动半导体产业的变革与升级。

AI如何助力

EDA应对挑战?

电子系统的能力和复杂程度,与其所集成的晶体管数量是成正比的。业界对于单颗芯片可集成的晶体管数量的最新预期是2030年将达到1万亿个;相形之下,半导体工程师和技术人员短缺问题持续存在,据中国半导体行业协会预测,2024年中国行业人才总需求将达到79万人左右,其中人才缺口将达到23万人,芯片设计和制造业人才缺口都在10万人左右。在急剧增加的晶体管数量面前,设计生产力差距成为一个日益严重的问题。

如何通过AI应对这一挑战?

将AI视作一种工具,导入传统EDA软件引擎、流程和工作流中,利用AI实现自动化以及能够验证利用AI获得的结果非常重要。西门子EDA认为,可验证、可追溯和开放性是EDA应用对AI的核心需求。

当前,西门子EDA通过在整个设计流程中引入AI,实现了EDA性能的显著提升,包括减少设计时间、提高验证效率优化测试和良率分析能力,以及增强用户交互体验等方面。

例如可用于复杂SoC系统验证的Veloce硬件仿真加速器平台、IC功能设计方面数字验证的Questa、定制IC验证平台Solido、DFT工具Tessent,以及系统设计的HyperLynx、Xpedition等工具,都可实现不同程度的效率提升。此外,还有用于IC物理验证的Calibre,和进行失效诊断分析的Tessent YieldInsight等。通过这一系列的改进,西门子EDA可帮助客户加快产品上市时间、降低成本,并且提高整体设计质量。

AI赋能的西门子EDA工具

在西门子EDA解决方案中,AI主要用于三个不同重点领域:核心技术、流程优化以及提供可扩展的开放平台,主要用于增强工程师能力、提高工程师的生产力,以及捕捉设计团队内的知识。AI可用于更深入了解IC设计,从而帮助理解问题发生的根本原因,并避免未来可能出现的潜在问题。在这一实践中,AI并非用于取代工程师,而是帮助工程师提高工作效率,并助力实现新的可能性。

AI推动技术进步

一段时间以来,传统AI技术在EDA应用中主要用于帮助处理海量数据,并通过图表分析、强化学习或计算分析等方式,解决新产品导入(NPI)时出现的问题。而新型AI技术包括预测式AI和生成式AI模型技术的引入,开启了更多可能性。

Calibre设计和制造解决方案利用AI为DRC/LVS/PEX/DFM检查、良率分析、可靠性优化以及光刻建模、RET和OPC提供了更快速、更准确的工具,从而加速了从设计到大批量制造的NPI过程。

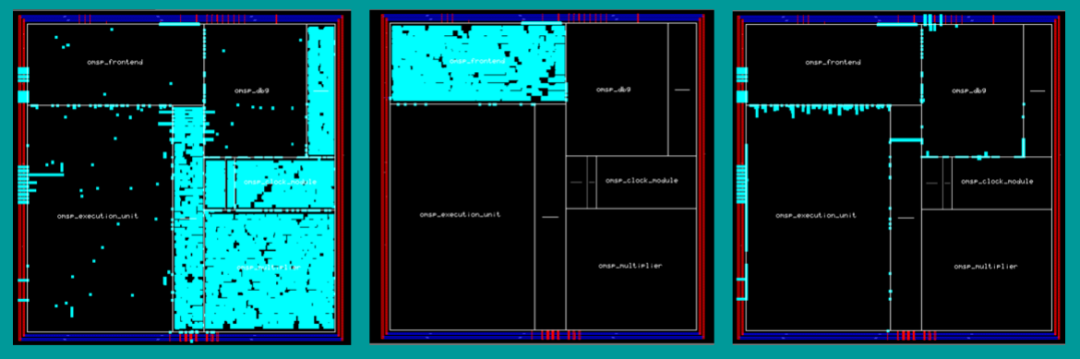

图:Calibre智能IC设计软件加速了复杂SoC设计中错误的验证和调试。

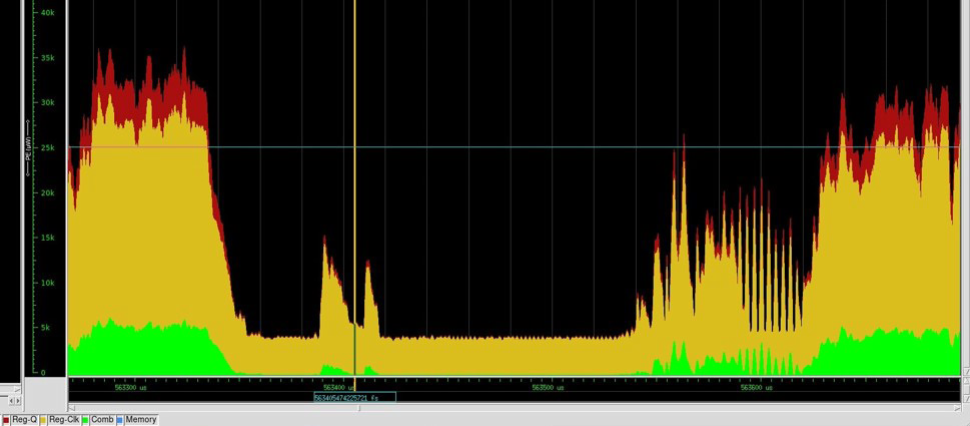

图:Veloce仿真结合AI功耗模型,提供了比传统流程快多个数量级的高精度RTL设计功耗估算。

大语言模型和生成式AI也在改变EDA工具的使用方式。生成式AI更方便工程师保存和分享他们的知识,使提取跨领域信息自动化,以及加快设计创建和系统优化。

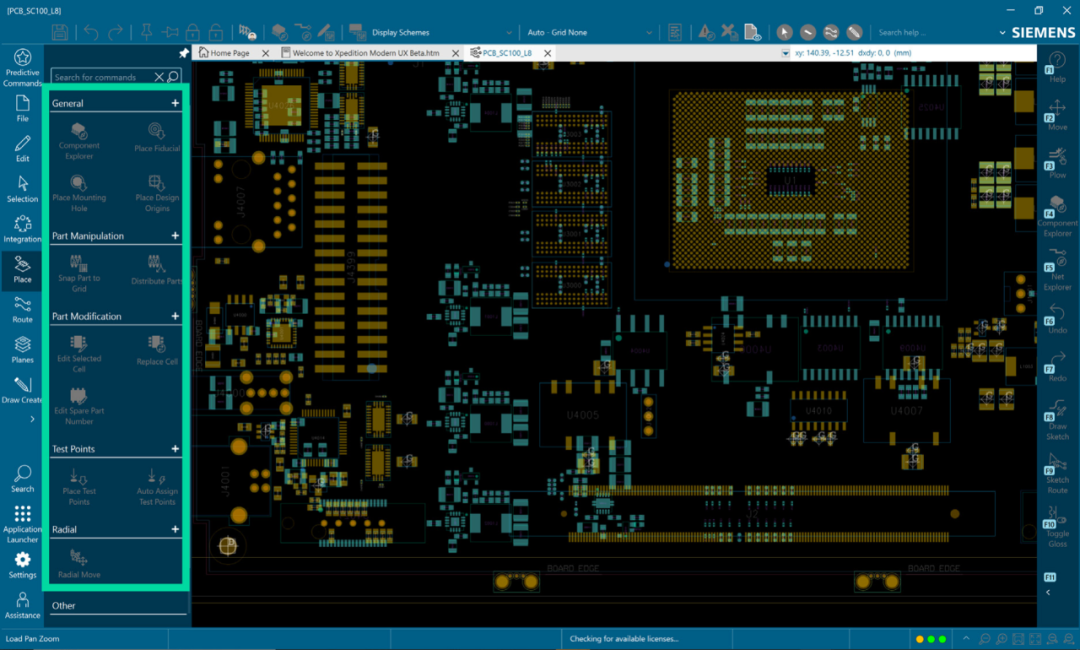

西门子EDA工具中的AI涵盖一系列相互协同的技术,它们使得客户能够打造出更好的芯片和电子系统。例如,设计电路板系统时,Xpedition、HyperLynx和PADS Pro能够借助即时机器学习模型,根据上一个指令来预测下一个指令。

AI赋能的工程师

AI还可在设计优化中充当指引者。所有这些技术都聚焦于为工程师赋能,让他们能够更快速、更高效地工作。例如,AI可以协助进行系统级高阶搜索乃至任务特定搜索,从而加速收敛。无论工程师的专业能力处于何种水平,AI都能为创建半导体设计提供新的见解和自动化能力。

图:AI可通过减少重复、单调的任务来使设计工程师能够积累更多专业经验。

AI简化设计流程

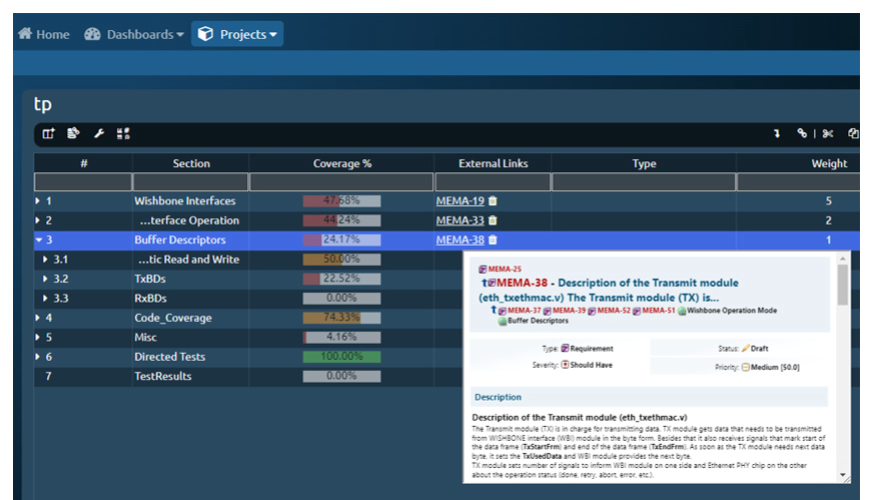

AI可以用于构建新的流程和能力,用于实现对数据的全新理解,使得能够做出以前未知但有价值的权衡,也可以用于更高效地执行EDA领域中的现有任务。例如,Questa Verification IQ数字验证工具套件,使覆盖率收敛速度更快。

图:AI驱动的Questa验证平台能使所需的测试量大大减少,从而缩短收敛时间。

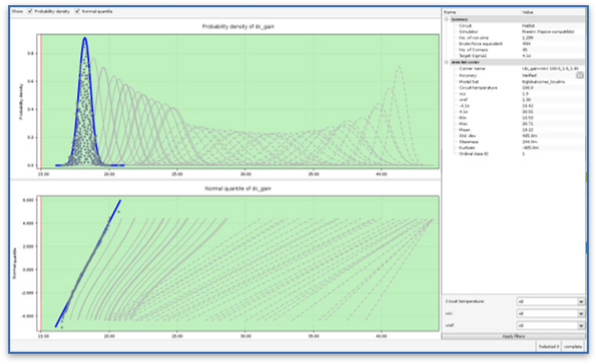

Solido Characterization Suite和Solido Design Environment能够将所需的验证减少几个数量级,同时确保获得质量相同的结果。

图:AI驱动的Solido自定义验证工具能对模拟IC进行更快速、更准确的设计、验证和仿真。

Solido作为首批使用AI技术的一款EDA解决方案,所包括的Solido Simulation Suite、Solido Design Environment、Solido Characterization Suite 和 Solido IP Validation Suite等Solido工具可以配合使用,形成紧密整合、高效的EDA解决方案。

从IC设计到生产的整个过程中,西门子EDA工具通过利用AI实现自动化、规模化与协作,大大提高了整个过程的运行效率。

构建开放安全的AI生态系统

在AI的助力下,芯片设计从概念到生产都在进入一个全新的时代。西门子EDA与合作伙伴正在携手进行大力投入,以期在未来打造一个开放的AI生态系统,让半导体设计人员和制造厂商能够构建可定制、可扩展、可验证的AI工具及优化流程。

在打造开放AI生态的过程中,西门子EDA将数据安全视作重要根基。在西门子EDA看来,数据的质量和安全性至关重要,在提供带有预训练AI模型的工具以处理客户数据时,基于客户数据构建的模型始终由客户自行控制,且并不会在未经许可的情况下利用客户数据来改进模型。

下图可以说明在西门子EDA AI解决方案中,是如何全面保障数据安全的。西门子EDA尽可能通过开放式标准数据格式和API来采集数据,强调数据采集和协同数据库的重要性,并且,在AI/ML模型的预训练、提供安全的设计洞察、以及供应链的优化和管理等多个工作流中,来保护数据和设计安全。

基于这一套完整的、覆盖全部关键要素所搭建起的平台支持,客户可以安全地利用其自有数据继续构建应用层AI,这些数据包括EDA数据、源控制数据、流程数据以及其他一系列内部数据。通过西门子EDA AI平台,客户可将其数据放心地集成到EDA工具中,以提取数据并根据需求进行控制。

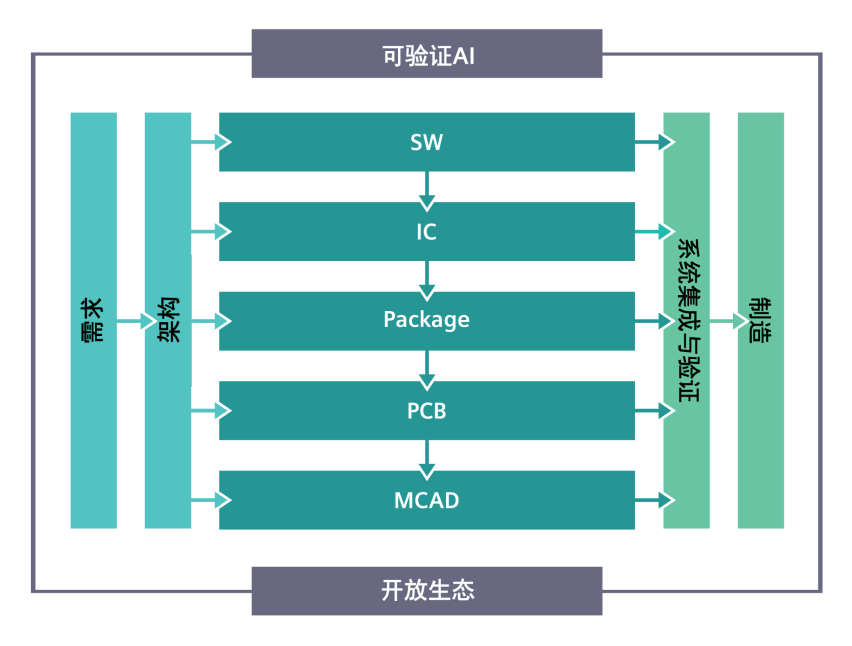

西门子EDA希望从IC设计需求出发,贯穿架构、软件(包括IC、Package、PCB以及MCAD等方面)、系统集成和验证以及制造等全流程,打造一个促进创新、协作和效率的开放式平台,最终构建可信、可验证的AI平台。

展望:半导体全生命周期

进一步提升AI能力

在AI的助力下,从概念到生产的芯片设计正进入一个全新时代。

西门子EDA研发人员正与客户积极合作,不仅要提升半导体设计和生产阶段导入的能力,也要在半导体全生命周期中实现进一步提升。通过与客户密切合作,西门子EDA研发人员和支持团队能够在传统EDA之外,研究来自半导体设计过程的深刻知识与见解,从而致力于减少产品制造所需的时间和资源,同时提升工程设计能力,而这将有助于实现更加全面而深入的优化。

未来,随着AI助推半导体技术集成到全面的数字孪生中,一系列新的功能可望实现:比如实现精确仿真、个性化产品设计、自动优化、半导体供应链优化等等,从而更大程度推动整个行业的进步。

-

半导体

+关注

关注

339文章

31438浏览量

267425 -

西门子

+关注

关注

98文章

3402浏览量

120858 -

eda

+关注

关注

72文章

3157浏览量

184042 -

AI

+关注

关注

91文章

41834浏览量

302983

原文标题:可验证AI开启EDA新时代,引领半导体产业变革

文章出处:【微信号:Mentor明导,微信公众号:西门子EDA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

EDA²侠客岛难题挑战·2025已正式开启

【开源硬件系列04期】AI人工智能技术带给EDA的机遇和挑战(文中含回放+课件)

新思科技发布业界首款全栈式AI驱动型EDA解决方案Synopsys.ai

AI助力国产EDA,挑战与机遇并存

AI如何助力EDA应对挑战

AI如何助力EDA应对挑战

评论