在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,就往往需要提高PCB的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,请介绍在高速(>100MHz)高密度PCB设计中的技巧?

在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。以下提供几个注意的地方:

1.控制走线特性阻抗的连续与匹配。

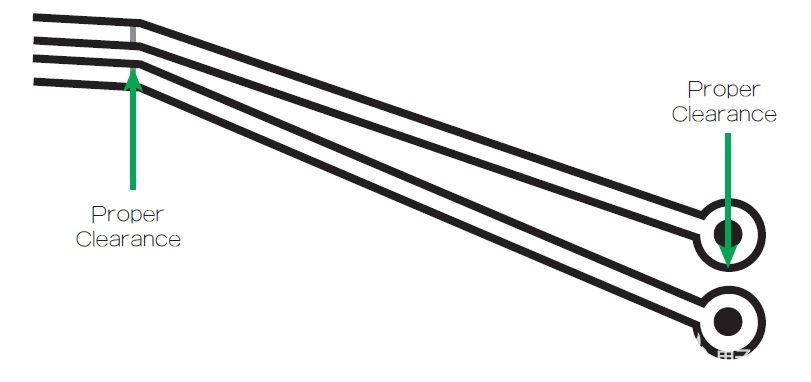

2.走线间距的大小。一般常看到的间距为两倍线宽。可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的最小间距。不同芯片信号的结果可能不同。

3.选择适当的端接方式。

4.避免上下相邻两层的走线方向相同,甚至有走线正好上下重迭在一起,因为这种串扰比同层相邻走线的情形还大。

5.利用盲埋孔(blind/buried via)来增加走线面积。但是PCB板的制作成本会增加。 在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。

除此以外,可以预留差分端接和共模端接,以缓和对时序与信号完整性的影响。

-

pcb

+关注

关注

4319文章

23111浏览量

398313 -

串扰

+关注

关注

4文章

189浏览量

26958

原文标题:【M博士问答】在高速(>100MHz)高密度PCB设计中,对于串扰需要注意什么?

文章出处:【微信号:Mouser-Community,微信公众号:贸泽电子设计圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

在高速(>100MHz)高密度PCB设计时需要注意串扰的几个方面

在高速(>100MHz)高密度PCB设计时需要注意串扰的几个方面

评论