在现代电子系统中,数字电路扮演着至关重要的角色。这些电路处理的是二进制信号,即由逻辑“1”和逻辑“0”组成的信号。这些逻辑状态通常通过电压水平来表示,其中高电平代表逻辑“1”,低电平代表逻辑“0”。

1. 数字信号基础

数字信号是电子系统中用来表示信息的电压或电流的变化。在最简单的形式中,数字信号只有两种状态:高电平和低电平。这些状态对应于二进制数字系统中的“1”和“0”。

1.1 高电平输入

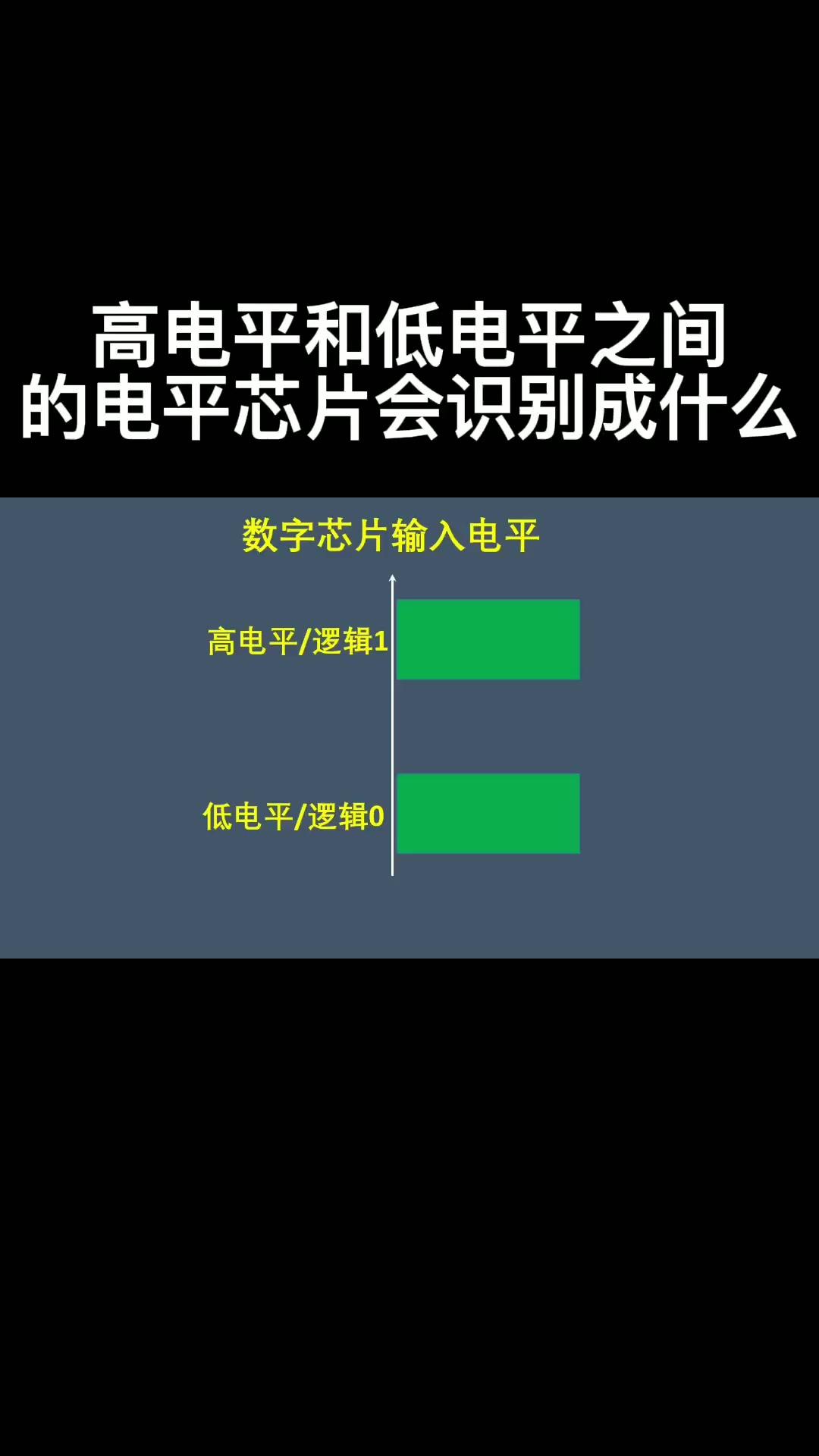

高电平输入是指电路接收到的电压水平高于某个预设的阈值。在数字电路中,高电平通常用来表示逻辑“1”。这个阈值电压通常由电路的设计决定,但常见的标准是5伏特(V)或3.3伏特(V)。

高电平输入在电路中的作用是激活或使能某些功能。例如,在微控制器中,一个高电平输入可能意味着一个特定的引脚被设置为输出高电平,从而驱动一个外部设备。

1.2 低电平输入

与高电平输入相对的是低电平输入,它指的是电路接收到的电压水平低于预设的阈值。在数字电路中,低电平通常用来表示逻辑“0”。这个阈值电压同样由电路的设计决定,但常见的标准是接近0伏特(V)或0.8伏特(V)。

低电平输入在电路中的作用是关闭或禁用某些功能。例如,在一个简单的开关电路中,低电平输入可能意味着电路中的晶体管被关闭,从而切断电流的流动。

2. 电平触发和边沿触发

数字电路可以根据输入信号的变化来响应,这通常涉及到电平触发和边沿触发两种机制。

2.1 电平触发

电平触发是指电路对输入信号的电平变化做出响应。在电平触发的电路中,只要输入信号保持在高电平或低电平状态,输出就会相应地保持在高电平或低电平状态。

电平触发电路的一个常见例子是基本的逻辑门,如与门(AND)和或门(OR)。这些逻辑门的输出状态完全取决于输入信号的电平状态。

2.2 边沿触发

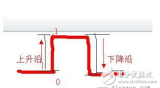

与电平触发不同,边沿触发是指电路对输入信号的电平变化(即从低电平到高电平或从高电平到低电平的跃变)做出响应。在边沿触发的电路中,输出只在输入信号的电平发生变化时改变状态。

边沿触发电路的一个典型例子是触发器,如D触发器和JK触发器。这些触发器的输出状态取决于输入信号的边沿变化,而不是电平的持续状态。

3. 噪声和信号完整性

在实际的电子系统中,信号的完整性可能会受到噪声的影响。噪声可以是电源电压的波动、温度变化、电磁干扰(EMI)或电路本身的不完美。

3.1 噪声对信号的影响

噪声可能会导致信号的电平变化,从而影响电路的逻辑判断。例如,如果噪声导致一个本应为低电平的信号短暂地上升到高电平阈值,电路可能会错误地将这个信号识别为高电平输入。

3.2 信号完整性

为了确保信号的完整性,设计者通常会采取一些措施来减少噪声的影响。这些措施包括使用去耦电容来稳定电源电压、使用屏蔽和接地技术来减少EMI、以及设计具有足够噪声容限的电路。

-

电流

+关注

关注

40文章

6937浏览量

132594 -

二进制

+关注

关注

2文章

796浏览量

41746 -

低电平

+关注

关注

1文章

117浏览量

13325 -

高电平

+关注

关注

6文章

153浏览量

21489

发布评论请先 登录

相关推荐

高电平和低电平是什么意思?区别是什么?

PWM的输入是高电平有效还是低电平有效的?

低电平和高电平的区别

逻辑芯片输入的低电平有效和高电平有效

电子设计(4)高电平、低电平复位电路

单片机检测IO口高电平、低电平、悬空三种状态。

高电平、低电平复位电路

高电平输入和低电平输入是什么意思

高电平输入和低电平输入是什么意思

评论