Altium Designer 24.10.1

发布时间:2024年10月10日

Altium Designer 24.10.1离线包

15天免费试用 Altium Designer

原理图输入改进

支持正常模式下的空子部件

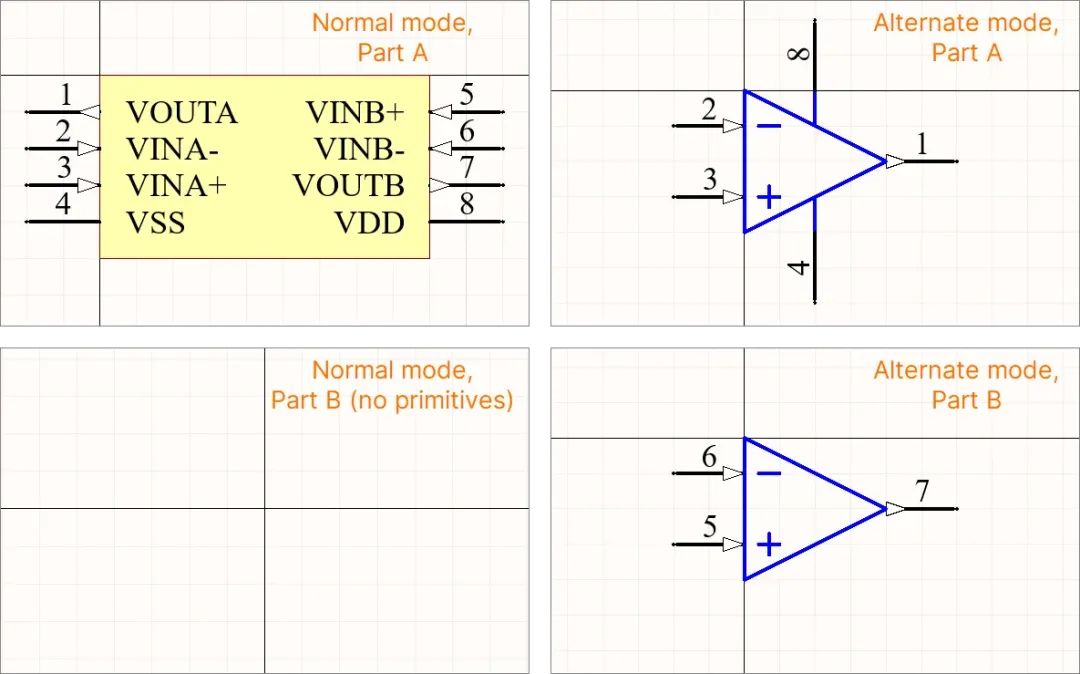

改进了单部件/多部件符号的处理功能,并将适用于Alternate显示模式的相同特性和功能扩展至Normal显示模式。例如,现在可以在Normal显示模式下以单个符号表示元件,而在其Alternate模式下则以两个符号表示,如下图所示。

如果一个多部件元件仅在一个子部件中定义了基元,则当该子部件被放置在原理图图纸上时,无论当前处于何种显示模式下以及无论哪些子部件包含基元(无论是否包含第一个子部件),其位号标识符后缀均将被隐藏。

如果多部件元件在其视图模式(Normal或Alternate模式)下包含空子部件,则在放置过程中这些子部件将被忽略。

如果一个元件包含没有基元的子部件,且这些子部件未被放置在原理图上,则在进行设计确认时无论处于何种显示模式下,元件违规中均不会出现任何Unused子部件。

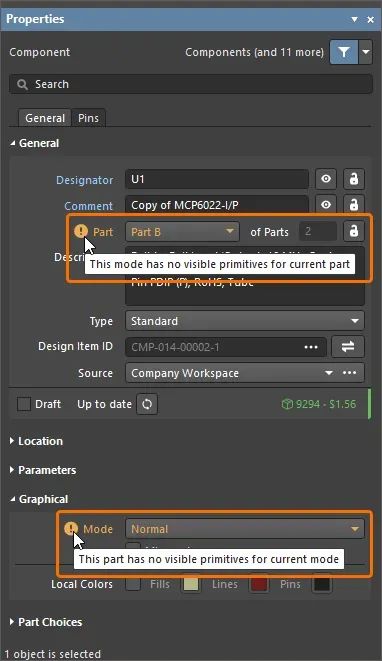

此外,现在还可以将部件或显示模式更改为不含任何基元的模式。当选定空子部件或显示模式时,Properties面板上的相应入口旁边即会显示一个警告图标。

如需了解更多信息,请参阅 Searching for & Placing Components页面。

PCB改进 Wire Bonding(开放测试阶段)

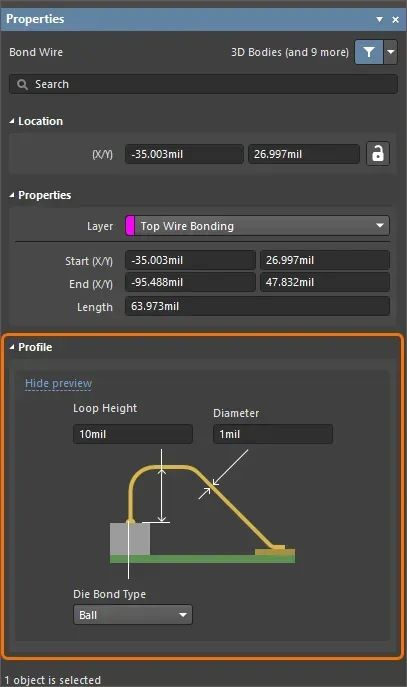

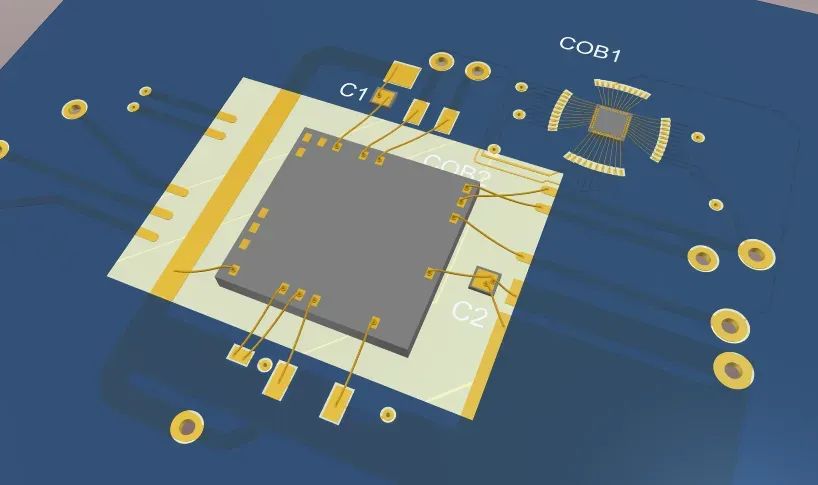

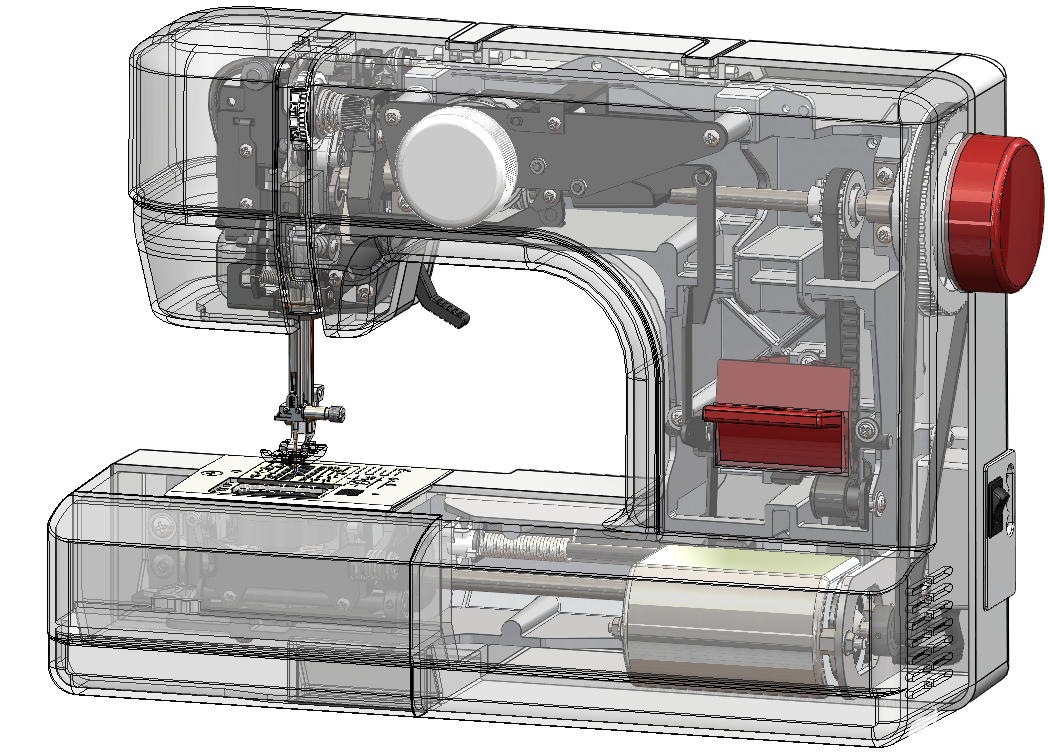

在本次发布中,添加了对使用Wire Bonding和板上芯片(CoB)技术开展混合电路板设计的支持。可通过此功能,使用定义的Die Pads(对应于原理图符号的引脚)创建元件。在将其放置到原理图上并(通过ECO)与PCB同步后,即可使用Bond Wires将其连接到主电路板的常规焊盘(或任何铜层)上。当连接到常规焊盘上时,该焊盘将类似于Bond Finger焊盘。 可以使用作为元件封装组成部分定义的die焊盘、bond finger焊盘和bond wires,定义一个完整的简单封装。

支持在使用预定义Die 元件层对(Top Die / Bottom Die)时,添加Die焊盘。请注意,当将一个Die焊盘放置在挤压3D体(和 Top Die / Bottom Die层)上时,其将被自动放置在该3D体的Overall Height上。

放置(Die焊盘与bond finger焊盘之间,Die焊盘与Die焊盘之间的)bond wires时,可使用预定义的Wire Bonding元件层对(Top Wire Bonding / Bottom Wire Bonding)。请使用Place » Bond Wire命令或者 在Active Bar上,放置bond wire。请使用Properties面板Profile区域中的字段,指定bond wire的Loop Height和Diameter的期望值,以及Die Bond Type (Ball或Wedge)。

在Active Bar上,放置bond wire。请使用Properties面板Profile区域中的字段,指定bond wire的Loop Height和Diameter的期望值,以及Die Bond Type (Ball或Wedge)。

可以将连接bond wires的常规焊盘(bond finger焊盘),与bond wires对齐。为此,请选定bond wires和与之连接的bond finger焊盘,右键单击选定内容,然后从右键单击菜单中选择Pad Actions » Align Bond Finger with Bond Wire命令。

在二维和三维视图中具有wire bonding功能的封装示例。

当使用Chip-on-Board法时,还可以手动放置bond wire,以将芯片的die焊盘连接到主电路板的任何铜层上。Bond wire将继承其源die焊盘的网络。既可以从同一个die焊盘上引出多条Bond wire,亦可以在主电路板的同一铜层上结束多条Bond wire。

具有wire bonding功能的PCB示例。

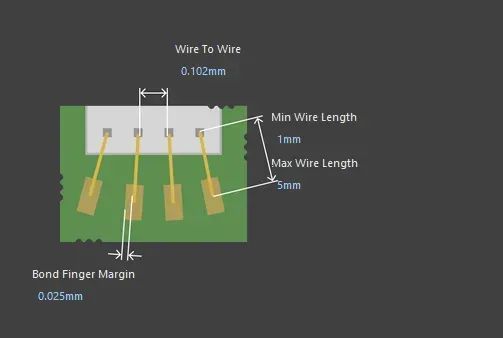

在Routing类别中,添加了一条支持wire bonding的新Wire Bonding 设计规则,当从PCB和PCB Rules and Constraints Editor对话框中进行访问时(使用先前方法进行设计规则定义和管理时),可以在Constraint Manager的 All Rules视图中定义该规则。可以根据该规则,针对相邻bond wires之间的允许距离(Wire To Wire)、 Min和Max Wire Length以及Bond Finger Margin——即,bond wires与其所连接的bond finger焊盘边缘之间的距离/填充,进行约束定义。批量DRC支持Wire Bonding设计规则。电气规则检查(Un-Routed Net和Short Circuit)同样支持Wire Bonding。

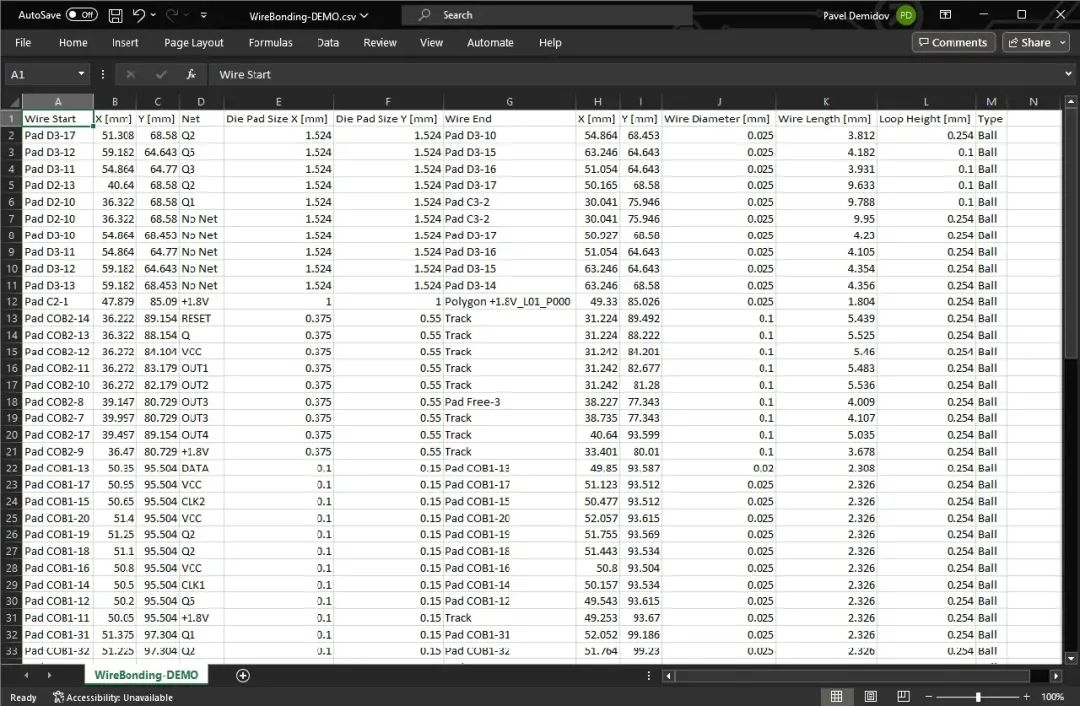

对于制造文档,Draftsman支持在其常规电路板装配视图(用于主Chip-on-Board法)和 元件视图(用于已在封装内完整定义wire bonding‘封装’的情形)中进行wire bonding。在生成常规PCB打印时,还支持wire bonding信息。 能够(以CSV格式)生成一份提供 die 焊盘和bond finger焊盘信息的 wire bonding表报告。请使用输出作业文件Assembly Outputs区域的Wire Bonding Table Report输出,添加该类型的新输出,或者从PCB编辑器的主菜单中选定File » Assembly Outputs » Wire Bonding Table Report命令来生成该报告。

此功能处于Open Beta阶段,且仅在Advanced Settings对话框中启用了PCB.Wirebonding选项时可用。 如需了解更多信息,请参阅Wire Bonding 页面。

差分对相位匹配(开放测试阶段)

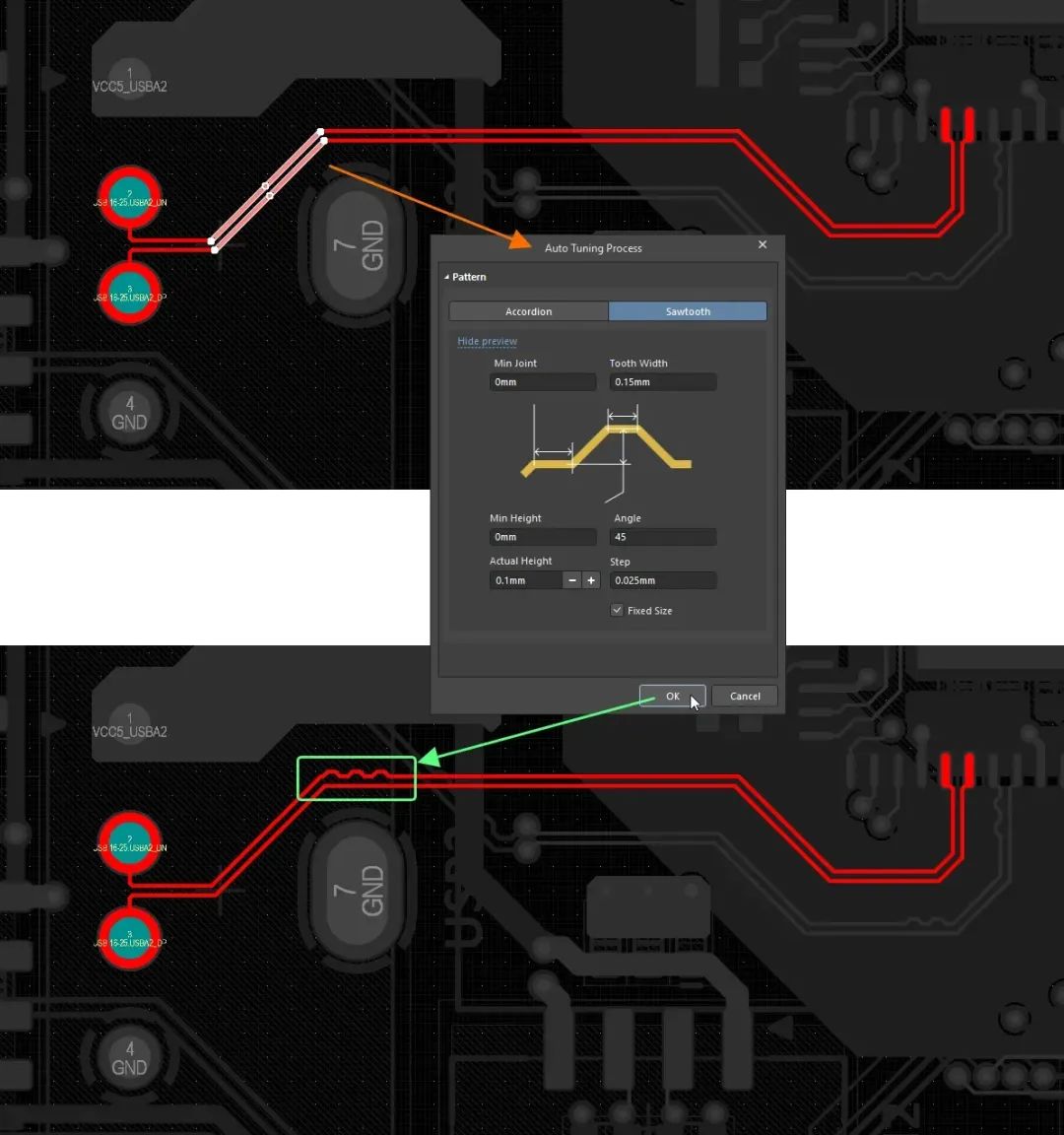

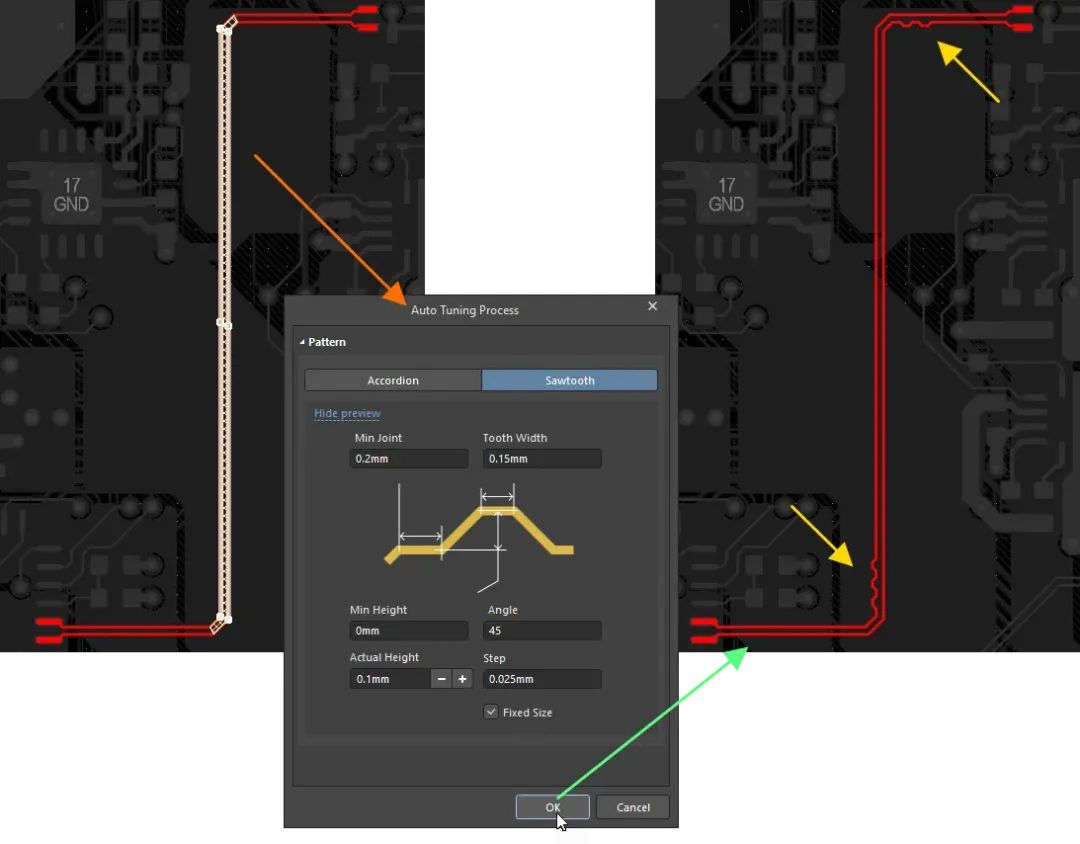

本次发布包括在进行差分对长度自动调整时,启用差分对两侧之间的相位匹配的功能。 为了根据相关Matched Lengths约束在所需差分对两侧之间实施相位匹配,并选定Within Differential Pair Length选项,请选定这些差分对的基元,然后从主菜单中选择Route » Automatic Length Tuning命令。在打开的Auto Tuning Process对话框中,打开一个新的Sawtooth选项卡,然后根据需要配置锯齿模式参数。在该对话框中单击OK键后,锯齿调整模式将被添加到差分对两侧,以均衡其长度。

此功能处于Open Beta阶段,且仅在Advanced Settings对话框中启用了PCB.TraceTuning.PhaseTuning选项时可用。 如需了解更多信息,请参阅Length Tuning页面。

差分对动态相位匹配(开放测试阶段)

本次发布提供了针对差分对动态相位匹配的支持,以确保顺利进行高速PCB设计。为了能够以最高效率进行差分信号传输,需要进行差分对静态相位匹配(均衡差分对两侧的长度)和动态相位匹配(沿着差分对的整个长度进行相位匹配)。

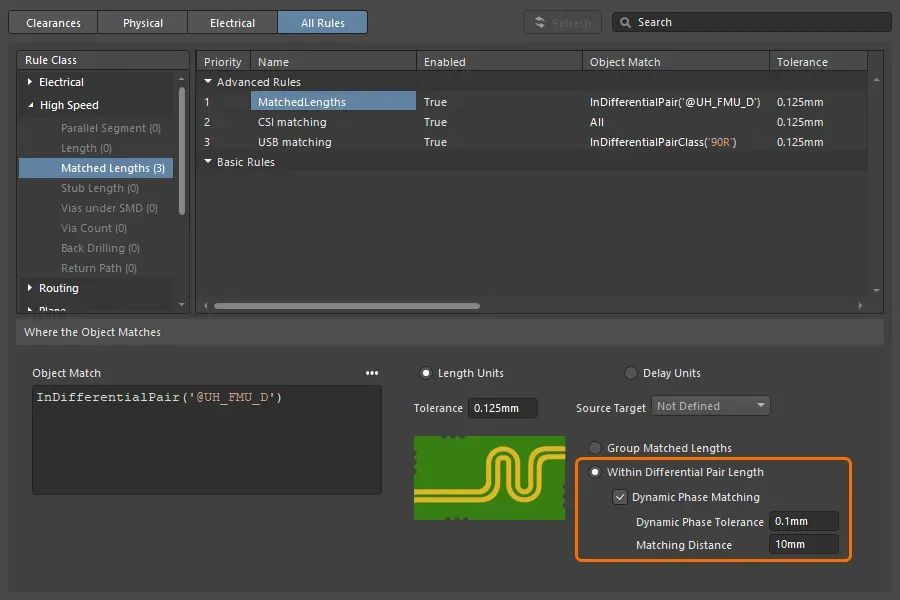

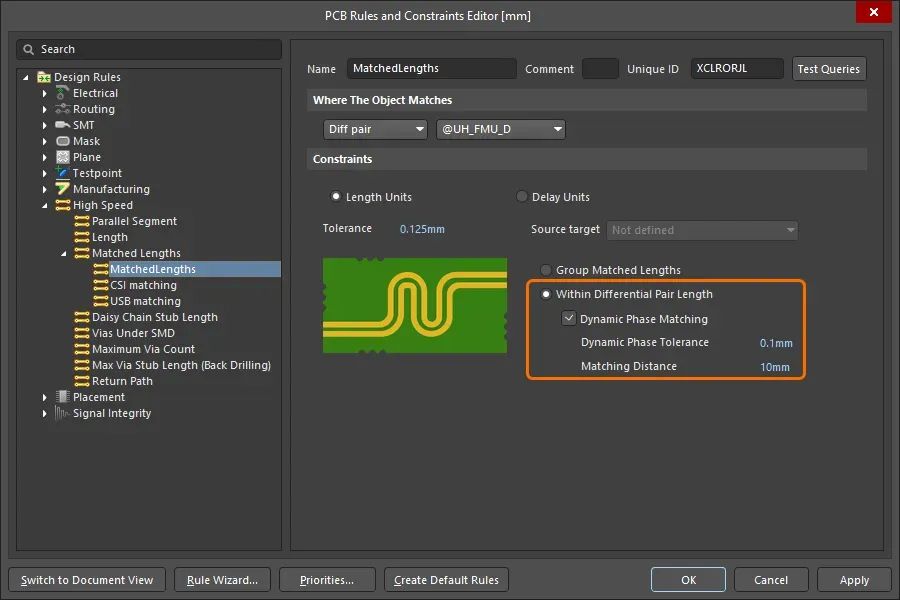

实施新的动态相位匹配约束和相位补偿自动调整后,即可避免耗时的相位失配检测和消除。 扩展后,Matched Length设计规则具备了指定动态相位匹配约束的功能。选定Within Differential Pair Length选项后,即会出现一个新的Dynamic Phase Matching复选框。可以在启用该复选框后,定义以下约束:

Dynamic Phase Tolerance / Dynamic Phase Delay Tolerance – 即,差分对内线路之间的允许相位失配程度,超过该失配程度即需进行补偿。

Matching Distance – 超出公差后必须进行补偿的距离。

在规则中选定Length Units或Delay Units后,即可以毫米或皮秒为单位对上述约束进行定义。 Constraint Manager的All Rules视图(从PCB中进行访问)和PCB Rules and Constraints Editor 对话框(使用先前方法进行设计规则定义和管理时)均支持此项增强规则。

在Constraint Manager中配置的动态相位匹配约束

在PCB Rules and Constraints Editor对话框中配置的动态相位匹配约束

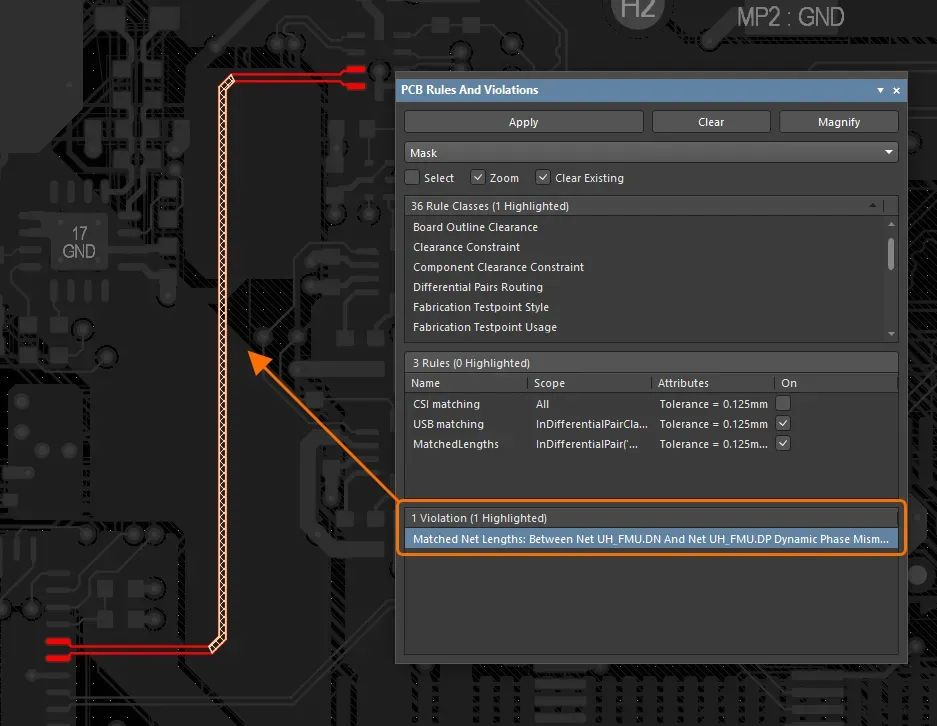

将在设计区内的相应导线上,以阴影模式标记检测到的规则违规(阴影将从检测到的相位失配点——即超出定义公差处开始)。

可以使用Automatic Length Tuning工具,消除动态相位匹配的违规。选定所需差分对(差分对的任何线路),然后从主菜单中选择Route » Automatic Length Tuning命令。在打开的Auto Tuning Process对话框的Sawtooth选项卡上,根据需要设置相位匹配参数,然后单击OK键,以添加进行差分对动态相位匹配所需的锯齿模式。请注意,需要考虑已布线差分对两端焊盘的电气类型,因此如果指定了源/负载,则需要通过沿着差分对向适当的方向移动来进行调整。

此功能处于Open Beta阶段,且仅在Advanced Settings对话框中启用了PCB.Rules.DiffpairPhaseMatching选项时可用。 如需了解更多信息,请参阅High Speed Rule Types页面。

布线拓扑结构DRC支持(开放测试阶段)

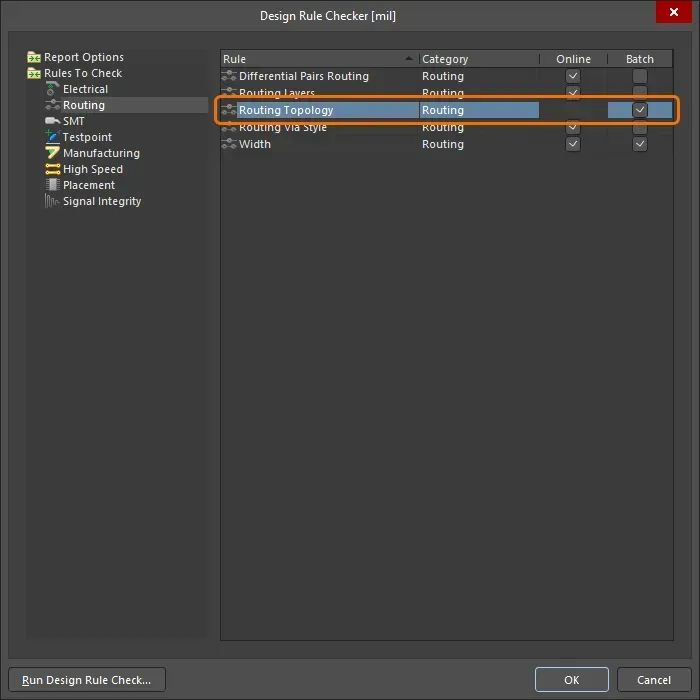

现在可以在Batch DRC过程中,检查使用From-Tos定义的自定义拓扑结构的实现情况。请在Design Rule Checker对话框(Tools » Design Rule Check)中,启用Routing Topology设计规则类型的Batch选项,以进行违规检测。

如果From-To的焊盘之间存在电气连接,且最短路径中包含该网络的至少一个其他焊盘,则会检测到违规。

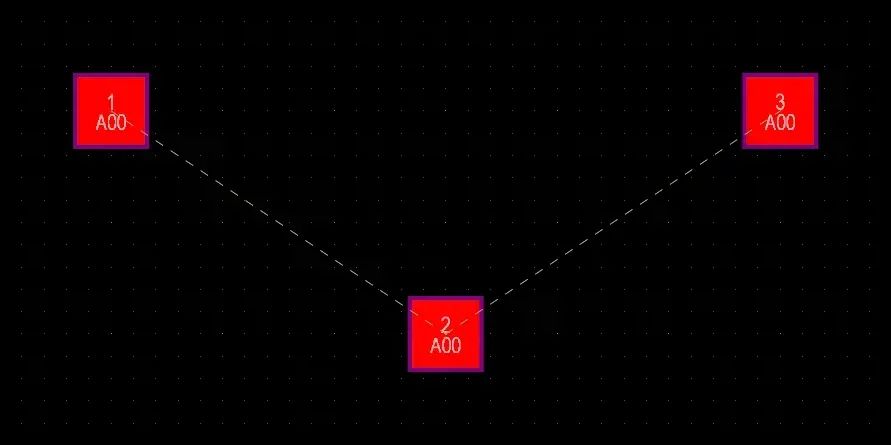

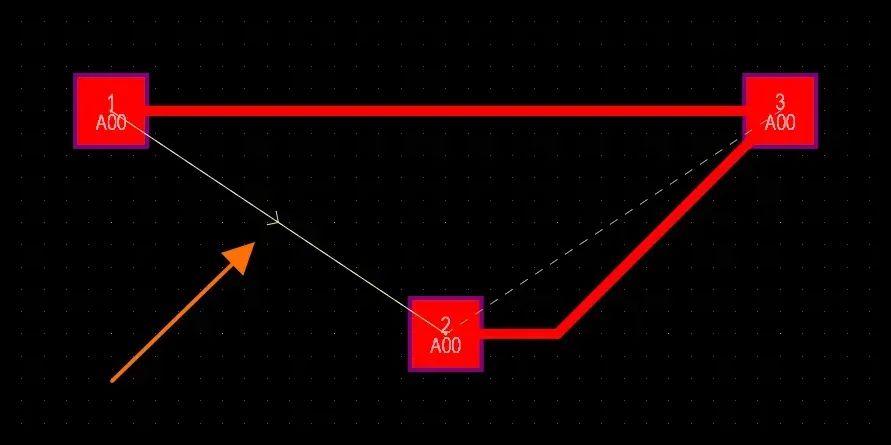

在三个焊盘之间创建两个From-Tos – 即,焊盘1与焊盘2之间以及焊盘2与焊盘3之间

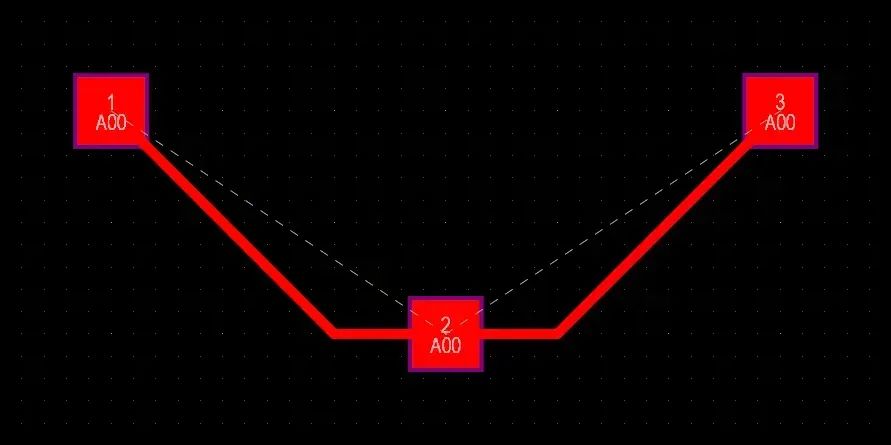

根据From-Tos的配置创建布线 - 焊盘1与焊盘2之间以及焊盘2与焊盘3之间均进行了布线。未检测到涉及Routing Topology规则的任何违规。

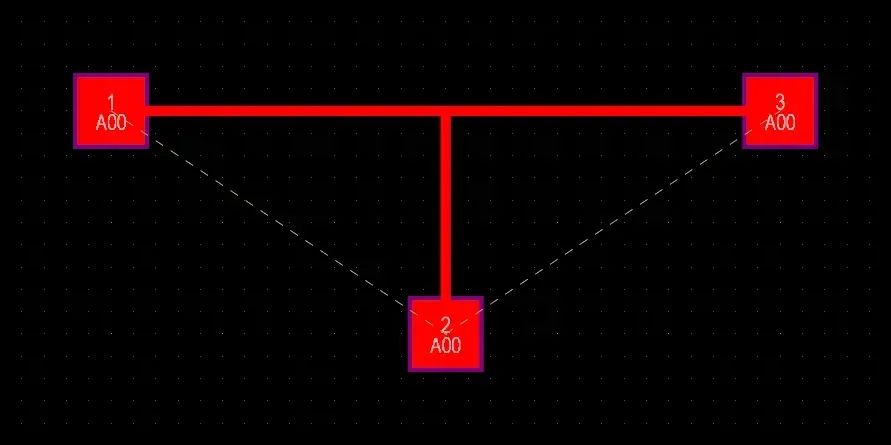

以T型分支方式创建布线。根据From-To的配置,路径中不存在任何额外焊盘,因此不会检测到涉及Routing Topology规则的任何违规。

在焊盘1与焊盘3之间以及焊盘2与焊盘3创建布线。该布线不会与From-To配置进行匹配,因为在焊盘1与焊盘2之间的路径上存在一个额外焊盘3,因此会在焊盘1与焊盘2之间的From-To上检测一条到涉及Routing Topology规则的违规。

对于包含大量焊盘(超过20个)或基元(超过1024个)的网络,不会检测到违规。 此功能处于Open Beta阶段,且仅在Advanced Settings对话框中启用了PCB.Rules.CheckRoutingTopology选项时可用。 如需了解更多信息,请参阅Understanding Connectivity on Your PCB 页面。

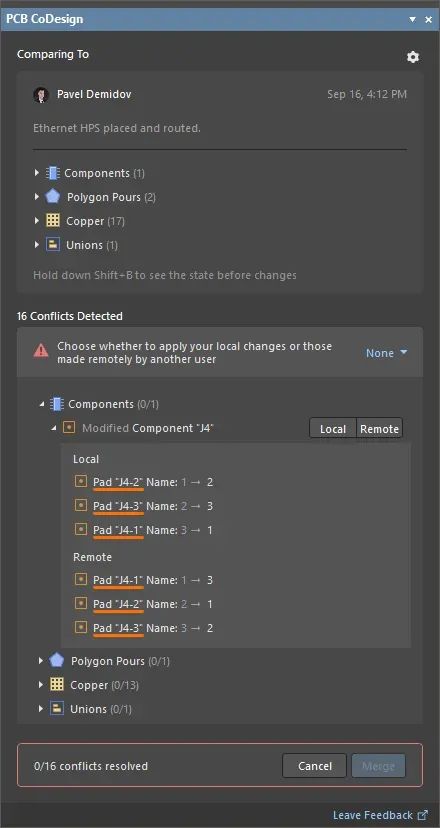

PCB CoDesign改进 显示存在冲突的基元名称

当检测到组对象的基元之间存在冲突时,现在会在PCB CoDesign面板的冲突列表中显示这些基元的名称。如下图所示,将在基元属性之前显示组对象(元件焊盘)内存在冲突的基元名称。

如需了解更多信息,请参阅PCB CoDesign 页面。

合并对象属性

当从两侧更改相同对象属性且属性值内不存在冲突时,这些更改将不再产生冲突,并且可以进行合并,从而显著减少对象冲突数量。

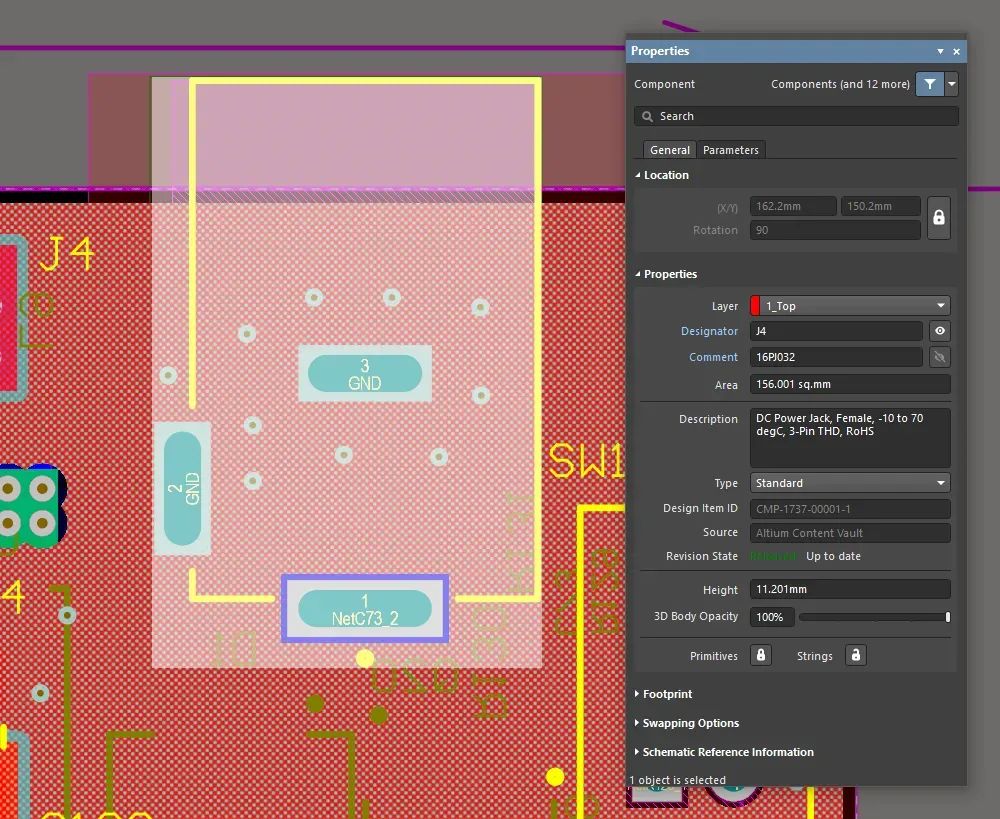

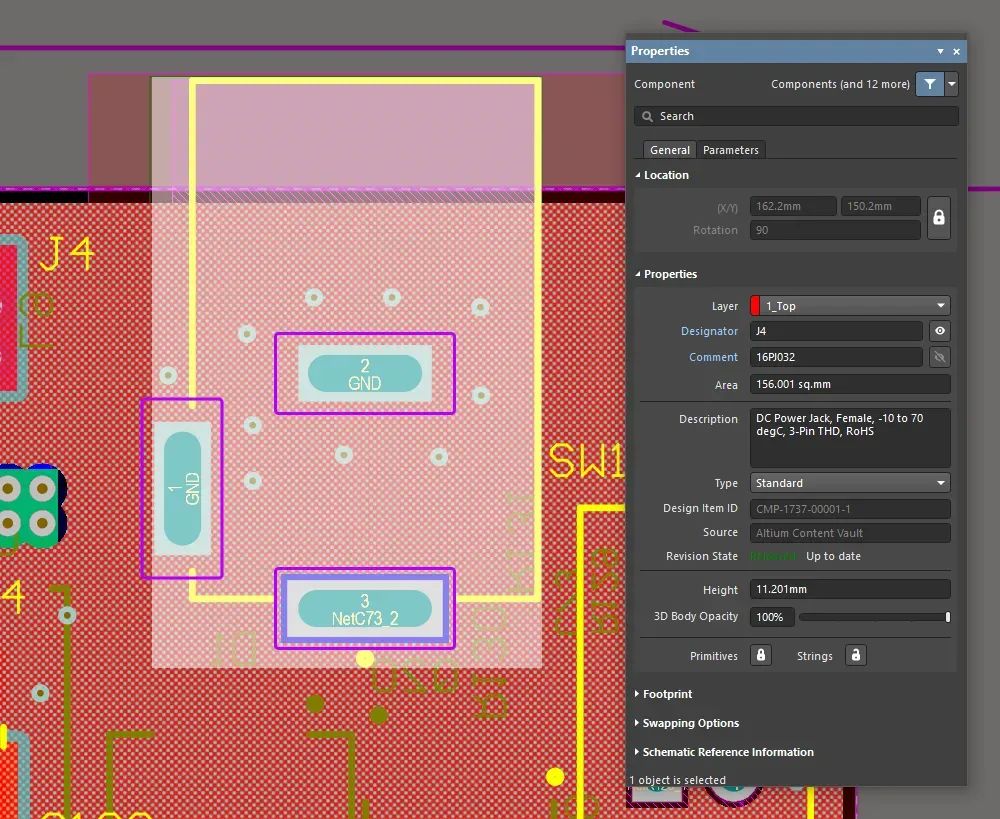

此处显示了PCB文档基础版本中元件J4的PCB面积和属性。

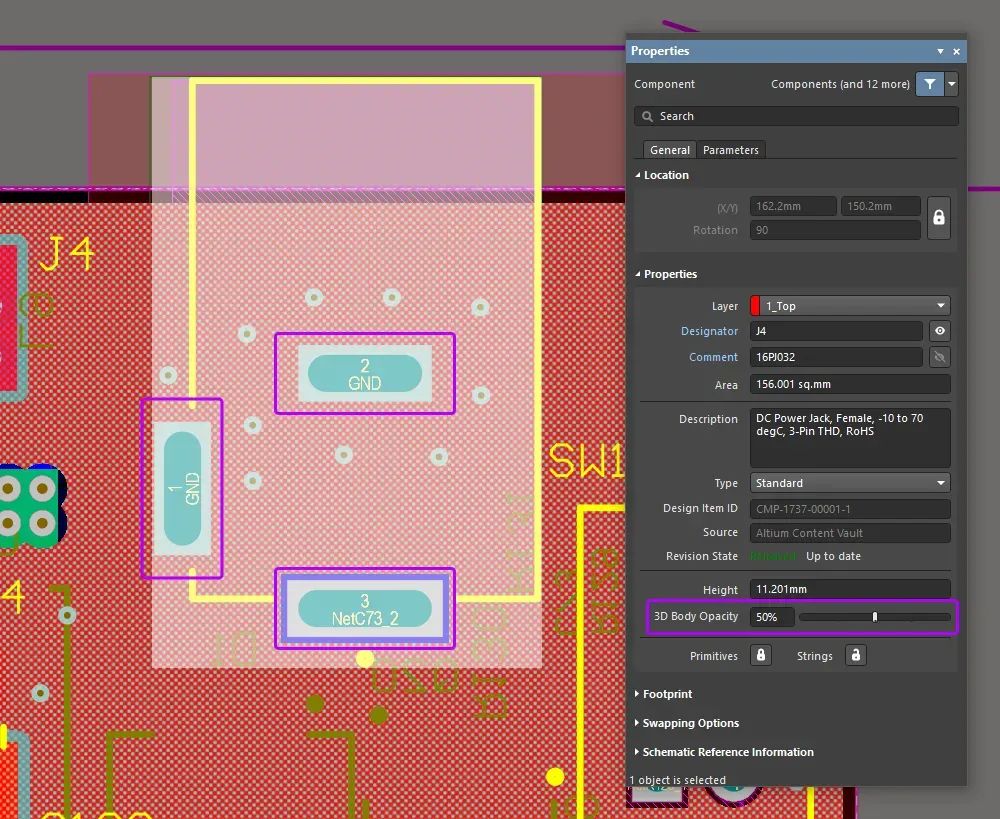

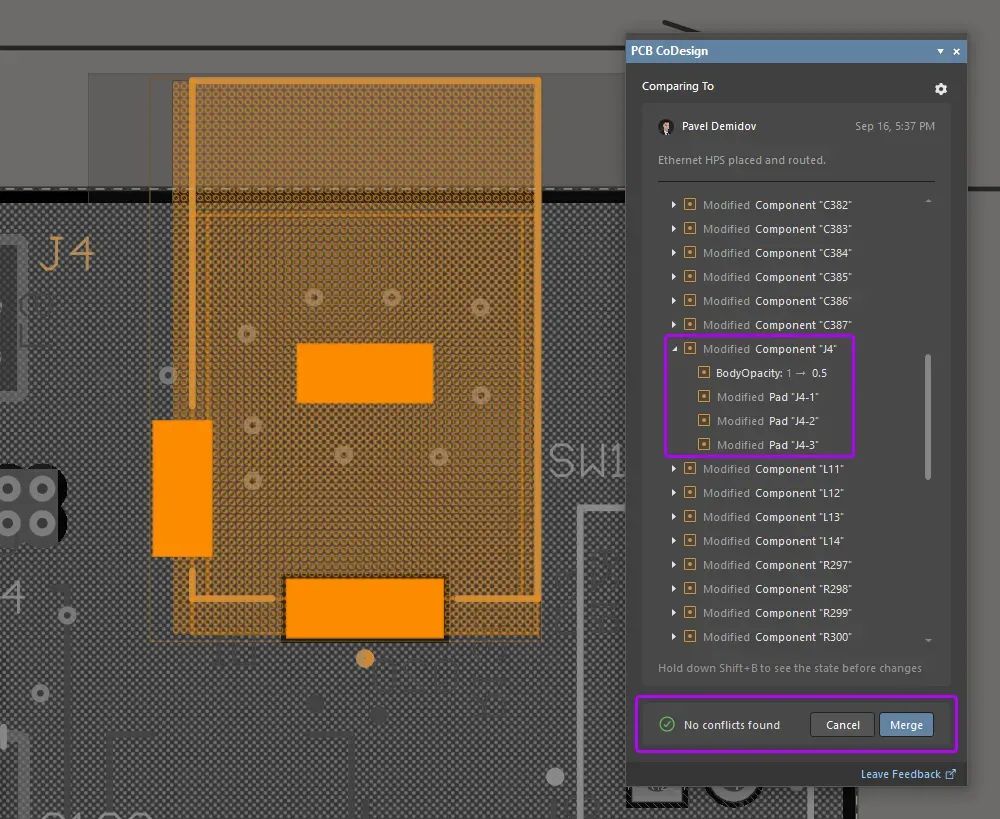

在PCB的远程版本中,更新了J4的3D体透明度和焊盘编号。

在PCB的本地工作副本中,以与远程版本相同的方式更新了J4的焊盘编号。

使用PCB CoDesigner面板进行比较后,J4中的更改不会引起冲突。这些更改可以合并到PCB的本地副本中。

如需了解更多信息,请参阅PCB CoDesign页面。

约束管理器改进 迁移至Constraint Manager的功能(开放测试阶段)

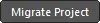

本次发布中包括从PCB Rules and Constraints Editor对话框一次性单向迁移到Constraint Manager的功能。 请使用PCB和原理图编辑器主菜单中的Design » Migrate Project to Constraint Manager Flow命令。此时将打开Migration Required对话框,提示即将进行迁移,且在单击该 按钮后将无法撤消迁移。PCB设计规则和原理图指令均将转移到Constraint Manager中的相应约束中。顺利完成迁移后,将(在进行迁移时编辑器处于活动状态的上下文中)打开Constraint Manager。

按钮后将无法撤消迁移。PCB设计规则和原理图指令均将转移到Constraint Manager中的相应约束中。顺利完成迁移后,将(在进行迁移时编辑器处于活动状态的上下文中)打开Constraint Manager。

如果在PCB Rules and Constraints Editor对话框中尚不存在具有默认范围的设计规则(例如,不存在范围为All的Width规则),则将在进行迁移时在Constraint Manager中创建该规则。 此功能处于Open Beta阶段,且仅在Advanced Settings对话框中启用了ConstraintManager.ProjectMigrationWizard选项时可用。 如需了解更多信息,请参阅Defining Design Requirements Using the Constraint Manager页面。

指令改进

添加、更新和删除已导入指令的约束 对于已导入指令,现在可以使用Properties面板为其添加、更新和删除约束。

如需在Constraint Manager中对数据进行更改,请在从原理图侧进行访问时,单击Constraint Manager右上角的 按钮。 如需了解更多信息,请参阅Defining Design Requirements Using the Constraint Manager页面。

按钮。 如需了解更多信息,请参阅Defining Design Requirements Using the Constraint Manager页面。

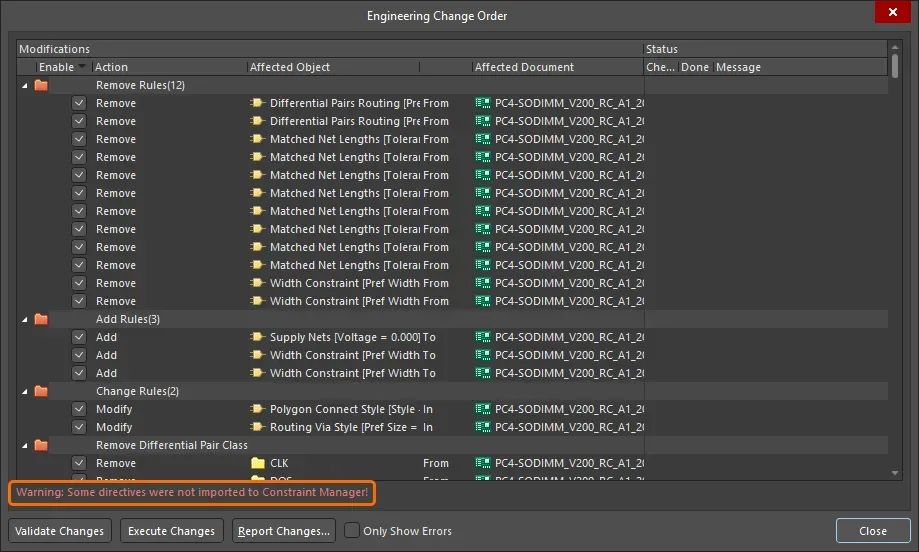

ECO内的差异警告

如果在通过制定ECO将更改从原理图传递到PCB时,原理图上存在先前未导入的指令,则会显示警告。

如需了解更多信息,请参阅Defining Design Requirements Using the Constraint Manager页面。

线束设计改进

导线的自动分组

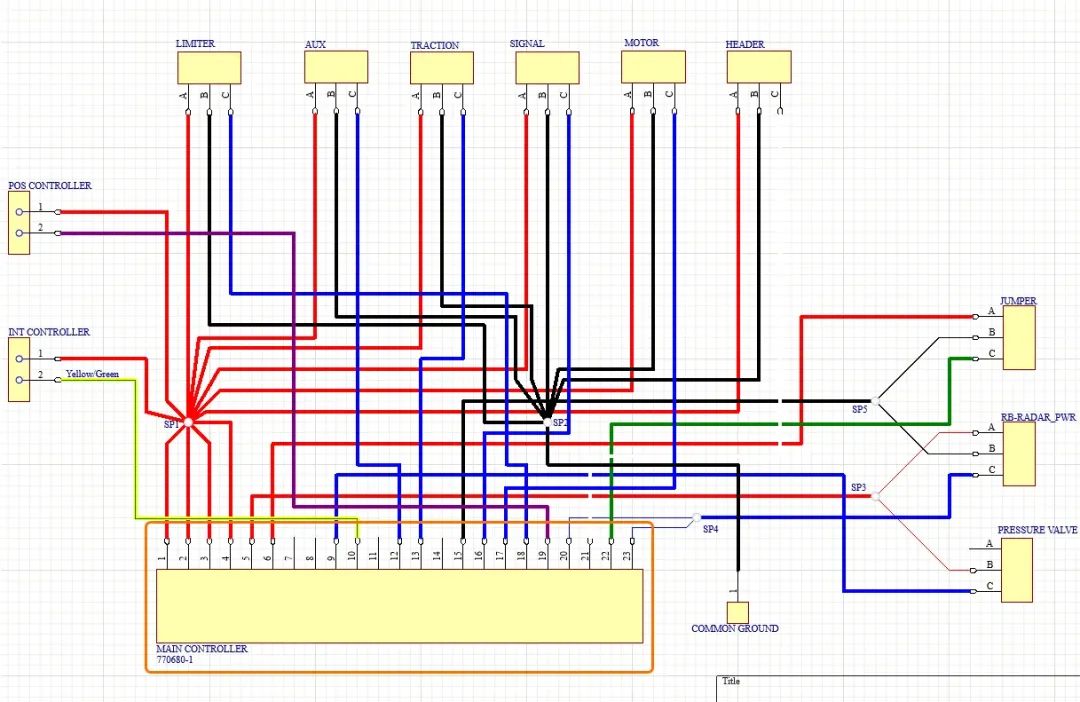

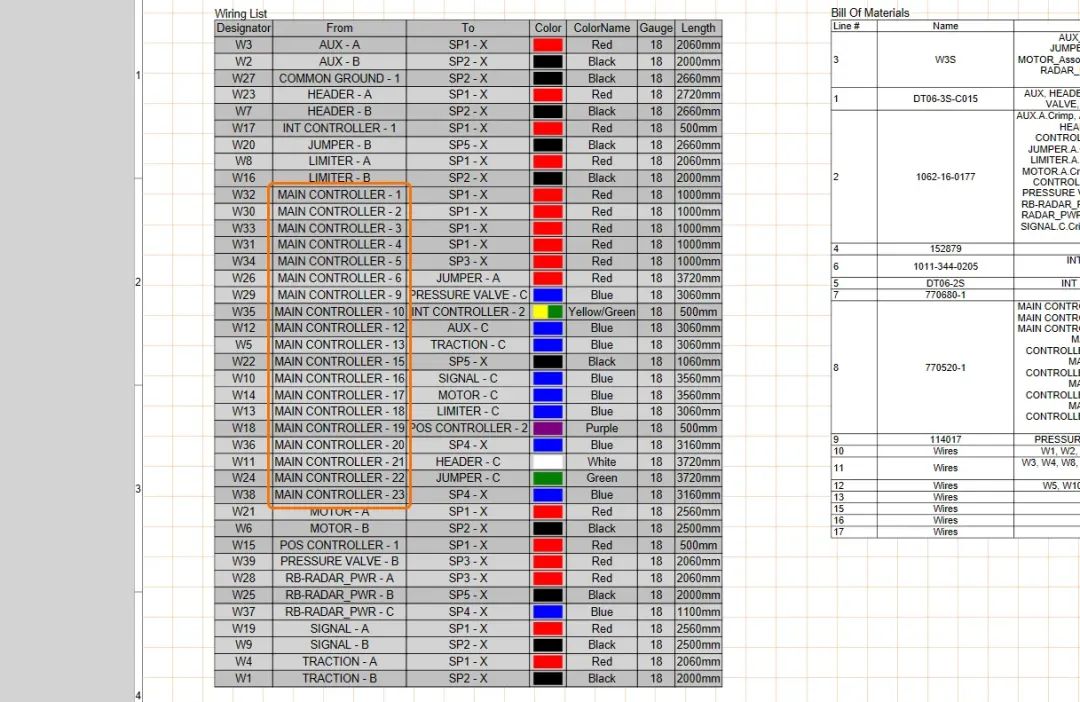

对于Bulkhead Connector(具有最多型腔的连接器),将针对线束制造文档(*.HarDwf)内的接线列表进行自动分组,以确保在From列中正确分组其所有型腔。

在此设计中,由于元件MAIN CONTROLLER具有最多型腔,因此其被视为Bulkhead Connector。

在制造图中,MAIN CONTROLLER的所有型腔均将在From列中进行分组。

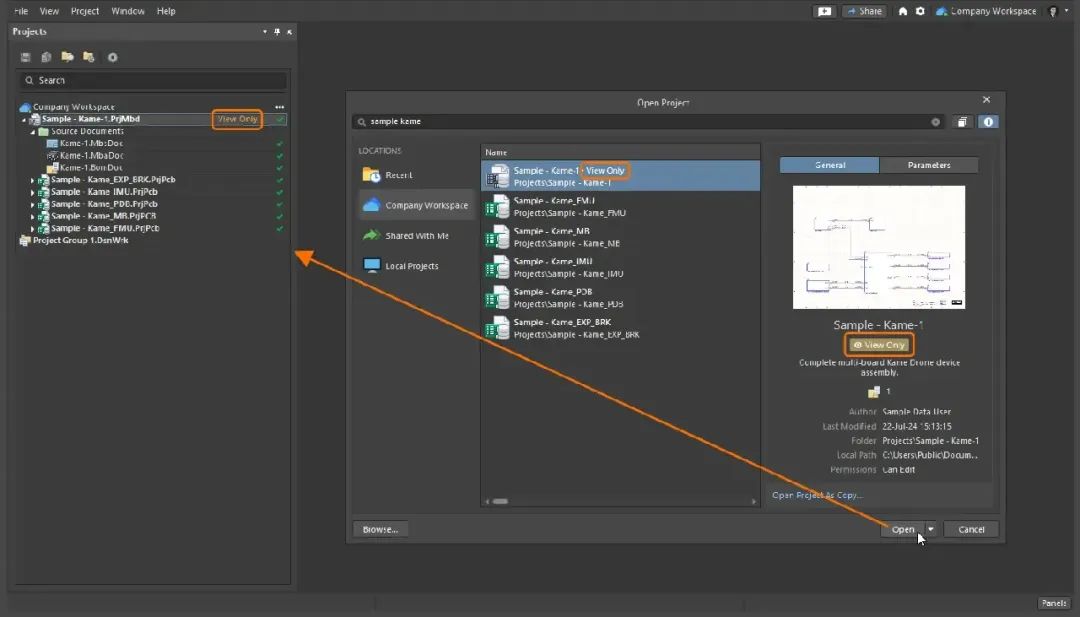

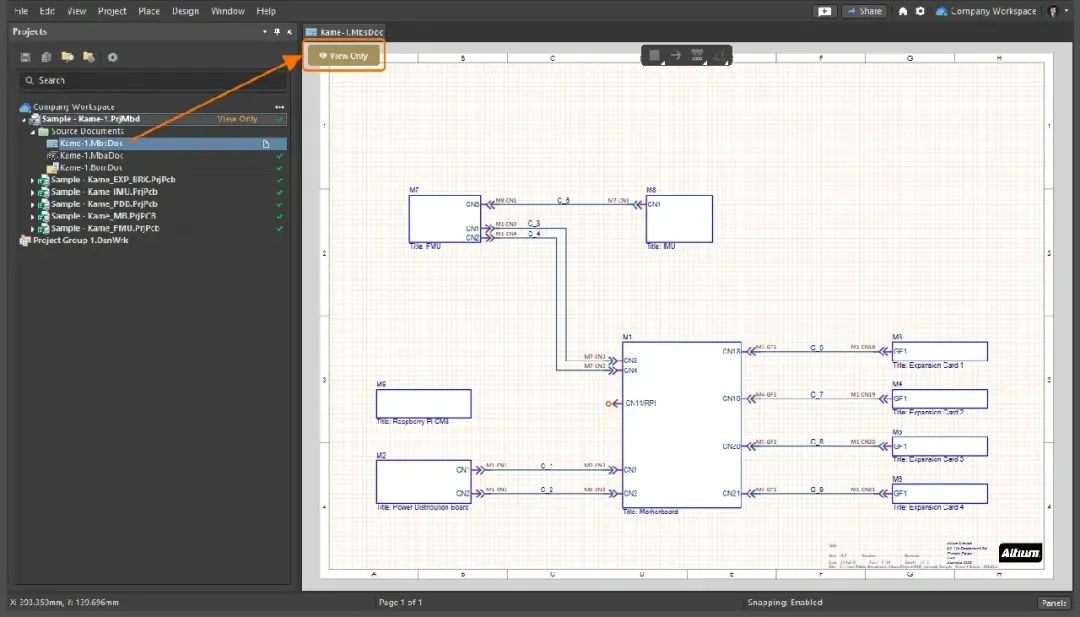

平台改进 线束和多板设计的仅供查看模式(开放测试阶段)

针对Harness和Multi-board项目及其相关文档,引入了仅供查看模式。将其引入后,现在可以查看和探索以前可能无法访问的功能,并与处理上述类型项目的同事进行协作。 在仅供查看模式下,不得对项目和文档进行更新,亦不得对其进行访问。当在仅供查看模式下打开某个项目时,Projects面板将显示View Only,如下图所示。

Multi-board项目的仅供查看模式示例。该项目将在Open Project对话框和Projects面板中被标记为View Only。

当打开项目的源文档时(如此处Multi-board原理图文档所示),其同样会被标记为View Only,因此该文档无法进行修改。

尽管您无法修改任何内容,但可以生成PDF等源文档输出以及来自关联OutJobs的已定义输出。

此功能处于Open Beta阶段,且仅在Advanced Settings对话框中启用了System.ViewOnlyMode.Support选项时可用。 如需了解更多信息,请参阅Designing with Multiple PCBs和Harness Design 页面。

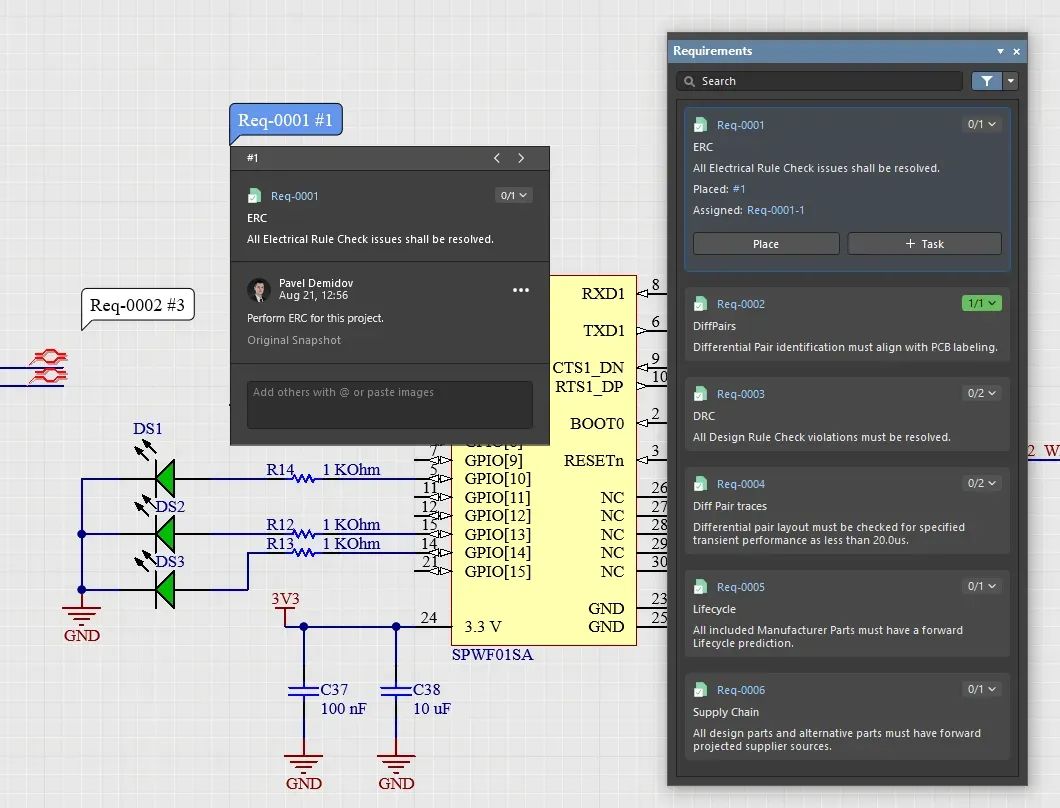

数据管理改进 要求管理(开放测试阶段)

本次发布中针对存储在连接的Altium 365 Workspace中的PCB设计项目,提供了通过Requirements and Systems Portal处理已定义系统要求的功能。后者是一种高级工程管理应用程序,用于在系统设计开发阶段确保规格和性能的合规性。

当针对Altium 365 Workspace启用时,Requirements and Systems Portal将通过交换设计数据和正式的Requirement实例,与PCB设计项目进行集成。可以将在Requirements and Systems Portal中创建的系统要求,作为活动实例放置在设计文档中,然后作为任务进行引用,并最终将其标记为已验证状态,以确认该要求的合规性。

在Altium Designer中,将通过Requirements 面板进行要求管理。可以将已放置的要求,实时提供给对文档拥有共享访问权限的合作用户,并将其保存到独立于项目的Workspace,而不以任何方式更改其组成文档。

此功能处于Open Beta阶段,且仅在Advanced Settings对话框中启用了EDMS.Requirements选项时可用。

如需了解更多信息,请参阅Working with Requirements页面。

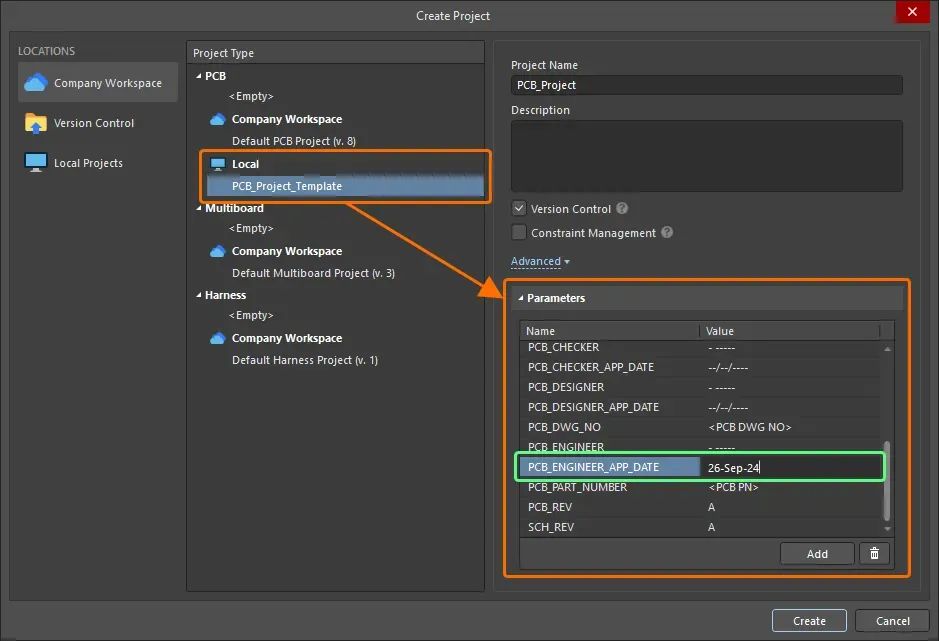

从本地模板中更改项目参数的功能

在使用Create Project对话框(File » New » Project)创建新项目时,现在可以更改或删除选定的本地项目模板的参数(名称和/或值)。

如需了解更多信息,请参阅Creating Projects and Documents页面。

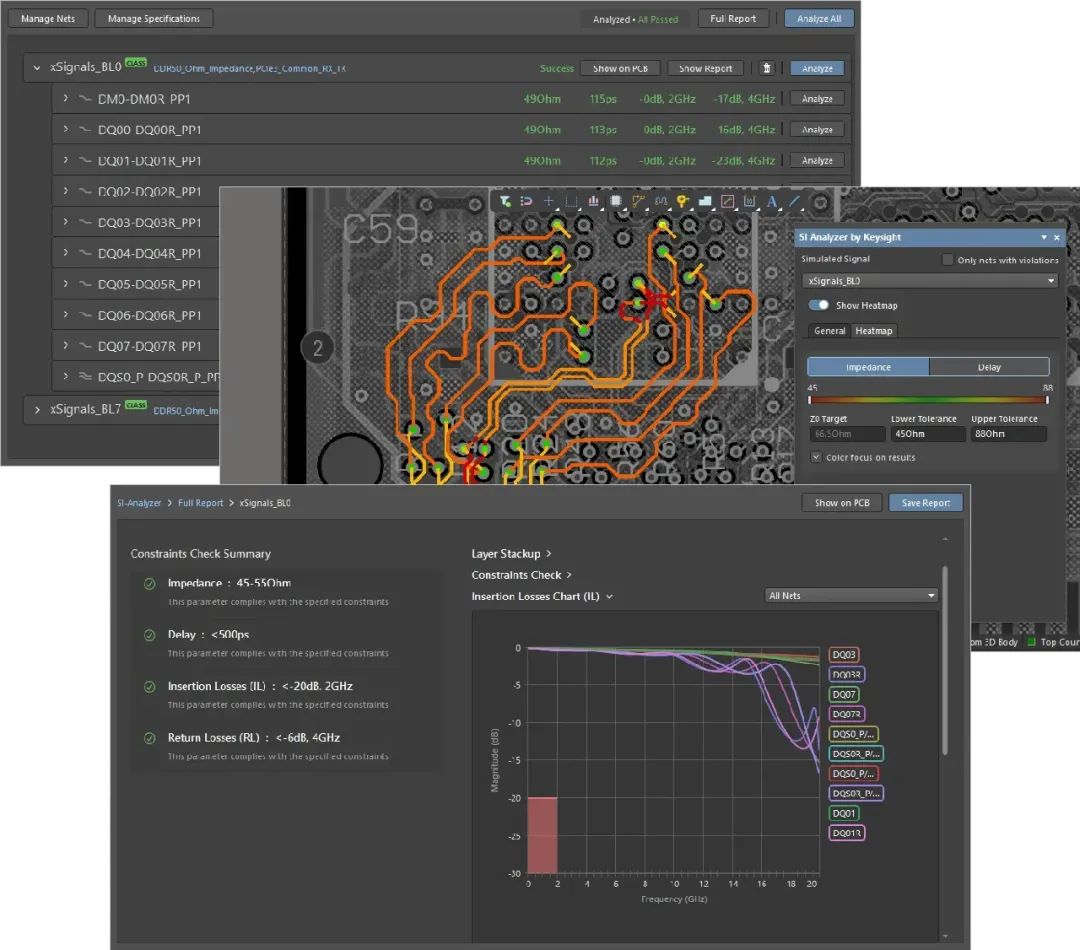

SI Analyzer by Keysight(开放测试阶段)

越来越多的现代电子设备采用了高速PCB设计,而信号速度亦随着技术的发展而不断提升(DDR6为17 GHz,而QSFP++则为400 Gbps)。因此,确保信号完整性(SI)成为高速设计中的一个关键步骤。如果无法满足接口开发人员的要求,则很可能会在后续设计阶段引起制造和性能问题。

为了向PCB设计人员提供信号完整性分析工具,我们现在推出了一种新的解决方案 – SI Analyzer by Keysight。Keysight SI Analyzer将作为软件扩展提供,并且可以直接在Altium Designer环境中使用,以确保能够在完成布局后针对最重要的高速设计参数进行一系列的SI检查:

Impedance

Delay

Insertion Losses (IL)

Return Losses (RL)

此功能处于Open Beta阶段,且仅在安装了SI Analyzer by Keysight扩展时可用。只要持有有效的Altium Designer许可证,即可创建新的分析文档,添加/配置网络以进行分析,以及查看现有SI分析结果和生成SI分析报告。如需进行新的SI分析,则需要获取有效的Signal Analyzer by Keysight许可证。如果在运行新的SI分析时尚未获取Signal Analyzer by Keysight许可证,则可以使用打开的对话框申请14天免费试用。 如需了解更多信息,请参阅SI Analyzer by Keysight页面。

Altium Designer 24.10中完全公开的功能

以下功能现已在本次发布中正式公开:

焊盘孔间距检查改进 – 自24.1版开始提供

封装镜像阻止 – 自24.5版开始提供

更多版本发布说明

-

原理图

+关注

关注

1305文章

6368浏览量

235793 -

altium

+关注

关注

47文章

952浏览量

118492 -

元件

+关注

关注

4文章

956浏览量

36889 -

Designer

+关注

关注

0文章

124浏览量

35933

原文标题:Altium Designer 24.10.1 版本发布,新功能说明

文章出处:【微信号:AltiumChina,微信公众号:Altium】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Altium Designer 24.7.2版本新功能图解说明

原创Altium Designer 17全程安装及新功能视频教程

无私分享,Altium Designer 18 最新18.1.7版本

Altium Designer 20 新功能官方直播

Altium Designer 6.3 新功能教程

Altium Designer 6.8的新功能介绍

altium_designer_16.1.11_软件下载

Altium Designer 21版本的操作界面环境

altium designer哪个版本稳定

Altium Designer 25.2.1版本新功能解析

Altium Designer 24.10.1版本新功能解析

Altium Designer 24.10.1版本新功能解析

评论