这是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。

结合实际讲一个有用的例子来加深印象:

有的同学可能已经学习了这样的一条PCB布线规则:在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长。这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。

如OC或OD电路要控制一个电平就是通过它这个开关的通断来实现的。

有在上拉电阻的情况下,开关接通,得低电平;开关切断,得高电平。这样,为了防止电路失控的情况下仍然是有效电平,那么当然是低电平有效才更“保险”了。结构上,象OC电路那样,由于集电极更难击穿,所以,也更不容易损坏。

对于其它图腾柱输出的电路,虽然0和1都有同样的风险,但应用中还是有人愿意加一个上拉电阻,以取得类似OC或OD输出的效果。至于为什么不采用下拉电阻而用上拉电阻,大家也可以分析一下。

另一个方面是OC或OD输出的电路,使用上拉电阻后具有节能的效果。因为关断后它是具有获得高电平时的电流几乎为0。

-

单片机

+关注

关注

6044文章

44632浏览量

639401 -

上拉电阻

+关注

关注

5文章

363浏览量

30756 -

低电平

+关注

关注

1文章

117浏览量

13362

原文标题:为什么单片机管脚设计成低电平才有效?

文章出处:【微信号:mcugeek,微信公众号:MCU开发加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

51单片机中断用法实例解析

C语言单片机等待询问_51单片机编程实例大全(下部)

单片机IO口低电平不为0V

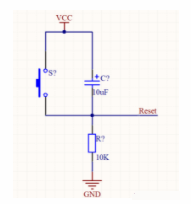

电子设计(4)高电平、低电平复位电路

为什么单片机管脚设计成低电平才有效

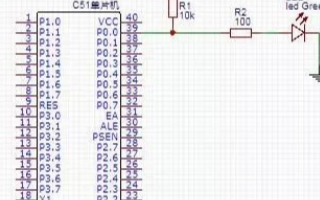

利用单片机点亮流水灯实例解析

基于单片机管脚设计成低电平的原因以及实例解析

基于单片机管脚设计成低电平的原因以及实例解析

评论