一、微封装技术的发展

随着航空航天系统对于小型化、低功耗、高性能、高可靠性的要求,传统PCB板上系统(SOB)的设计方案的缺点越来越明显。由于芯片、模块的体积和功耗的限制,PCB板尺寸和功耗不能无限制减小。单个芯片的封装尺寸通常在mm到cm量级,但PCB板上的走线长度通常在1cm~50cm量级,过大的封装和走线造成损耗大、寄生参数多,限制了系统性能的提升。同时由于系统功能复杂,使用大量分立器件造成系统故障点多,整机可靠性降低。

为了解决传统板上系统设计的弊端,航空航天领域也逐渐开始采用在通信、计算机及消费类电子广泛使用的微封装、微组装技术,来提高系统的集成度和可靠性。

典型的微封装、微组装技术有SoC、MCM、SiP、SoP等。

SoC技术最早出现于上世纪80年代,用于把多个功能模块集成到一个晶片上,主要用于通信、计算机、网络等高性能领域,典型的如NVIDIA的Tegra, Freescale的Vybrid以及下图所示Intel的Core系列多核处理器等。SOC的特点是把相同工艺的多个功能模块集成到1个单一晶片上,系统性能高、功耗低,是商用一体化芯片解决方案的首选. 其基本要求是要在同种半导体材料上实现, 而对于综合了GaAs、GaN及锗硅工艺的航空航天领域,则较难以实现。

MCM也是上世纪80年代出现的一种封装技术,其特点是把多个芯片甚至裸Die通过金丝键合线以及基底材料集成到一个封装里。MCM封装后的模块尺寸和成本可以降低很多,同时由于模块内的各个芯片不需要单独封装,且芯片间走线更短,所以可以提供更好的传输性能。另外由于集成度高,容易进行集中的屏蔽和保护,所以比起采用分立器件系统可靠性更高。 MCM技术可以把不同工艺的晶片集成在一个封装里,因此使用非常灵活,可以构建模拟、数字、射频以及电阻、电容等无源器件的混合系统。下图分别是IBM和波音公司开发的两款MCM芯片。

图1:IBM Power5处理器和Boeing公司的MCM控制芯片

SiP是上世纪90年代出现的封装技术,可以认为是MCM技术的升级版。SiP封装技术除了像MCM一样可以进行多个不同工艺晶片的平面封装以外,还可以进行裸Die或者封装的立体3D堆叠,进一步提高了封装密度。目前广泛应用于手机、PAD等便携式消费电子设备里,典型的如Apple公司在iWatch里的核心模块以及相控阵雷达里使用的T/R模块等。

图2:iWatch里使用的SiP模块及射频T/R SiP模块

SoP是本世纪初出现的一种封装技术,可以认为是SiP技术的进一步升级。除了像SiP一样可以完成多种晶片、无源器件的3D堆叠和封装以外,还采用了薄膜技术和纳米材料把一些常用的无源器件如电阻、电容、滤波器、波导、耦合器、天线甚至生物传感器等直接集成到封装基底上。这使得基底上的走线长度从mm量级减小到了um甚至nm量级,进一步提高了系统性能和集成度。下图是一个SoP芯片应用的例子。

图3:典型的SoP系统

由此可见,SoC、MCM、SiP、SoP等技术各有自己的特点和应用领域。为了实现航天电子系统的小型化并提高可靠性,MCM和SIP是特别适合系统级小型化设计可以采用的微封装、微组装技术,同时可以重点关注SOP技术的发展并做相应的技术储备。

二、微封装技术的挑战

微封装、微组装技术可以带来显著的集成度和系统性能的提高,但是由于采用和传统的板级系统设计完全不同的技术和工艺,其设计和测试难度很大。尤其对于空间等高辐射、高可靠性应用的场合来说,如何进行可靠性设计以及全面有效的功能、性能验证尤其重要。在空间应用中采用微封装技术的主要难点和挑战体现在以下几个方面。

1. 微封装材料、互连技术的设计和仿真:在空间应用中,辐射、温度、振动等工作环境恶劣,一颗卫星的工作周期可能要20年以上并几乎不可维修,使得其对于可靠性的要求很高,因此封装材料和互连工艺的选择至关重要。以基底材料来说,可能有塑料、树脂、铝、陶瓷等多种选择;以电介质材料来说,适合空间等恶劣环境应用BCB(苯并环丁烯)材料、Riston和Kapton材料等;以互连技术来说,可能有球状焊接、金丝键合、硅穿孔(TSV)等方式,而以主流的金丝键合方式来说又存在着多种的键合线结构。因此,对各种材料特性、加工工艺、走线拓扑进行仿真并确定设计方案,同时确保满足空间环境的电、热和机械性能要求,就成为系统设计的难点和关键技术。

2. 关键芯片的功能和性能验证:微封装模块是把不同功能的芯片甚至裸Die封装在一起并通过金丝键合在一起,整个模块内部可能会有几个甚至几十个子功能模块的芯片。由于航天级芯片的成本都非常高,如果封装完后才发现其中某个芯片有问题,会造成整个模块的报废,因此封装前芯片功能和性能的检测对于提高最终的成品率和降低成本至关重要。

3. 微封装模块的系统功能和性能测试:大部分微封装模块是把两个或多个功能模块如模拟、射频、数字、电源等用金属或陶瓷材料封装在一起。当各个功能模块被封装在一起以后,需要对微封装模块的功能和性能进行全面的测试,以确保封装后的模块功能和性能满足设计要求。对高可靠性应用场合,还需要按照实际工作要求进行环境老化试验和筛选,以确保在未来几年甚至几十年内能够可靠有效地工作,这就使得微封装模块的系统功能和性能测试至关重要。

三、关键功能模块表征

1. 高速并串转换芯片的功能和性能测试

并行总线是数字电路里最早也是最普遍采用的总线结构。为了解决并行总线占用尺寸过大且对布线等长要求过于苛刻的问题,随着芯片技术的发展和速度的提升,越来越多的数字接口开始采用串行总线。

为了便于把多路并行的数字信号用尽可能少的电缆传输出去,并提供更好的噪声抑制能力及传输距离,一般会通过高速TRANSCEIVER芯片把多路并行数据复用在一起并通过高速低压差分信号进行传输。

数据速率提高以后,对于阻抗匹配、线路损耗和抖动的要求就更高,稍不注意就很容易产生信号质量的问题。对于高速串行收发芯片的测试,主要涉及以下几个方面:

* 高速串行芯片发送端信号质量测试: 包括输出幅度、眼图、抖动、上升时间、下降时间等;

* 高速串行芯片接收端抖动容限、噪声容限、灵敏度、系统误码率测试,用于验证系统实际传输的误码率、接收容限等。

* 芯片工作电压、电流、功耗等

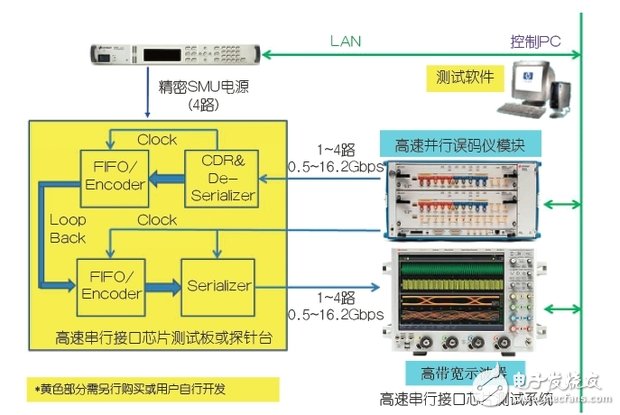

以下是整个高速收发芯片传输系统的测试平台构成。

图4

测试中使用高性能的多通道误码仪产生多路串行激励信号和时钟送给被测芯片,数据经环回后回送误码仪进行误码率统计或者接高带宽示波器进行信号质量分析。误码率测试过程中可以在信号上加入随机抖动、确定性抖动、共模噪声、差模噪声、ISI码间干扰能影响以验证接收端对于恶劣信号的容忍能力。

2. 卫星相机成像的电子系统微封装模块整体测试方案

其测试系统应包含以下功能。

* CCD信号的模拟:应能模拟CCD器件输出的模拟信号,并能灵活增加噪声以验证被测模块提取和恢复图像数据的能力。

* 高速输出数据的采集和分析:应能采集捕获被测模块处理后的高速数据输出,并能够根据数据结构提取数据里的图像信息,以验证模块在不同工作状态下的功能和性能。

* 模拟输出信号的分析:对CCD驱动时钟、电机/快门等驱动信号的幅度、频率、占空比、脉冲宽度等进行测量和分析。

* 接口控制电路:应能控制模块进入正常工作状态。

* 模块功耗和电源抗扰度测试:应能对模块在不同工作状态下的电压、电流、功耗做记录,并能够模拟电压跌落、电源纹波、上下电时序变化等异常情况,验证模块在极端情况下的工作状态

图5:CCD相机SiP模块测试系统

测试中用高性能的AWG任意波形发生模块模拟产生CCD输出的视频模拟信号,经被测模块采集和处理后以高速数字形式输出。如果是并行数据捕获高速并行数据,可以用高速逻辑分析仪模块捕获分析;如果是多路高速串行数据,可以用并行误码仪的输入端进行时钟恢复并捕获数据。测试中要求AWG模块的信噪比、动态范围、带宽等指标能满足系统信噪比测试要求,可以灵活添加噪声等干扰因素,并有足够深的内存以产生整视频帧的信号。逻辑分析仪应有足够高的状态采样速率和内存深度,误码仪应有多路串行数据输入能力、时钟恢复能力、高速信号均衡能力以及足够的内存深度。

-

SiP

+关注

关注

5文章

505浏览量

105364 -

卫星

+关注

关注

18文章

1716浏览量

67104

发布评论请先 登录

相关推荐

微封装技术对减轻卫星载荷的重要性

微封装技术对减轻卫星载荷的重要性

评论