斯坦福大学的研究人员已经证明,由单层二硫化钼(MoS2)制成的场效应晶体管可以成功驱动电阻式随机存取存储器。近日在IEEE国际电子设备会议上报告的结果代表了在单片3D集成芯片中将存储器与逻辑混合的关键里程碑。

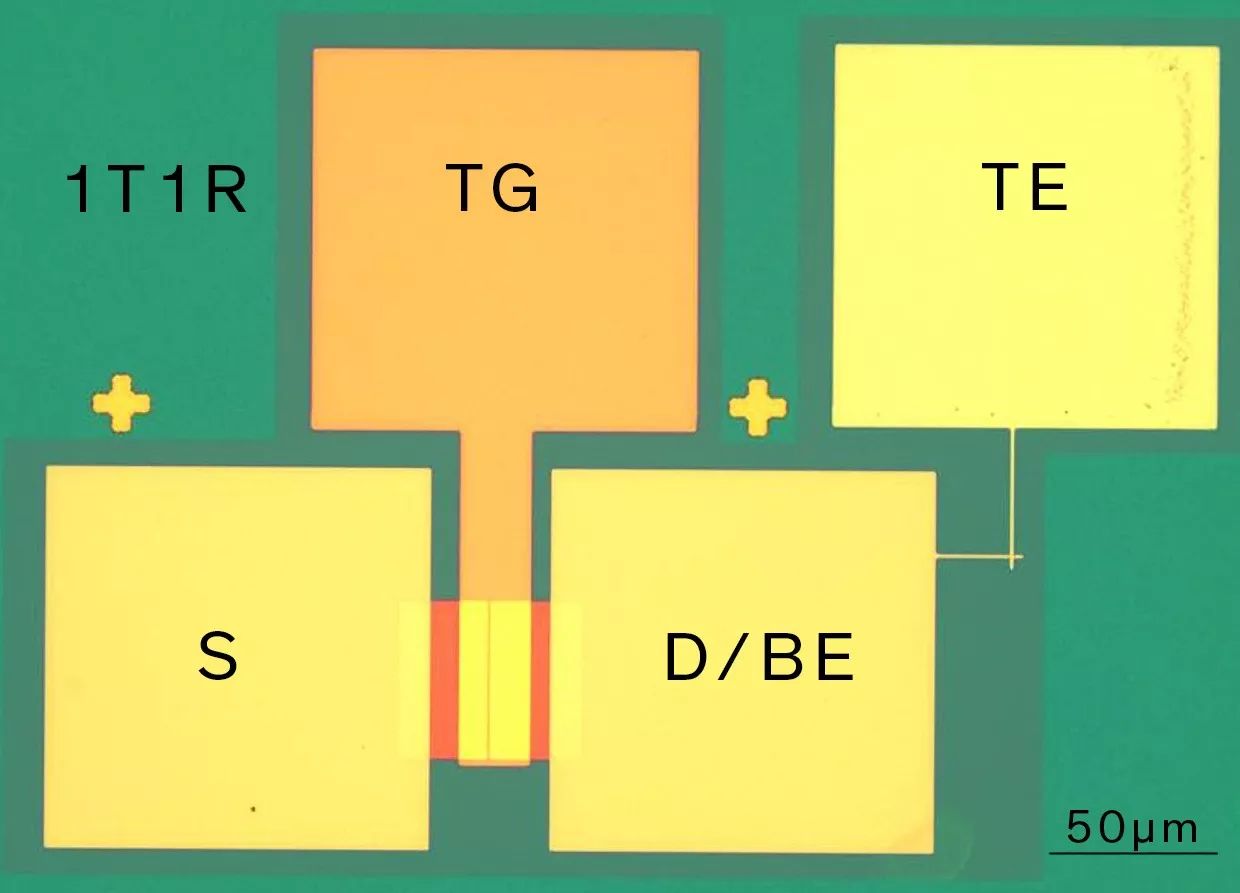

斯坦福研究人员开发的芯片被称为“单晶体管单阻变存储器”(1T1R)单元。这种1T1R存储单元相对于含有阻变存储器但没有晶体管的存储单元,能够提供极大好处。

没有晶体管的情况下,阻变存储芯片中的所有存储单元都被连接到不同的线路,从而使存储阵列成为一个大电阻网络。当选择某个存储单元读取其内容时,电流不仅来自所选的存储单元,还来自存储阵列中所有未选存储单元的泄漏电流。由于这些泄漏电流,被选存储单元上的电压将小于施加电压。

1T1R存储单元的好处在于,可以通过晶体管的开启和关闭,将目标存储单元同其他存储单元隔离,从而抑制泄漏电流。“虽然硅场效应晶体管也可以用于1T1R存储单元,但单层二硫化钼的优点在于,其转移工艺可以在较低温度下进行,从而便于在单块芯片中实现存储层和逻辑层的相互三维堆叠配置。” 斯坦福大学的博士后研究员Rui Yang说。他是H.-S内部研究的主要作者,和Philip Wong都在Nanoelectronics实验室。

Yang补充说,“二硫化钼场效应晶体管的电流沟道只有原子厚度,纳米级的中间层过孔可以成为连接芯片不同层的通道。这使芯片中的更多部分能够更加有效访问存储器。”

在一般操作中,阻变存储器将数据存储为电阻阻值。对于采用1T1R存储单元的阻变存储器,当存储单元中的场效应晶体管(本例中是基于二硫化钼的场效应晶体管)开启时,存储单元就处于写入模式。此时,其他未被选中单元的晶体管将处于关闭状态,电压将被施加在所选阻变存储器的顶部电极和二硫化钼晶体管的源电极上。

晶体管与阻变存储器串联在一起。当阻变存储器从高阻状态转变为低阻状态时,阻变存储器的顶部电极就处于高电平状态,场效应管的源电极接地。晶体管驱动电流通过阻变存储器并控制电流,当电压周期性变化时,进而调控电阻值。目前,阻变存储器的制取可以利用CMOS兼容的材料实现。

然而,表示,目前工业上还没有准备在同等程度上制造二维材料。他说:“我们需要找到可靠的方法,以在晶片上生长和转移二维材料,并在单片三维堆叠架构上实现二维晶体管与阻变存储器的集成。”Yang说。

除了在晶片上生长和转移二维材料以外,这些器件仍有许多问题需要克服。杨认为,他们需要使器件更小,使1T1R存储阵列更大,并进一步提高器件的一致性。他相信该技术极具发展前景。二硫化钼和阻变存储器不仅使平面内电路规模的横向扩展成为可能,而且还提供了通过三维堆叠方式使电路规模在垂直方向上实现扩展的可能性。Yang补充道:“为了实现这一目标,我们计划在三维电路中制造多个存储层和逻辑层,并使其具备存储器内计算的能力。”

-

存储器

+关注

关注

38文章

7552浏览量

164808 -

晶体管

+关注

关注

77文章

9829浏览量

139396

原文标题:斯坦福大学开发单晶体管单阻变存储器单元

文章出处:【微信号:IEEE_China,微信公众号:IEEE电气电子工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

斯坦福大学开发了单晶体管单阻变存储器单元 可抑制泄漏电流

斯坦福大学开发了单晶体管单阻变存储器单元 可抑制泄漏电流

评论